随着物联网技术的兴起,现在的电子产品搭载无线通讯功能是越来越普遍了,而无线通讯技术是依赖于PCB上的射频电路来实现的,并且需要专业的设计和仿真分析工具。现将模组射频电路PCB 设计分享给大家。

走线原则

对于自身没有连接器的模块,需通过 RF 走线和天线馈点或者连接器连接,所以 RF 线推荐走微带线, 越短越好,差损控制在 0.2dB 以内,并且阻抗控制在 50Ω。

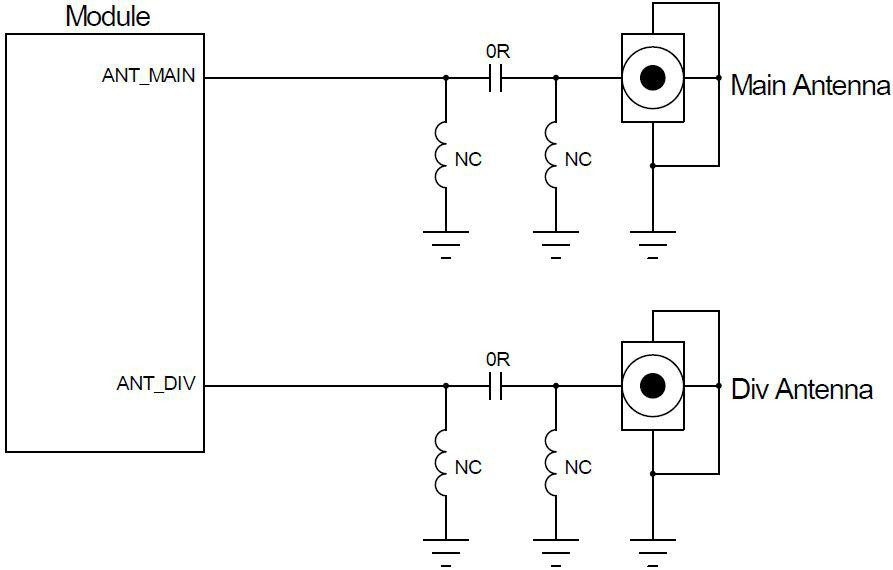

在模块和天线连接器(或馈点)之间预留一个π型电路(两个并行器件接地脚要直接接到主地)供天线调试。

在 PCB 走线时,此信号走线控制 50Ω。产品的射频性能与此走线密切相关。在 PCB 板上影响此走线阻抗的因素如下:

l 走线的宽度和厚度

l 介质介电常数和厚度

l 焊盘的厚度

l 与地线的距离

l 附近的走线

阻抗设计

两个天线接口的 RF 信号线阻抗都需要控制 50Ω。在实际应用中根据 PCB 的其他参数如参考层厚度、层数和叠层等都会影响到 RF 的走线方式,不同的情况参考 GND 层不一样,走线差距也将很大。

3W 原则

多层板设计天线 RF 信号在 PCB 上走线时,首先考虑的是满足基本的“3W 原则”。为了减少线间串扰,应保证线间距足够大,如果线中心距不少 3 倍线宽时,则可保持 70%的线间电场不互相干扰,称为“3W 原则”。

3W 原则示意图

射频 PCB Layout 部分

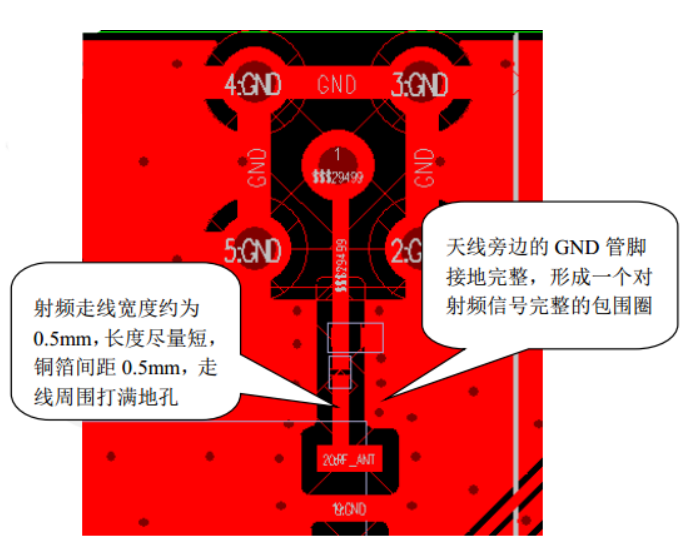

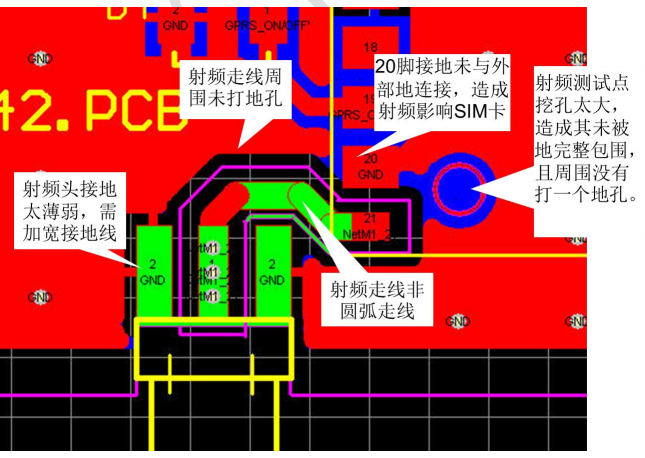

l 射频走线尽量做50欧姆阻抗,如果无关做到,应将射频走线宽度保持在0.5mm~1mm距地安全距离也要保持在0.5mm~1mm,周围打满地孔

l 射频座子的地建议尽量净空

l 过孔焊盘建议用泪滴结束

射频走线应尽量远离电源,SIM卡,时钟,高速数字信号;保其不对周围器件产生的影响,所以在天线周边建议客户不要放其他元器件,并且 PCB 上的走线尽可能远离 RF 部分。

射频走线应尽量短,遇弯需走蛇形线或圆弧,周围打地孔;

两层板阻抗设计

两层板阻抗设计

因为大部分客户多有用双面板进行设计,所以针对两层板典型的 1.6mm,1.0mm 厚度 PCB 设计做实例说明:

案例一:PCB 板厚 1.6mm

考虑到 PCB 板厚的影响,要完全符合 3W 原则很难实现,既要保证 50Ω走线,又要确

射频走线过长时,模块测和天线测建议预留匹配电路

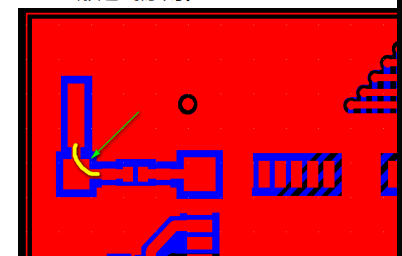

如果板上空间富裕,优先通过布局实现RF走线的短和直,如果布局空间不允许,需要拐角走线,一定避免直角或45°拐角走线,要走圆弧走线,如果实在要走直角了,可以通过放置元件通过元件的摆位的方式来替代走线来做90°角的转折,这样可以最大化避免阻抗突变造成的信号反射影响。

两层板阻抗设计

因为大部分客户多有用双面板进行设计,所以针对两层板典型的 1.6mm,1.0mm 厚度 PCB 设计做实例说明:

案例一:PCB 板厚 1.6mm

考虑到 PCB 板厚的影响,要完全符合 3W 原则很难实现,既要保证 50Ω走线,又要确保其不对周围器件产生的影响,所以在天线周边建议客户不要放其他元器件,并且 PCB 上的走线尽可能远离 RF 部分。

经过我们大量实际验证,以下设计可以保证 RF 阻抗控制在 50Ω左右,并且受到影响最小:

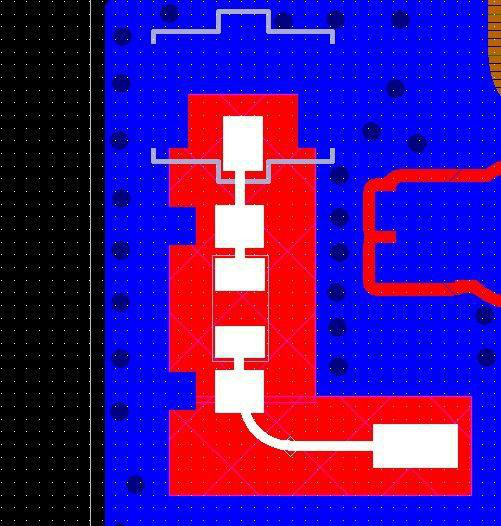

RF 线宽 43mil,离旁边的地(蓝色)的距离是 8mil,射频走线的正下方是 RF 线参考层,通常为完整的地(红色)。 RF 线四周需完整的地保护,并且沿着走线方向尽量多打地孔。在射频走线及其参考地周围,不建议有其他任何走线或器件。

50Ω阻抗的理论计算:

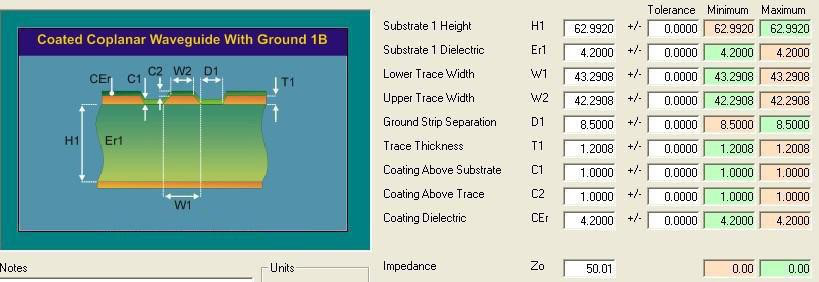

阻抗计算工具示意图(单位 mil)

Er1,T1,C1,C2,CEr 参数一般由 PCB 板厂确认,每个 PCB 板厂的工艺和材质有略微差异,需要和 PCB 板厂确认。

H1 为 PCB 厚度,W1 为线宽,D1 为线到旁边 GND 的距离。 实际生产中要考虑误差。案例二 PCB 板厚 1.0mm PCB 板厚 1.0mm 时,RF 在 PCB 上线宽是 35mil,线到旁边的 GND 的间距是 8mil。

四层板阻抗设计

四层板,板厚 1.0mm,RF 线走在表层 Lay1,参考 Lay2(GND 层)。不同 PCB 板厂的叠层会有不同,以下图的 4 层板的叠层为例:

层板叠层厚度示意图

Lay 1 到 Lay 2 的厚度是 65um,RF 走线 4mil,RF 到两边 GND 的距离大于 3 倍的 RF线宽。Lay 1 蓝色,红色是 Lay 2 层,高亮部分是 RF 线。

RF 走线示意图

50Ω阻抗的理论计算:

D1 的值在大于 3 倍的 W1 以后,对阻抗的影响就很微弱。

四层板阻 TOP 层走线抗计算示意图

以上是我们在模组开发项目中硬件电源设计过程中的一些经验累积,希望您在项目开发过程中少走弯路,顺利完成开发任务。最后介绍我们奇迹物联,我们产品涵盖了基于eSIM技术的2G,4G,NB模组,并且还为客户提供模组相关的硬件设计资料和评审服务,帮助客户快速完成项目开发,迅速抢占物联网市场。

文章奖励内容:

本文Candy奖励:GSMA 2019 《eSIM在中国-未来之路》产业报告

获得方式:扫码关注,留言“eSIM在中国”

——end----

我要赚赏金

我要赚赏金