PLD(可编程逻辑器件)以其操作灵活、使用方便、开发迅速、投资风险低的特点,很快发展起来,并越来越受人们的瞩目。PLD是可以由用户在工作现场编程的逻辑器件,它从简单的PAL、GAL,已发展到CPLD、EPLD、FPGA和FLEX系列。他们都具有体系结构和逻辑单元灵活、集成度高以及适用范围广等特点。

同以往的PAL、GAL等相比较,FPGA/CPLD的规模比较大,适合于时序、组合等逻辑电路等场合应用。可编程逻辑器件易学、易用,简化了系统设计,缩小了系统规模,提高了系统的可靠性。一个器件的可用门已达数万门,引脚间延时仅几ns,而且仍在朝着高密度、高速度的方向迅速发展。

计算机总线是计算机各部件之间进行信息传输的公共通道。在当今的微型机中主要采用的是PCI总线,ISA、EISA总线正逐步被淘汰。所以对硬件设计人员来说,掌握PCI总线板卡的开发技术是非常重要的。板卡的设计方法通常有这么几种:一是做ASIC,开发周期长;另一种是在专用接口芯片下开发,但使用不是很灵活,系统规模大;目前最新的方法是用PLD来开发设计。

在进行CPLD设计时,使用的软件是Altera的MAX+PLUSII。Altera的MAX+PLUSII开发系统是一个完全集成化、易学易用的、与结构无关的可编程逻辑设计环境,它使通用系列设计者能方便的进行设计输入、快速处理和器件编程,使用此软件的设计方法是很灵活的,可以采用硬件描述语言(PLD)、电路图,甚至是时序图。根据不同的情况可以采用不同的方法,在一个设计中也可以采用多种方法。下面以一个简单的PCI从设备设计为例,说明设计思想与过程。

在本例中,设计的PCI卡作为从设备使用,可以实现即插即用功能,卡上有1MB的存储器可供使用。在PCI即插即用板卡的设计中,核心设计有两部分:时序控制和配置空间。时序控制保证了板卡能按正常的PCI时序工作,配置空间部分保证了板卡的即插即用功能。

在本例中,这两部分都由AHDL语言来实现的(AHDL语言是Altera公司专门为其芯片设计开发的一种硬件描述语言)。在时序控制程序中采用状态机模型来实现不同时序的转换,采用这种方式既节省资源,程序也简单易懂。

本例中的状态机共使用了七种状态,分别对应空闲、存储器读写的判断、配置读写的判断、读、写、过渡周期、总线忙周期的时序。板卡接到复位信号后,对系统进行复位,然后转入空闲状态。在空闲状态中采样总线,并根据总线的变化来决定下一个时钟上升沿后,状态机转入何种状态。这些时序和程序中用到的信号都是基本且必须的。在进行开发时可以根据需要增添必要的状态和信号。程序描述如下:

subdesignstatesmachine

(clk,rst,frame,ad[31..0],cbe[3..0],idsel,irdy,mem_bar[12..0]:input;

devsel,trdy,cfg_rd,cfg_wr,mem_rd,mem_wr:output;

cfg_addr[5..0],mem_addr[16..0]:output;)

//以上定义了状态机模块的输入输出引脚

VARIABLE

pci_state:MACHINE

WITHSTATES(idle,cmp_cfg,cmp_addr,read,write,turn_ar,bus_busy);

//定义状态机变量,共有七个状态空闲状态idle,配置空间操作cmp_cfg,比较地址cmp_addr,读状态read,写状态write,过渡周期状态turn_ar,总线忙状态bus_busy。通过状态机的不同状态实现时序的转换,在每个状态中实现不同的时序周期。

BEGIN

初始化:对内部信号和各个输入输出引脚进行初始化,设定它们的连接关系。

IFrst==b“0”THEN//判断是否复位

实现复位的时序操作。

ELSE

CASEpci_stateIS

WHENidle=》//空闲状态

在此状态中,每个时钟周期判断frame和idsel信号的变化,一旦发现frame被置为有效,就根据idsel信号判断下一状态转入对配置空间操作的cmp_cfg或是比较地址对存储器操作的cmp_addr

WHENcmp_cfg=》//对配置空间操作的状态

在此状态中根据地址线的低两位判断是否是对配置空间的操作,若不是转入总线忙状态bus_busy;若是则根据cbe的信号是A或B来判断是读还是写,转入相应的状态read,write。

WHENcmp_addr=》//地址比较状态

在此状态中判断要读写地址的高位与配置空间中分配的地址是否相同,若不同转入总线忙状态bus_busy;若相同则根据cbe的信号是6或7来判断是读还是写,转入相应的状态read,write。

WHENread=》//读状态

在此状态中,根据cbe的值判断是配置读还是存储读,然后控制输出信号mem_rd,cfg_rd,trdy,devsel产生相应的读时序,同时在此周期中判断frame,irdy信号,若irdy变低并且frame变高,则读状态结束,转入turn_ar状态.

WHENwrite=》//写状态

在此状态中,根据cbe的值判断是配置写还是存储写,然后控制输出信号mem_wr,cfg_wr,trdy,devsel产生相应的写时序,同时在此周期中判断frame,irdy信号,若irdy变低并且frame变高,则写状态结束,转入turn_ar状态。

WHENturn_ar=》//信号的过渡周期状态

按照PCI的总线规范,S/T/S信号,从有效变为浮空之前必须保证使其具有至少一个时钟周期的高电平状态,此状态中,将所有的S/T/S信号置为高。

WHENbus_busy=》//总线忙状态

总线不对本卡操作,因此通过对frame信号的判断,来决定何时脱离本状态。

WHENOTHERS=》

若进入此状态,则应根据需要,马上转入bus_busy或idle

ENDCASE;

ENDIF;

END;

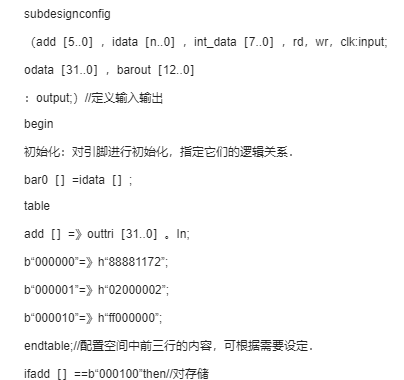

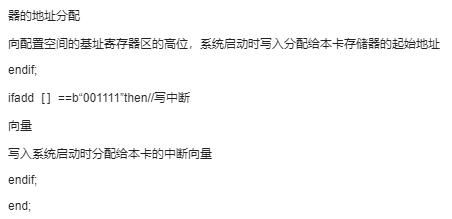

配置空间部分也采用AHDL语言来描述实现,在配置空间中定义PCI卡的功能、内存空间的分配、以及产品号、ID号等.通过对配置空间的定义,才能保证板卡的即插即用功能.描述如下:

两部分都通过软件生成模块,两模块之间的接口部分,可以很容易的通过电路图的连接来实现。两个模块图如图。

使用CPLD技术开发PCI板卡有以下优点:

1、开发周期短、成本低、投资风险小,标准产品无需测试、质量稳定,可实时在线检验。采用CPLD技术设计完成后,可以进行实时的时序仿真。验证改进设计结果,而不需重复的硬件试验。设计通过后写入芯片,通过测试即可投入使用。比使用一些专用的PCI芯片开发要简单,而且省去了其他开发设备,所以成本也较低。比之ASIC开发的周期则要短的多。

2、使用灵活方便。由于开发的板卡是直接在总线的基本规范上进行,没有使用一些专用芯片,因而开发更灵活、自由,受到的限制更少,整个硬件模块的规模也较小,可以将很多自己的算法与技术和PCI合成在一起,做出技术含量更高的产品。

3、有利于知识产权的保护和软件性能的提高。利用这项技术可以将自己的的算法、技术和一些软件做成硬件固化到卡上,既提高了运行速度,也使盗版者难以复制。

本文结合一个实例给出了在PCI总线上利用CPLD技术设计各种板卡的设计方案,简单实用,有很高的应用价值。

山东大学数学院•作者:周庆瑞,牛超星

我要赚赏金

我要赚赏金