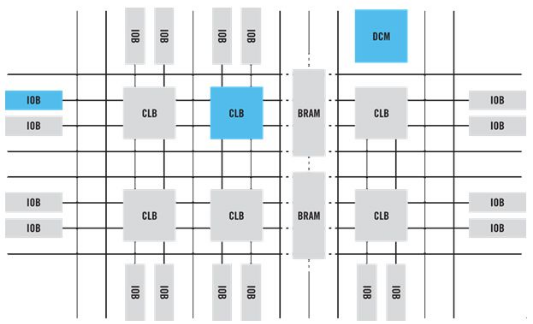

FPGA架构主要包括可配置逻辑块CLB(Configurable Logic Block)、输入输出块IOB(Input Output Block)、内部连线(Interconnect)和其它内嵌单元四个部分。CLB是FPGA的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个CLB都包含一个由4或6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

FPGA可支持许多种I/O标准,因而可以为系统设计提供理想的接口桥接。FPGA 内的I/O按bank分组,每个bank能独立支持不同的I/O标准。目前最先进的FPGA提供了十多个I/O bank,能够提供灵活的I/O支持。

CLB 提供了逻辑性能,灵活的互连布线则负责在CLB和I/O之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低skew布线(全局性专用布线资源)。一般,各厂家设计软件会将互连布线任务隐藏起来,用户根本看不到,从而大幅降低了设计复杂性。

内嵌硬核单元包括RAM、DSP、DCM(数字时钟管理模块)及其它特定接口硬核等,FPGA器件内部结构如下示意图。

一般来说,器件型号数字越大,表示器件能提供的逻辑资源规模越大。在FPGA器件选型时,用户需要对照此表格,根据业务对逻辑资源(CLB)、内部BlockRAM、接口(高速Serdes对数)、数字信号处理(DSP硬核数)以及今后扩展等多方面的需求,综合考虑项目最合适的逻辑器件。

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的开发流程一般如下图所示,包括功能定义/器件选型、设计输入、功能仿真、逻辑综合、布局布线与实现、编程调试等主要步骤。

1、功能定义/器件选型:在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。

2、 设计输入:设计输入指使用硬件描述语言将所设计的系统或电路用代码表述出来。最常用的硬件描述语言是Verilog HDL。

3、 功能仿真:功能仿真指在逻辑综合之前对用户所设计的电路进行逻辑功能验证。仿真前,需要搭建好测试平台并准备好测试激励,仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用仿真工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS等软件。

4、 逻辑综合:所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。为了能转换成标准的门级结构网表,HDL程序的编写必须符合特定综合器所要求的风格。常用的综合工具有Synplicity公司的Synplify/Synplify Pro软件以及各个FPGA厂家自己推出的综合开发工具。

5、布局布线与实现:布局布线可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告);实现是将综合生成的逻辑网表配置到具体的FPGA芯片上。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

6、编程调试:设计的最后一步就是编程调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generaon),将编程数据加载到FPGA芯片中;之后便可进行上板测试。最后将FPGA文件(如.bit文件)从电脑下载到单板上的FPGA芯片中。

我要赚赏金

我要赚赏金