来源:FPGA技术江湖阿Q

今天给各位大侠带来一篇项目开发经验分享“基于JESD204B的LMK04821芯片项目开发”,这是本人实打实的项目开发经验,希望可以给有需要的大侠提供一些参考学习作用。

- 支持JESD204B;

- 超低的时钟抖动和噪声;

- 能够同时输出14路差分时钟:

<2>. 最大输出频率可以达到3.1GHz;

- 双PLL结构;

- PLL2的VCO分频系数为1-32;

- 输出时钟精确的数字延时、模拟延时、以及动态延时;

- 多工作模式:双PLL、单PLL以及时钟分发模式;

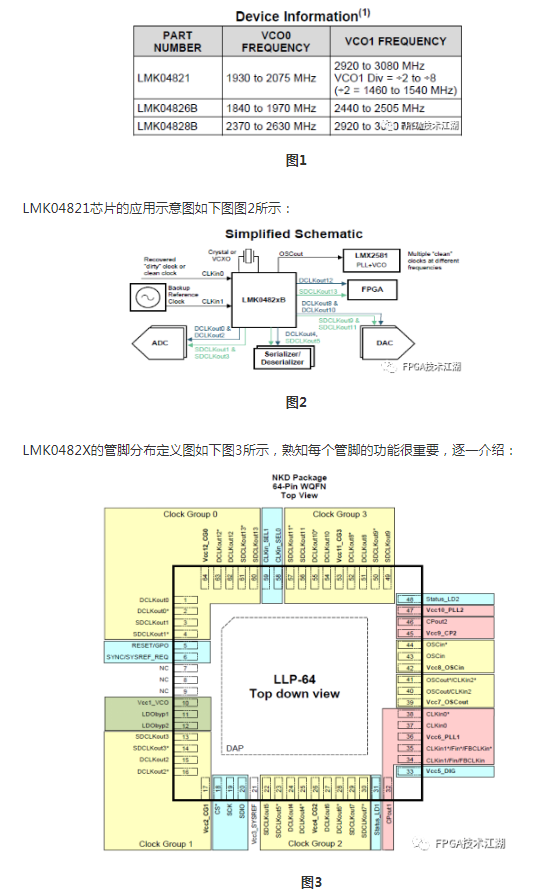

LMK0482X系列的这三款芯片不同之处在于支持不同的VCO,如下图图1所示:

PIN3、4:第1路SYSREF/Device CLK差分输出;

PIN6: 该芯片的时钟同步输入端口或者是连续SYSREF CLK请求输入端口;

PIN10: 电源输入;

PIN12:LDO旁路电容,外接0.1uf到地;

PIN15、16:第2路Device CLK差分输出;

PIN18:芯片的SPI配置CS信号;

PIN20:芯片的SPI配置SDIO信号;

PIN22、23:第5路SYSREF/Device CLK差分输出;

PIN26:电源输入;

PIN29、30:第7路SYSREF/Device CLK差分输出;

PIN32:PLL1的电荷泵输出;

PIN34、35:PLL1的参考时钟输入1、零延迟模式下的外部反馈时钟输入、外部VCO输入;

PIN37、38:PLL1的参考时钟输入0;

PIN40、41:反馈到PLL1,参考输入到PLL2。AC耦合;

PIN43、44:PLL2的参考时钟输入、PLL1的反馈时钟输入;

PIN46:PLL2的电荷泵输出;

PIN48:可编程的状态监测I/O管脚;

PIN51、52:第8路Device CLK差分输出;

PIN54、55:第10路Device CLK差分输出;

PIN58:可编程的状态监测I/O管脚;

PIN60、61:第13路SYSREF/Device CLK差分输出;

PIN64:电源输入;

2.1 硬件电路检查

2.2 寄存器配置

2.2.1 写操作时,CS信号为低电平时,SDIO的数据在SCK上升沿写进芯片,写数据格式为1bit的读写控制位+2bit的0+13bit地址+8bit数据。

时序图如下图6所示:

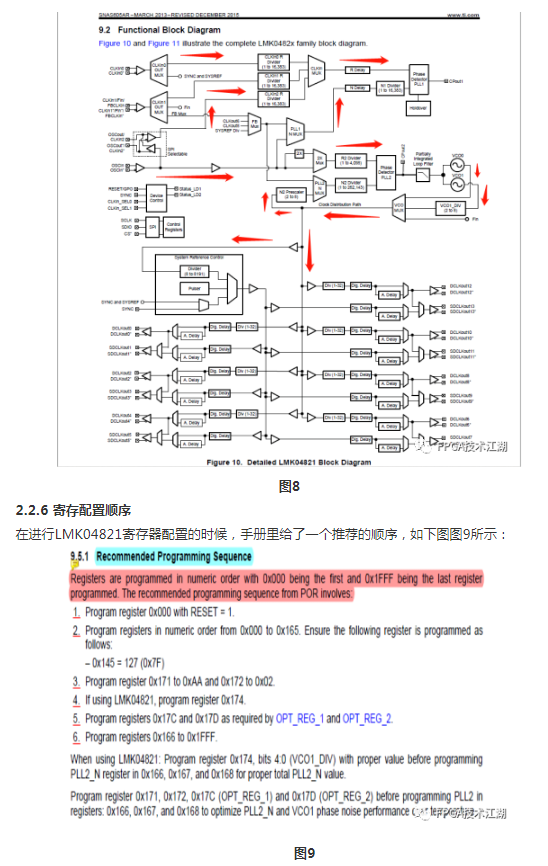

2.2.4 LMK04821的双PLL级联系统的介绍:

- LMK0482X系列芯片的双PLL结构保证了在很宽的输出频率范围内还可以输出最低抖动的时钟。第一级PLL(PLL1)被外部的参考时钟驱动,第二级PLL(PLL2)由VCXO或者可调晶振提供高精度、低噪声的二级参考时钟。经过这两级PLL,输出时钟的精度将会大大提高。

- LMK0482X系列芯片共输出7对JESD204B DeviceCLK和7对SYSREF CLK,其中每个Device CLK对应一个SYSREF CLK。对于那些非JESD204B的应用,SYSREF CLK同样可以编程为Device CLK。

- PLL1的输入参考时钟包括管脚CLKin0,CLKin1以及CLKin2,任选一个作为时钟输入即可,选择的规则由配置寄存器参数决定。

- VCXO/Crystal 缓存输出,LMK0482X系列芯片提供OSCout输出,该输出其实就是PLL1的反馈输入,也是PLL2的参考时钟输入,芯片的该功能其实就是为了在其编程之前可以提供一个时钟给控制器工作,控制器编程再配置LMK0482X。OSCout输出可以为LVDS、LVPECL以及LVMOS电平。

- LMK0482X具有频率保持的功能,当外部参考时钟丢失后,输出频率还能保持最小的漂移,直到外部参考时钟恢复。

- 7路Device CLK都可以分别的分频,分频系数为1~32。

- 7路SYSREF CLK统一分频,分频系数为8~8191。

- Device CLK具有延迟的功能,其包括模拟延迟和数字延迟。模拟延迟是以25ps为单位的时钟延迟模块,使用该模块本身也会带来500ps的延时。数字延时范围为4~32 VCO时钟周期,每一个延迟单元的大小为0.5 VCO周期。需要注意的是延迟的功能必须在同步使能后才起作用。

- SYSREF CLK同样具有模拟核数字延迟。模拟延迟的最小单位为150ps。数字延迟的范围为1.5~11VCO,同样每一个延迟单元的大小为0.5 VCO周期。

- 14路时钟的输出不仅在电平标准上可编程,在输出的幅度方面也可编程。

- 要使时钟的数字延时起作用,管脚SYNC必须给一个脉冲,在脉冲的上升沿所有的时钟同步。

- LMK04821提供了几个状态管脚用来供用户监测芯片内部的状态或者作为输入端口来响应用户的需求,具体的功能在寄存器配置说明里介绍。

但是在实际运用中,按照该寄存器配置顺序,时钟输出端并没有正确的时钟输出。实际运用中,将寄存器顺序按照如下顺序进行配置:

2、然后紧接着从0X100~0X145;

4、0X146~0X16E;

注意:在实际应用中,目前为止该寄存器顺序是唯一能够正确产生时钟的顺序,可以参考软件给的寄存器数据,尽量不要改变配置寄存器的顺序。部分寄存器在设计中没有进行配置,比如一些只读寄存器,IC信息相关的寄存器,reback相关的寄存器都没有进行配置,实际操作中无伤大雅,可以不用配置。但是在SPI配置寄存器时,如果要检验寄存器读写是否成功时,可以将这些寄存器进行读操作,确保SPI操作正常。

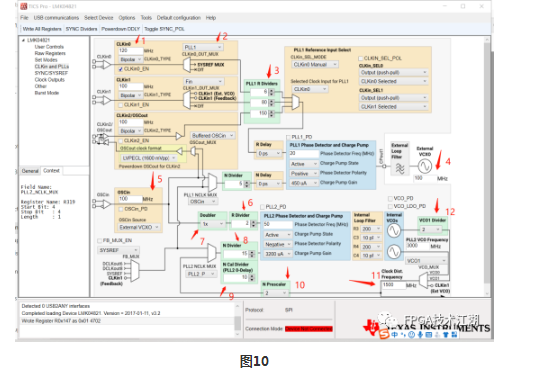

在此之前,确定寄存器配置顺序之后,利用辅助软件TICS Pro软件产生对应的参数,按照6中所示的寄存器顺序进行写操作。软件使用中重要参数的产生以及对应在软件中如何设置见下图图10;

- 标记1选择CLKin0作为参考时钟输入;硬件环境值在CLKin0端有时钟输入;

- 标记2选择PLL1,MUX是可以进行选择的,不同的选择,对应寄存器要配置的数值不同;

- 标记3处选择相应的DIV数值,得到需要的时钟100M;

- 标记4 CPout1直接连接到外部晶振,目的是,当参考时钟丢失时,延时功能可以将PLL1的调谐电压固定在VCXO或者可调谐晶振上,使得在外部参考时钟丢失时,输出的时钟频率的偏移最小,直到外部时钟恢复。

- 标记5 OSCin,PLL1的反馈输入,PLL2的参考时钟输入,实际调试中,发现OSCin如果没有输入,输出端就没有时钟输出,没有CLKin0输入,输出时钟依然正常输出;

- 标记6、7、8、9、10、11、12,这几处都和PLL2 VCO Frequency有关系,手册中显示LMK04821在使用VCO1时,PLL2频率要求在2920~3080MHz之间。

- 超出范围,软件会报红出错。这几处设置其实就是简单的将OSCin的时钟进行先倍频后分频的一个操作;比如,实际中需要DCLKout输出150M、75M时钟,再复合要求范围的情况下,找到一个合适的公倍数,例子中为1500M,这样一来,既能得到150M的DCLKoutX的输出,又能得到75M的时钟输出;

- 标记1,公倍数;

- 标记2,PLL1的反馈输入,PLL2的参考输入,实际运用中,PLL2的参考输入为OSCin;

- 标记3,分频系数,1500M十分频150M;

- 标记4,选择PD,意味着该通道不输出,处于关闭状态;

- 标记5,DCLK输出频率,可在对应位置直接填入想要的数值。注意,最好是公倍数的整数分频后的值,不然,软件会自动产生一个和填入值最相近的数值;

- 标记6,SCLK输出端口,SCLK不能单独分频,7个通道只能统一进行分频;具体设置如下图图12所示:

- Doubler,对应相关寄存器0X162;

- R Divider,对应寄存器0X160、0X161;

- N Divider,对应寄存器0X168;

- VCO,对应寄存器0X138;

- DCLKoutX_DIV, 对应寄存器0X100、0X108、0X110、0X1180、0X120、0X128、0X130;

- SYSREF DIV,对应寄存器0X13A、0X13B;

3.1 时钟输出结果

3.2 待解决问题

其中,DCLK与SCLK如果输出频率相同时,相位差通过观察,有细微偏差,考虑到示波器使用过程中,探头不稳定原因,暂定相位偏差为0;后期有更好的测试方法时,再进行确认。