与处理器不同,FPGA本质上是真正并行的,因此不同的处理操作不必争夺相同的资源。每个独立的处理任务都分配给芯片的专用部分,并且可以自主运行,而不受其他逻辑块的影响。因此,当您添加更多处理时,应用程序一部分的性能不会受到影响。

图1.与基于处理器的系统相比,FPGA的优势之一在于应用逻辑是在硬件电路中实现的,而不是在OS,驱动程序和应用软件之上执行。

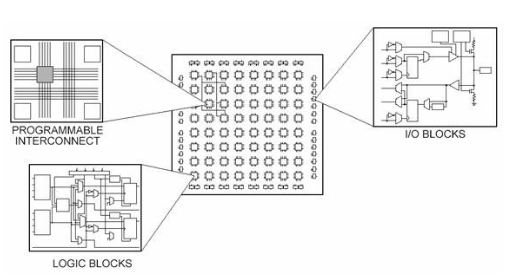

定义FPGA的各个部分每个FPGA芯片都由有限数量的预定义资源组成,这些资源具有可编程的互连,以实现可重新配置的数字电路和I / O块,以允许该电路访问外界。

图2. FPGA的不同部分

FPGA资源规范通常包括可配置逻辑块的数量,固定功能逻辑块(例如乘法器)的数量以及存储器资源(例如嵌入式Block RAM)的大小。在许多FPGA规范中,当为特定应用选择和比较FPGA时,这些规范通常是最重要的。

可配置逻辑块(CLB)是FPGA的基本逻辑单元。有时称为切片或逻辑单元,CLB由两个基本组件组成:触发器和查找表(LUT)。各种FPGA系列在触发器和LUT封装在一起的方式上有所不同,因此了解触发器和LUT非常重要。

人字拖

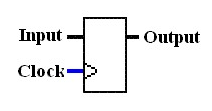

触发器是二进制移位寄存器,用于在FPGA电路内的时钟周期之间同步逻辑并保存逻辑状态。在每个时钟沿,触发器会在其输入上锁存1或0(TRUE或FALSE)值,并将该值保持恒定,直到下一个时钟沿为止。

图3.触发器符号

触发器是二进制移位寄存器,用于在FPGA电路内的时钟周期之间同步逻辑并保存逻辑状态。在每个时钟沿,触发器会在其输入上锁存1或0(TRUE或FALSE)值,并将该值保持恒定,直到下一个时钟沿为止。

查找表(LUT)

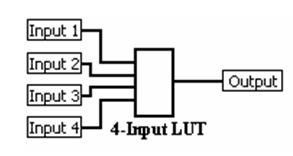

图4.四输入LUT

CLB中的许多逻辑都是使用少量LUT形式的RAM来实现的。很容易假设FPGA中的系统门数是指特定芯片中的NAND门和NOR门的数量。但是,实际上,所有组合逻辑(AND,OR,NAND,XOR等)都被实现为LUT存储器中的真值表。真值表是每个输入组合的预定义输出列表。

这是数字逻辑课的快速入门。

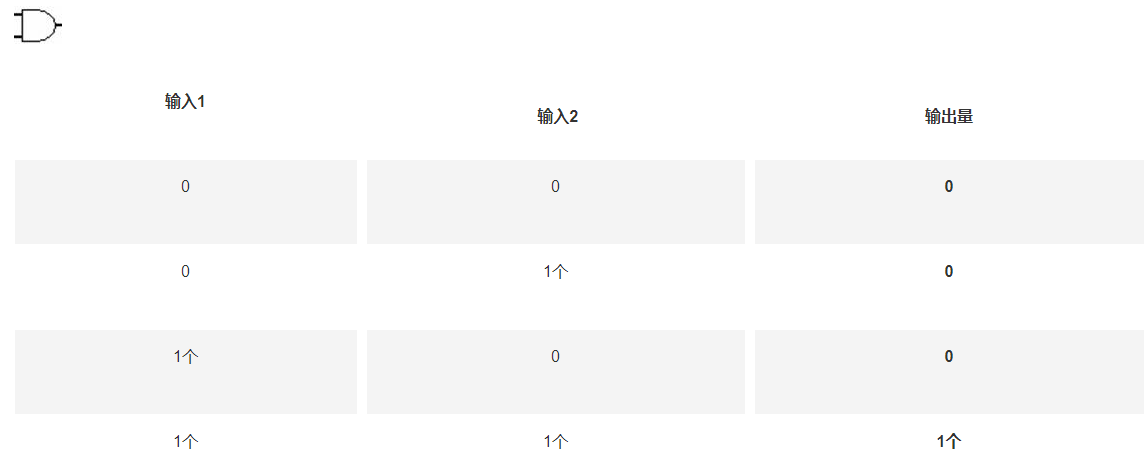

例如,布尔AND操作如图5所示:

图5. NI LabVIEW布尔与运算

表2列出了与运算的两个输入对应的真值表。

表1.布尔“与”运算的真值表

乘法器和DSP Slice

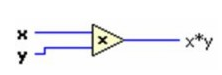

图6. NI LabVIEW乘函数

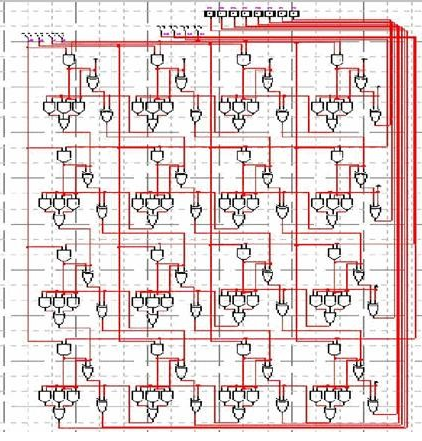

将两个数字相乘的看似简单的任务可能会占用大量资源,并且在数字电路中实现起来非常复杂。为了提供参考框架,图6给出了使用组合逻辑实现4位乘4位乘法器的一种方法的示意图。

图7. 4位乘4位乘法器的示意图

现在想象一下将两个32位数字相乘,一次乘以2,000次运算。因此,FPGA预先构建了乘法器电路,以节省数学和信号处理应用中的LUT和触发器使用。

许多信号处理算法都涉及保持连续的总数被相乘,因此,诸如Xilinx Virtex-5 FPGA之类的高性能FPGA已预先构建了乘法器累加电路。这些预构建的处理模块(也称为DSP48 Slice)将25位乘18位乘法器与加法器电路集成在一起。

块RAM

存储器资源是选择FPGA时要考虑的另一个关键指标。用户定义的RAM嵌入整个FPGA芯片,对于存储数据集或在并行任务之间传递值很有用。根据FPGA系列的不同,您可以按16或36 kb的块配置板载RAM。您仍然可以选择使用触发器将数据集实现为数组。但是,大型阵列对于FPGA逻辑资源而言很快变得昂贵。一个100个元素的32位数组可以占用Virtex-II 1000 FPGA中超过30%的触发器,或占不到嵌入式Block RAM的1%。数字信号处理算法通常需要跟踪整个数据块或一个复杂方程式的系数,并且没有板载存储器,

FPGA固有的并行执行功能允许由不同的时钟驱动独立的硬件逻辑。在以不同速率运行的逻辑之间传递数据可能很棘手,板载内存通常用于使用先进先出(FIFO)内存缓冲区来平滑传输。

回到顶部将FPGA设计到系统中尽管FPGA有许多优势,例如速度,可靠性和灵活性,但也存在与FPGA相关的折衷。FPGA没有微处理器体系结构和OS具有的驱动程序生态系统和代码/ IP基础。此外,与操作系统结合的微处理器为文件结构以及与用于许多通常是必不可少的任务(例如将数据记录到磁盘)的外围设备进行通信提供了基础。

结果,在过去的十年中,出现了一种混合架构,有时也称为异构架构,其中微处理器与FPGA配对,然后将FPGA连接到I / O。现代FPGA通常将逻辑门与处理器结合到一个称为片上系统(SoC)的芯片中,以提高计算性能。这种方法利用了这两个目标所提供的好处。

图8. NI提供了整个系列的FPGA支持的设备,包括封装的和板级的,您可以基于结合微处理器和FPGA的理想混合架构,使用LabVIEW进行编程。

美国国家仪器公司(National Instruments)在其支持FPGA的设备中实现了这种功能强大的微处理器加FPGA体系结构。这些设备跨越多种不同的外形尺寸,从坚固到高性能的系统,都基于相同的体系结构。

回到顶部FPGA设计工具既然您知道了FPGA芯片的组成部分,您可能会问:“如何配置所有这数百万个组件来构建需要执行的逻辑?”

答案是,您可以使用开发工具在软件中定义数字计算任务,然后将其编译为包含有关如何将组件连接在一起的信息的配置文件或位流。过去,FPGA技术面临的挑战是,只有对数字硬件设计有深刻理解的工程师才能使用低级FPGA设计工具。但是,诸如LabVIEW之类的高级综合(HLS)设计工具的兴起改变了FPGA编程的规则,并提供了将图形框图转换为数字硬件电路的新技术。

传统FPGA设计工具

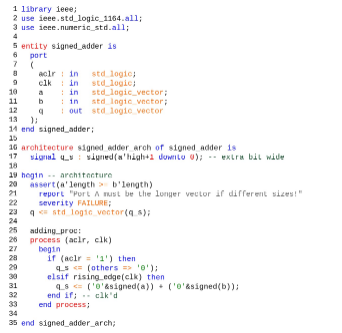

在FPGA开发的前20年中,诸如VHDL和Verilog之类的硬件描述语言(HDL)演变为用于设计FPGA芯片上运行的算法的主要语言。这些低级语言集成了其他文本语言提供的一些优势,并意识到在FPGA上您正在构建电路。产生的混合语法要求将信号从外部I / O端口映射或连接到内部信号,这些内部信号最终连接到包含算法的功能。这些功能按顺序执行,并可以引用FPGA内的其他功能。但是,很难在连续的逐行流程中可视化FPGA上任务执行的真正并行性。HDL反映了其他文字语言的某些属性,

为了验证由FPGA程序员创建的逻辑,通常的做法是在HDL中编写测试平台,以通过断言输入和验证输出来环绕并执行FPGA设计。测试平台和FPGA代码在仿真环境中运行,该仿真环境对FPGA芯片的硬件时序行为进行建模,并将所有输入和输出信号显示给设计人员以进行测试验证。与创建原始FPGA HDL设计本身相比,创建HDL测试平台和执行仿真的过程通常需要更多时间。

使用HDL创建FPGA设计并对其进行验证后,需要将其馈入采用基于文本的逻辑的编译工具,并通过几个复杂的步骤将HDL合成为一个包含以下信息的配置文件或位流:组件应如何连接在一起。作为此多步骤手动过程的一部分,通常需要您指定信号名称到所使用的FPGA芯片上的引脚的映射。

图9. VHDL中的简单计数器FPGA设计

最终,该设计流程中的挑战在于,传统HDL编程所需的专业知识并不广泛,因此,绝大多数工程师和科学家都无法使用FPGA技术。

高级综合设计 工具

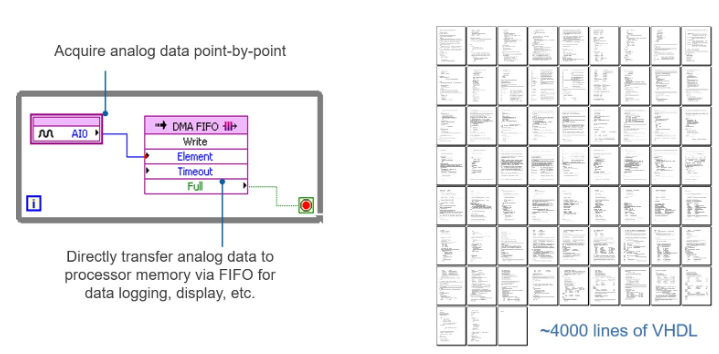

图形HLS设计工具(例如LabVIEW)的出现消除了传统HDL设计过程中的一些主要障碍。LabVIEW编程环境非常适合FPGA编程,因为它清楚地表示了并行性和数据流,因此在传统FPGA设计过程中经验丰富和经验不足的用户都可以利用FPGA技术。此外,为了不丢失以前的知识产权(IP),您可以使用LabVIEW将现有的VHDL集成到LabVIEW FPGA设计中。由于LabVIEW FPGA与硬件高度集成,因此无需像许多HLS代码生成器一样,可以用VHDL重写代码来满足时序或资源限制。

图10.左侧是LabVIEW,它是FPGA的高级设计工具。它为创建和扩展VHDL设计时经常发现的低级复杂性提供了抽象。

然后,为了仿真和验证FPGA逻辑的行为,LabVIEW直接在开发环境中提供了功能。在不了解底层HDL语言的情况下,您可以创建测试平台以行使设计逻辑。此外,LabVIEW环境的灵活性还可以通过导出到周期精确的仿真器(例如Xilinx ISim)来帮助更高级的用户对设计的时序和逻辑进行建模。

LabVIEW FPGA编译工具可自动执行编译过程,因此您只需单击一个按钮即可启动该过程,并在完成编译阶段时接收报告和错误(如果有)。如果由于您的FPGA设计而确实发生了时序错误,LabVIEW将以图形方式突出显示这些关键路径,以加快调试过程。

结局

随着诸如LabVIEW之类的高级工具使FPGA更加易于使用,FPGA技术的采用持续增长。但是,重要的是要查看FPGA内部并了解将框图编译为可在硅片中执行时实际上发生了多少事情。根据触发器,LUT,乘法器和Block RAM比较和选择硬件目标是为您的应用选择合适的FPGA芯片的最佳方法。在开发期间,尤其是在优化大小和速度时,了解资源的使用非常有帮助。本文无意成为所有FPGA基本构建模块的全面清单。您可以从下面的资源中了解有关FPGA和数字硬件设计的更多信息。

我要赚赏金

我要赚赏金