FPGA 是可编程芯片,因此 FPGA 的设计方法包括硬件设计和软件设计两部分。硬件包括 FPGA 芯片电路、 存储器、输入输出接口电路以及其他设备,软件即是相应的 HDL 程序以及最新才流行的嵌入式 C 程序。

目前微电子技术已经发展到 SOC 阶段,即集成系统(Integrated System)阶段,相对于集成电路(IC)的设计思想有着革命性的变化。SOC 是一个复杂的系统,它将一个完整产品的功能集成在一个芯片上,包括核心处理器、存储单元、硬件加速单元以及众多的外部设备接口等,具有设计周期长、实现成本高等特点,因此其设计方法必然是自顶向下的从系统级到功能模块的软、硬件协同设计,达到软、硬件的无缝结合。

典型 FPGA 开发流程与注意事项

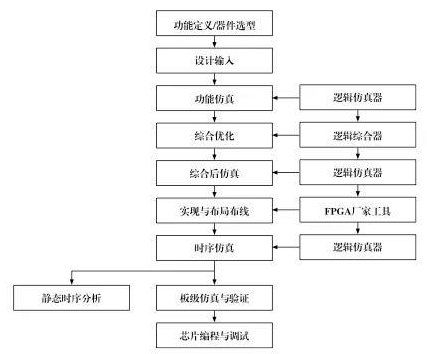

FPGA 的设计流程就是利用 EDA 开发软件和编程工具对 FPGA 芯片进行开发的过程。典型 FPGA 的开发流程一般如所示,包括功能定义 / 器件选型、设计输入、功能仿真、综合优化、综合后仿真、实现、布线后仿真、板级仿真以及芯片编程与调试等主要步骤。

1、功能定义 / 器件选型

在 FPGA 设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。一般都采用自顶向下的设计方法,把系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接使用 EDA 元件库为止。

2、 设计输入

设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,并输入给 EDA 工具的过程。常用的方法有硬件描述语言(HDL)和原理图输入方法等。原理图输入方式是一种最直接的描述方式,在可编程芯片发展的早期应用比较广泛,它将所需的器件从元件库中调出来,画出原理图。这种方法虽然直观并易于仿真,但效率很低,且不易维护,不利于模块构造和重用。更主要的缺点是可移植性差,当芯片升级后,所有的原理图都需要作一定的改动。

目前,在实际开发中应用最广的就是 HDL 语言输入法,利用文本描述设计,可以分为普通 HDL 和行为 HDL。普通 HDL 有 ABEL、CUR 等,支持逻辑方程、真值表和状态机等表达方式,主要用于简单的小型设计。而在中大型工程中,主要使用行为 HDL,其主流语言是 Verilog HDL 和 VHDL。这两种语言都是美国电气与电子工程师协会(IEEE)的标准,其共同的突出特点有:语言与芯片工艺无关,利于自顶向下设计,便于模块的划分与移植,可移植性好,具有很强的逻辑描述和仿真功能,而且输入效率很高。除了这 IEEE 标准语言外,还有厂商自己的语言。也可以用 HDL 为主,原理图为辅的混合设计方式,以发挥两者的各自特色。

3、 功能仿真

功能仿真也称为前仿真是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。仿真前,要先利用波形编辑器和 HDL 等建立波形文件和测试向量(即将所关心的输入信号组合成序列),仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用的工具有 Model Tech 公司的 ModelSim、Sysnopsys 公司的 VCS 和 Cadence 公司的 NC-Verilog 以及 NC-VHDL 等软件。

4、 综合优化

所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供 FPGA 布局布线软件进行实现。就目前的层次来看,综合优化(Synthesis)是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。真实具体的门级电路需要利用 FPGA 制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。为了能转换成标准的门级结构网表,HDL 程序的编写必须符合特定综合器所要求的风格。由于门级结构、RTL 级的 HDL 程序的综合是很成熟的技术,所有的综合器都可以支持到这一级别的综合。常用的综合工具有 Synplicity 公司的 Synplify/Synplify Pro 软件以及各个 FPGA 厂家自己推出的综合开发工具。

5、 综合后仿真

综合后仿真检查综合结果是否和原设计一致。在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响。但这一步骤不能估计线延时,因此和布线后的实际情况还有一定的差距,并不十分准确。目前的综合工具较为成熟,对于一般的设计可以省略这一步,但如果在布局布线后发现电路结构和设计意图不符,则需要回溯到综合后仿真来确认问题之所在。在功能仿真中介绍的软件工具一般都支持综合后仿真。

图 1 FPGA 典型设计流程

6、 实现与布局布线

布局布线可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告),实现是将综合生成的逻辑网表配置到具体的 FPGA 芯片上,布局布线是其中最重要的过程。布局将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,并且往往需要在速度最优和面积最优之间作出选择。布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确地连接各个元件。目前,FPGA 的结构非常复杂,特别是在有时序约束条件时,需要利用时序驱动的引擎进行布局布线。布线结束后,软件工具会自动生成报告,提供有关设计中各部分资源的使用情况。由于只有 FPGA 芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

7、 时序仿真

时序仿真,也称为后仿真,是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规(即不满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等)现象。时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。由于不同芯片的内部延时不一样,不同的布局布线方案也给延时带来不同的影响。因此在布局布线后,通过对系统和各个模块进行时序仿真,分析其时序关系,估计系统性能,以及检查和消除竞争冒险是非常有必要的。在功能仿真中介绍的软件工具一般都支持综合后仿真。

8、 板级仿真与验证

板级仿真主要应用于高速电路设计中,对高速系统的信号完整性、电磁干扰等特征进行分析,一般都以第三方工具进行仿真和验证。

9、 芯片编程与调试

设计的最后一步就是芯片编程与调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generation),然后将编程数据下载到 FPGA 芯片中。其中,芯片编程需要满足一定的条件,如编程电压、编程时序和编程算法等方面。逻辑分析仪(Logic Analyzer,LA)是 FPGA 设计的主要调试工具,但需要引出大量的测****脚,且 LA 价格昂贵。目前,主流的 FPGA 芯片生产商都提供了内嵌的在线逻辑分析仪(如 Xilinx ISE 中的 ChipScope、Altera QuartusII 中的 SignalTapII 以及 SignalProb)来解决上述矛盾,它们只需要占用芯片少量的逻辑资源,具有很高的实用价值。

基于 FPGA 的 SOC 设计方法

目前,由于 FPGA 性能提升价格下降,同时嵌入越来越多内核,很自然地,很多 IC 设计公司将 FPGA 用于 ASIC 原型验证,把 FPGA 可编程的优点带到了 SOC 领域,其系统由嵌入式处理器内核、DSP 单元、大容量处理器、吉比特收发器、混合逻辑、IP 以及原有的设计部分组成。

SOC 平台的核心部分是内嵌的处理内核,其硬件是固定的,软件则是可编程的;外围电路则由 FPGA 的逻辑资源组成,大都以 IP 的形式提供,例如存储器接口、USB 接口以及以太网 MAC 层接口等,用户根据自己需要在内核总线上添加,并能自己订制相应的接口 IP 和外围设备。

基于 FPGA 的典型 SOC 开发流程为:

1、芯片内的考虑

从设计生成开始,设计人员需要从硬件 / 软件协同验证的思路入手,以找出只能在系统集成阶段才会被发现的软、硬件缺陷。然后选择合适的芯片以及开发工具,在综合过程得到优化,随后进行精确的实现,以满足实际需求。由于设计规模越来越大,工作频率也到了数百兆赫兹,布局布线的延迟将变得非常重要。为了确保满足时序,需要在布局布线后进行静态时序分析,对设计进行验证。

2、板级验证

在芯片设计完毕后,需要再进行板级验证,以便在印刷电路板(PCB) 上保证与最初设计功能一致。因此,PCB 布局以及信号完整性测试应被纳入设计流程。由于芯片内设计所做的任何改变都将反映在下游的设计流程中,各个过程之间的数据接口和管理也必须是无误的。预计 SOC 系统以及所必须的额外过程将使数据的大小成指数增长,因此,管理各种数据集本身是急剧挑战性的任务。

听过了太多国产 EDA 工具、FPGA 芯片的报道,很全面,也都能站在国家战略,资本市场等多个宏观角度去思考、分析问题。但我想,对于普通开发者而言,我们当然相信前途是很美好的,但我们也很关心 EDA 工具是否稳定,比如说:

1 500M 的芯片,跑不了 50M 的逻辑,EDA 工具都经历了什么?

2 简单的逻辑就导致布线的拥塞?

3 在线逻辑分析仪抓不到想要的信号?

以上是MYMINIEYE 的 Mill 和高云半导体市场副总裁 Paul(黄俊)从技术的角度聊聊 EDA 工具和 FPGA 芯片。Mill 有着多年的 FPGA 产品开发经验,而 Paul 也在国内外原厂有着多年的技术及市场经验,因此,从开发者和原厂的角度一起探讨 FPGA 开发核心技术问题,说出 FPGA 原厂背后的有趣故事。

我要赚赏金

我要赚赏金