来源:电子质量•作者:郑伟 田书林 周玉

1.引言

示波器测量频率和相位的方法很多, “李沙育图形法”就是其中用得最多的一种。“李沙育图形法”又称波形合成法,就是将被测频率的信号和频率已知的标准信号分别加至示波器的Y轴输入端和x轴输入端,在示波器显示屏上将出现一个合成图形,这个图形就是李沙育图形。李沙育图形随两个输入信号的频率、相位、幅度不同,所呈现的波形也不同。

早期的模拟示波器显示李沙育图形的原理是将电信号转换为光信号,核心部分是阴极射线示波管(CRT)。将输入信号加到示波管内部的偏转系统,高速电子经聚焦、加速和偏转后,打到荧光屏上形成亮点,实现李沙育图形。李沙育图形在数字示波器上显示与在模拟示波器上显示完全不同,输入的两路信号,经采样后变为数字信号,利用CPU做一次算法,通过运算后的数字信号映射到液晶屏上后形成了对应的李沙育图形,此种显示方法也能达到模拟示波器的效果。

该设计应用于手持式数字示波表,主要部分由高速ADC、FPGA、ARM 7和TFT_LCD组成,由于成本原因,选用低速处理器ARM7,其主频低于50MHz,如果采用常规设计方法,达不到模拟示波器相同的显示效果。利用FPGA来实现李沙育图形是该设计的关键所在。

2.FPGA设计原理

由FPGA完成李沙育图形,核心在于利用FPGA的内部数字逻辑单元实现数据的运算与存储。该系统主要由高速数据采集模块、可编程逻辑器件FPGA、微处理器和液晶显示模块等四部分组成,其中显示模块由液晶屏和一块低成本的CPLD组成。当两路信号分别接至A、B通道的输入端,经衰减、放大后输入到数据采集模块进行采样。由ADC采样回来的信号直接送到FPGA,此时数据并不是马上存储到FPGA的内部RAM模块里面,而是先做一次算法处理,此算法的功能就是利应两路信号的数值大小,计算出在液晶屏上的对应的被点亮的像素点的位置,而屏幕上不同的位置又对应不同的地址,此地址作为FPGA内部RAM的地址,用来存储对应的像素点是否点亮的信息,因此实际上RAM内部存储的数据就是一幅李沙育图形。此数据为二进制数据,都由逻辑信号0、1组成,0对应该像素点不被点亮,1则表示点亮。ARM读取这些数据时,RAM屏蔽写使能,只有当ARM把所有的数据读完后,RAM才被重新写使能。可以看到,在ARM读取数据的期间,从A、B两通道输进来的信号仍然在往FPGA里面传送,为了保证数据不丢失,该设计采用了两块大小相同的RAM的乒乓工作模式,即ARM在读取RAM1的数据时,RAM2用来存储输入进来的数据,当读完RAM1的数据后,ARM转到读RAM2的数据,而由RAM1来存储输入进来的数据。

3.李沙育图形在FPGA内部的实现

3.1 FPGA内部算法

为了将纯粹的数字信号转化为对应的李沙育图形,必须从李沙育图形的形成原理来做分析。

李沙育图形上的每一个点都可以下面两个公式来表示:

x=A lsin(ω1t+ψ1) (1)

Y=A 2sin(ω2t+ψ2) (2)

由上式可知,李沙育图形实际上是一个质点同时在x轴和Y轴上振动形成的,其初始相差值△ψ=ψ2一ψ1,频率比为ω2/ω1。为了在屏幕上达到显示的效果,把实际李沙育图形显示区域(256*200)等分为四个象限,水平中心线为X轴,垂直中心线为Y轴。当A、B两通道同时输入进来信号以后,把A通道的数值按由小到大的顺序,从左向右排列,B通道的信号则同理从下向上排列,同时进来的一组信号共同决定了它们所对应的在屏幕上显示的位置,而位置对应了FPGA内部RAM的地址。其算法可由下面两个公式实现:

ADD=Y×1 6+X/1 6 (3)

DATA=X%16 (4)

在这里ADD表示RAM的地址,DATA表示相应的RAM地址中存储的数据。式(3)中Y值的大小表示在垂直方向上的位置,因为前面提到过水平宽度为2 56个像素点,刚好对应了1 6个1 6b i t的二进制数据,即屏幕上的一行对应了1 6个地址单元。Y×1 6可以表示成,Y值每加一次,地址增加1 6。X/1 6是一个除法求整数的计算,此计算结果代表了这一行的l 6个地址中,哪个地址单元将被选中,而此地址单元将用来存储它所对应的屏幕上的1 6个像素点的状态信息。式(4)中X 1 6是一个求余数的运算,此运算结果刚好代表了在式(3)推算出来的地址对应的1 6个像素点中,哪个像素点将会被点亮。上面算法是在FPGA内部采用Verilog语言编程实现。

3.2 RAM工作状态和设计实现

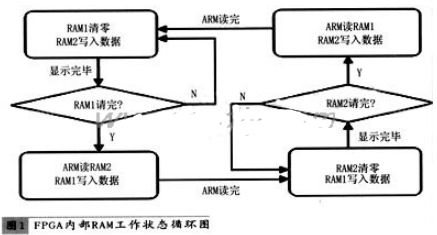

当地址和数据都计算出来后就可以将数据写入RAM模块。在本设计中,F P G A内部的工作状态都是受ARM所控制的,因此实际上ARM就是一个调度中心,它控制着整个系统的工作进程。为了保证数据的不丢失,两块RAM的乒乓工作模式被分成了四个状态(A:RAM 1清零、RAM2写入;B:R AM 1写入、 RAM 2读出;C:RAM 1写入、RAM2清零;D:RAM 1读出、RAM2写入),根据ARM的工作情况,这两块RAM在这四种工作状态中循环转变。其状态流程如图1所示。从流程图可以看到,两块RAM呈现交替的工作状态,使数据不被丢失,保证了整体的流畅性。

在实际的设计中还有下面两个因素需要考虑。一是由于ARM的工作速度相对于FPGA来说慢了很多,因此在对RAM进行有效清零的时候,并不是由ARM来完成,而是当ARM读完数据后,由A R M发一条清零状态命令到FPGA,FPGA根据接收到的命令来执行完成的。实际上就是把ARM与FPGA之间的控制大大简化掉,对于ARM只需要在执行完自己的任务后,将相应的状态发给FPGA,而不去关心FPGA是如何完成相应任务的;FPGA收到ARM发过来的状态命令后,对命令进行解读,通过解读出来的信息,再执行相关的任务。

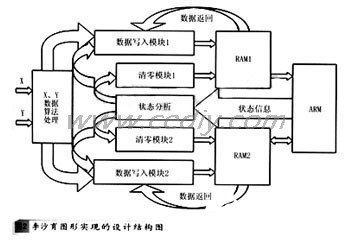

另一个问题就是,假设当A R M在读取R A M 1内的数据时,RAM2正在被写入数据,而ARM需要一定时间才能将所有的数据读完。由于数据还在源源不断的输入,就会出现下面的情况:在R A M 2的同一个地址中,之前可能已经写入了一个数据,而此时又要写入一个新的数据,如果采用直接写入的方式,就会把之前保留下来的数据覆盖掉。为了协调上述矛盾,该设计采取了分时控制的工作方式,即数据写入模块将地址发送到RAM时,屏蔽写使能,而将读使能打开,此时可将地址中之前存储下来的数据读出,将该数据送回到数据写入模块,与新数据做一次按位或操作运算,运算结束后再把写使能打开,将新计算结果写入RAM中。这样既保证了不丢失旧数据,同时也将新数据保存了下来,实现了李沙育图形的完整性。具体设计结构图如图2所示。

当一幅完整的李沙育图形在FPGA内部“产生”后,剩下显示的工作就由ARM来完成,主要工作包括:图形显示和余辉设置。ARM读取数据的时候,是从第一个地址一直读到最后一个地址,相当于从图形的左下方开始,直到右上方结束,显示的时候也是这个道理。ARM将地址和数据依次发给CPLD,CPLD根据对应的地址和数据来驱动液晶屏的显示。

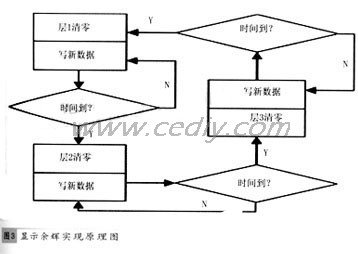

3.3 余辉效应

余辉的设计与实现是通过ARM的软件处理来完成。图形显示区域被模拟成三层重叠的显示层,在这三层中,各层之间相互独立,只要有任何一层在显示,屏幕上就能看到图形,余辉就是根据层与层之间的切换时间来实现的,该切换时间是通过ARM的内部定时中断产生。如图3所示,每次中断时间T到来时,ARM会对下一层做清零处理,即同一层被清零的时间间隔则是3T,因此3 T就是余辉时间,即图象在屏幕上停留的时间。ARM通过修改定时时间T,即可实现不同的余辉时间。在实际设计中添加了1 s、2s、5s、无限余辉和关闭,这五种选项供使用。无限余辉可使显示出来的图像一直保留在屏幕上,只可被新图象覆盖,而不被清除,此种显示方式对于观察极低频信号十分有帮助。

4.结语

利用FPGA在手持式示波表上实现李沙育图形,基本保证了图象的连续性,显示精度高,同时也具备一定的实时性,加上可变的余辉,显示效果已经超过了模拟示波器。该方案的设计在不影响整个示波表性能的同时,为手持式数字示波表添加了另一种测试功能,对于常规的相位和频率测量具有极大的帮助。该方案已经实现于正式产品中,工作良好。

我要赚赏金

我要赚赏金