包括电气间隙(空间距离),爬电距离(沿面距离)和绝缘穿透距离。

1、电气间隙:两相邻导体或一个导体与相邻电机壳表面的沿空气测量的最短距离。2、爬电距离:两相邻导体或一个导体与相邻电机壳表面的沿绝绝缘表面测量的最短距离。一、爬电距离和电气间隙距离要求:1、爬电距离:输入电压50V-250V时,保险丝前L—N≥2.5mm,输入电压250V-500V时,保险丝前L—N≥5.0mm;电气间隙:输入电压50V-250V时,保险丝前L—N≥1.7mm,输入电压250V-500V时,保险丝前L—N≥3.0mm;保险丝之后可不做要求,但尽量保持一定距离以避免短路损坏电源;2、一次侧交流对直流部分≥2.0mm;3、一次侧直流地对地≥4.0mm如一次侧地对大地;4、一次侧对二次侧≥6.4mm,如光耦、Y电容等元器零件脚间距≤6.4mm要开槽;5、变压器两级间≥6.4mm以上,≥8mm加强绝缘。

Part 2

抗干扰、EMC部分

一、长线路抗干扰

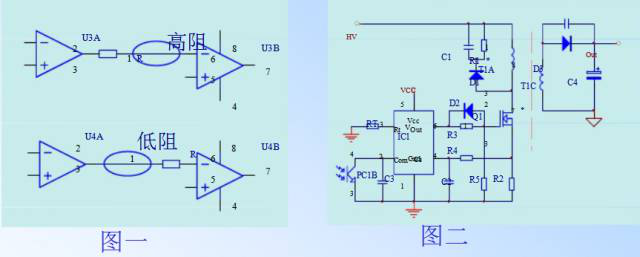

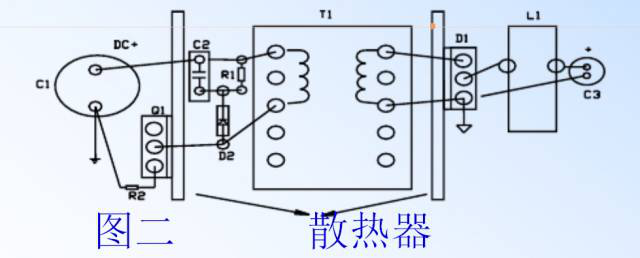

在图二中 ,PCB布局时,驱动电阻R3应靠近Q1(MOS管),电流取样电阻R4、C2应靠近IC1的第4Pin,如图一所说的R应尽量靠近运算放大器缩短高阻抗线路。因运算放大器输入端阻抗很高,易受干扰。输出端阻抗较低,不易受干扰。一条长线相当于一根接收天线,容易引入外界干扰。

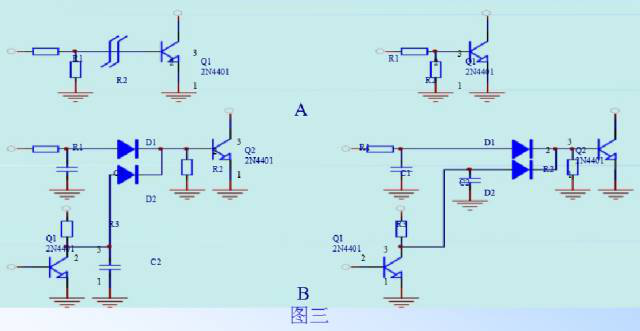

在图二中 ,PCB布局时,驱动电阻R3应靠近Q1(MOS管),电流取样电阻R4、C2应靠近IC1的第4Pin,如图一所说的R应尽量靠近运算放大器缩短高阻抗线路。因运算放大器输入端阻抗很高,易受干扰。输出端阻抗较低,不易受干扰。一条长线相当于一根接收天线,容易引入外界干扰。 在图三的A中排版时,R1、R2要靠近三极管Q1放置,因Q1的输入阻抗很高,基极线路过长,易受干扰,则R1、R2不能远离Q1。在图三的B中排版时,C2要靠近D2,因为Q2三极管输入阻抗很高,如Q2至D2的线路太长,易受干扰,C2应移至D2附近。二、小信号走线尽量远离大电流走线,忌平行,D>=2.0mm。

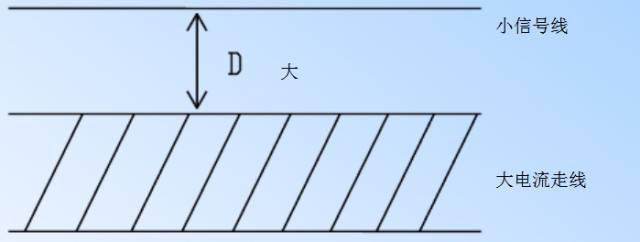

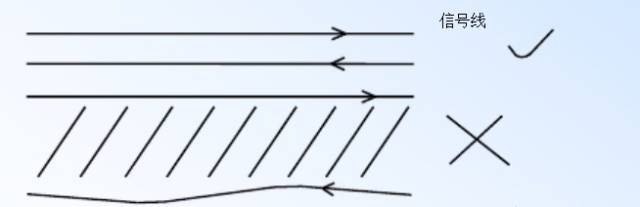

在图三的A中排版时,R1、R2要靠近三极管Q1放置,因Q1的输入阻抗很高,基极线路过长,易受干扰,则R1、R2不能远离Q1。在图三的B中排版时,C2要靠近D2,因为Q2三极管输入阻抗很高,如Q2至D2的线路太长,易受干扰,C2应移至D2附近。二、小信号走线尽量远离大电流走线,忌平行,D>=2.0mm。 三、小信号线处理:电路板布线尽量集中,减少布板面积提高抗干扰能力。四、一个电流回路走线尽可能减少包围面积。

三、小信号线处理:电路板布线尽量集中,减少布板面积提高抗干扰能力。四、一个电流回路走线尽可能减少包围面积。

如:电流取样信号线和来自光耦的信号线

如:电流取样信号线和来自光耦的信号线

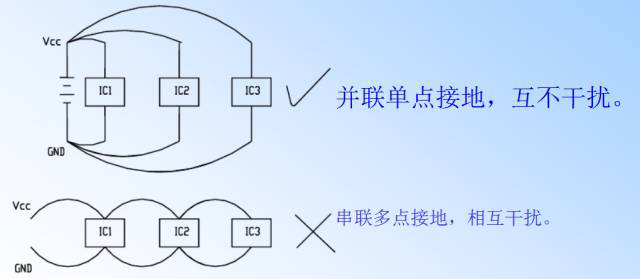

五、光电耦合器件,易于干扰,应远离强电场、强磁场器件,如大电流走线、变压器、高电位脉动器件等。六、多个IC等供电,Vcc、地线注意。

串联多点接地,相互干扰

串联多点接地,相互干扰

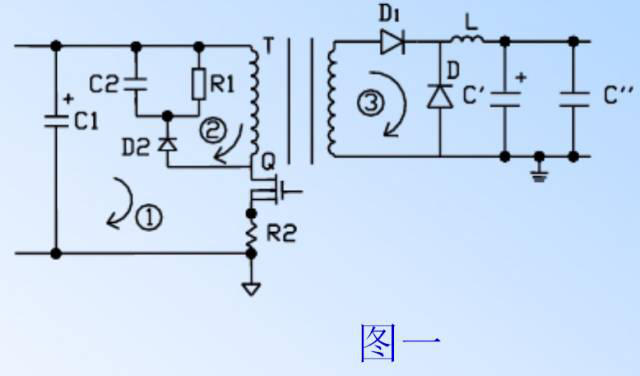

七、噪声要求1、尽量缩小由高频脉冲电流所包围的面积,如下(图一、图二) 一般的布板方式:

一般的布板方式: 2、滤波电容尽量贴近开关管或整流二极管如上图二,C1尽量靠近Q1,C3靠近D1等。3、脉冲电流流过的区域远离输入、输出端子,使噪声源和输入、输出口分离 。

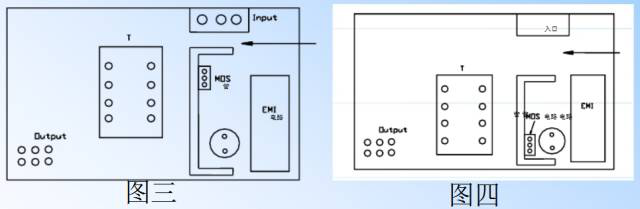

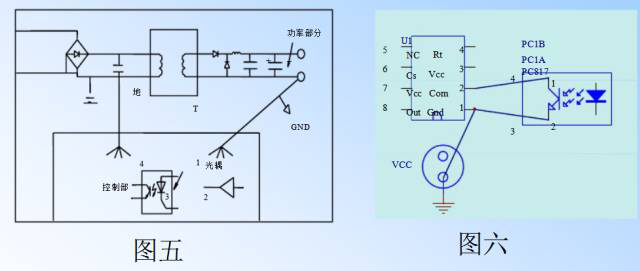

2、滤波电容尽量贴近开关管或整流二极管如上图二,C1尽量靠近Q1,C3靠近D1等。3、脉冲电流流过的区域远离输入、输出端子,使噪声源和输入、输出口分离 。 图三:MOS管、变压器离入口太近,电磁的辐射能量直接作用于输入端,因此,EMI测试不通过。图四:MOS管、变压器远离入口,电与磁的辐射能量距输入端距离加大,不能直接作用于输入端,因此EMI传导能通过。4、控制回路与功率回路分开,采用单点接地方式,如图五。

图三:MOS管、变压器离入口太近,电磁的辐射能量直接作用于输入端,因此,EMI测试不通过。图四:MOS管、变压器远离入口,电与磁的辐射能量距输入端距离加大,不能直接作用于输入端,因此EMI传导能通过。4、控制回路与功率回路分开,采用单点接地方式,如图五。 控制IC周围的元件接地接至IC的地脚 ;再从地脚引出至大电容地线 。光耦第3脚地接到IC的第1 脚,第4脚接至IC的2脚上 。如图六。5、 必要时可以将输出滤波电感安置在地回路上。6、 用多只ESR低的电容并联滤波。7、 用铜箔进行低感、低阻配线,相邻之间不应有过长的平行线,走线尽量避免平行、交叉用垂直方式,线宽不要突变,走线不要突然拐角(即:≤直角)。(同一电流回路平行走线,可增强抗干扰能力)八、抗干扰要求:1、尽可能缩短高频元器件之间连线,设法减少它们的分布参数和相互间电磁干扰,易受干扰的元器件不能和强干扰器件相互挨得太近,输入输出元件尽量远离。

控制IC周围的元件接地接至IC的地脚 ;再从地脚引出至大电容地线 。光耦第3脚地接到IC的第1 脚,第4脚接至IC的2脚上 。如图六。5、 必要时可以将输出滤波电感安置在地回路上。6、 用多只ESR低的电容并联滤波。7、 用铜箔进行低感、低阻配线,相邻之间不应有过长的平行线,走线尽量避免平行、交叉用垂直方式,线宽不要突变,走线不要突然拐角(即:≤直角)。(同一电流回路平行走线,可增强抗干扰能力)八、抗干扰要求:1、尽可能缩短高频元器件之间连线,设法减少它们的分布参数和相互间电磁干扰,易受干扰的元器件不能和强干扰器件相互挨得太近,输入输出元件尽量远离。

2、某些元器件或导线之间可能有较高电位差,应加大它们之间的距离,以免放电引出意外短路。

我要赚赏金

我要赚赏金