1 引言

FPGA是新型的可编程逻辑器件,能够将大量的逻辑功能集成于单个器件中,它所提供的门数从几百门到上百万门,符合系统芯片(SOC—System On Chip)的发展要求,具有高度集成、低功耗、硬件升级等优点,可以满足不同的需要。

随着电于技术和网络技术的不断发展,以可编程逻辑器件为核心设计制作的全电子式计量表必将取代传统的感应式计量表。尤其是集群式、模块化、全电子数字化计量表,将会成为民用主导产品。

利用电子技术和传感技术,对传统水表加以改进,本设计主要是用 FPGA设计水费计量芯片,芯片接受已处理好的脉冲信号,每 1000个脉冲记为 1 吨。

2 基于 FPGA的水表设计

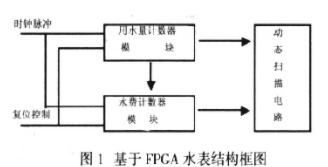

2.1基于 FPGA水表的结构图要设计的水费计量芯片主要功能如下:能对用水吨位计数,在动态扫描电路显示用水吨数,为了结构清晰,这里只设计显示用

水吨数的十位、个位、十分位、百分位。

能对用水水费分段计费。这样做的目的是为了提高人们的节水意识,在我国的有些地区已实行了水费的分段计费。当用水量不足一定数字时(如每年每户 40吨),水费费用较低(如每吨 1.2元),当用水量超过一定数字时,水费费用较高(如每吨 2.2元),计费结果送动态扫描电路显示,为了结构清晰,这里只设计显示水费的百位、十位、个位、十分位。

首先把系统分为几个模块,然后再分别用 VHDL实现。最后把各个模块连接起来,构成整个系统。本设计分为以下三个模块:用水量计数模块、水费计数模块、动态扫描电路显示模块。两个计数模块是整个测量系统的核心,进行计数,计数结果送到动态扫描电路模块进行连续实时显示。整个系统模块结构框图如图一所示。

2.2用水量计数模块

用水量计数模块是水费计量芯片的核心部分,它通过对被测脉冲计数来进行测量。计数模块在每次测量前,接受复位信号 RESET,对模块进行复位,清除上次的测量结果,为新的一次测量做准备。计数结果送到动态扫描电路模块进行连续实时显示。

主要程序如下:(为了结构清晰,对部分内容进行了删减)

……

begin

process(clk,reset)

variable kg : std_logic_vector (11 downto 0);

begin

if reset=‘0’ then

kg:=“000000000000”;

elsif clk‘event and clk=’1‘ then

if kg(3 downto 0)=“1001” then

kg:=kg+7;else kg:=kg+1; end if;

if kg(7 downto 4)=“1010” then

kg:=kg+“01100000”; end if;

if kg(11)=’1‘ and (not(kg(10 downto 9)=“00”)) then

kg:=kg+“011000000000”; end if;

end if;

count1《=kg(3 downto 0);

count2《=kg(7 downto 4);

count3《=kg(11 downto 8);

……

2.3水费计数模块

水费计数模块也是水费计量芯片的核心部分,它通过对被测脉冲计数来进行测量,并接收处理用水量计数模块的计数结果,水费计数模块在每次测量前,也接受与用水量计数模块相同的复位信号 RESET,对模块进行复位,清除上次的测量结果,为新的一次测量做准备。计数结果同样送到动态扫描电路模块进行连续实时显示。

主要程序如下:(为了结构清晰,对部分内容进行了删减) ……

……

begin

money《=“00100010” when ((judge(3)=’1‘) or (judge(2)=’1‘)) else “00010010”;

process(clk,reset)

variable mm : std_logic_vector (15 downto 0);

begin

if reset=’0‘ then

mm:=“0000000000000000”;

elsif clk’event and clk=‘1’ then

mm:=mm+money;

if mm(3)=‘1’ and (not(mm(2 downto 1)=“00”)) then

mm:=mm+6; end if;

if mm(7)=‘1’ and (not(mm(6 downto 5)=“00”)) then

mm:=mm+“01100000”; end if;

if mm(11)=‘1’ and (not(mm(10 downto 9)=“00”)) then

mm:=mm+“011000000000”; end if;

if mm(15)=‘1’ and (not(mm(14 downto 13)=“00”)) then

mm:=mm+“0110000000000000”; end if;

end if;

count1《=mm(3 downto 0);

count2《=mm(7 downto 4);

count3《=mm(11 downto 8);

count4《=mm(15 downto 12);

mcount《=mm;

……

2.4动态扫描电路显示模块

动态扫描电路将水量计数模块及水费计数模块的计数结果用七段显示数码管显示出来,所连接的数码管共用一个数据端,由片选信号依次选择输出,轮流显示。其程序比较常见,这里省略。

3 仿真

在 MAX+PLUS II中建立水费计数模块 RESET=‘1’时的仿真波形如图二。图二中 RESET为复位信号,当 RESET=‘0’时,系统复位,当 RESET=‘1’时,各计数器正常计数。judge(3)和 judge(2)是用水量计数模块输出结果 count3的最高两位二进制数,当它们有一个值为‘1’时,表示用水量大于 40吨。count1、count2、count3、count4分别对应水费的十分位、个位、十位、百位,在程序中用 8421BCD码给出,为清楚起见,在仿真时用十进制数给出,图中虚线左侧水费每吨 1.2元,当用水量达到 40吨时,judge(3)=1,在图中虚线右侧水费每吨 2.2元,因此,水费从 48.0元跳变到 50.2元。

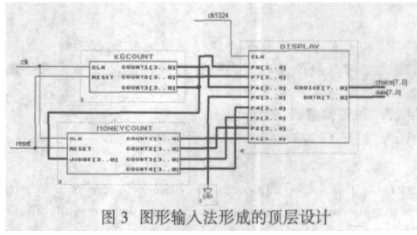

在 MAX+PLUS II中用图形输入法形成的顶层设计如图三所示。通过编译、仿真后,下载到 EP1K30TC144-3目标芯片中实际测试并获得了满足设计要求的结果。

4 结论

本文设计了基于 VHDL语言的水表的几个模块:用水量计数模块、水费计数模块、动态扫描电路显示模块。每个模块都通过了功能仿真和时序仿真,生成了可综合的网表文件,并下载到 EP1K30TC144-3芯片中。仿真和测试的结果表明每个模块均完成了其逻辑功能。

利用可编程逻辑器件丰富的内部资源,借助EDA工具把水表电路集成在一片FPGA芯片内,从而减小了电路的体积、提高了系统的可靠性。具有设计周期短、设计费用和风险低、功能灵活的特点。

我要赚赏金

我要赚赏金