随着目前数字技术的发展,多通道数据的高速采集处理获得了广泛的应用,面对大的数据吞吐量,往往需要共享一块大的缓存空间(外挂的大容量存储SDRAM或是DDR)。而大多时候多通道之间的实时数据流量并不一定平衡。这样必须有一套合理多通道复用仲裁方法,达到整个数据存储效率最大化,用最小的存储空间达成最大的平均吞吐。

外部高速缓存的基本读写流程描述

外部缓存SDRAM (DDR)由于读写共用一个物理接口,所以读写需要分时产生,读时不能写,写时不能读。而且对于易失性存储设备(掉电数据丢失),必须对内部数据定时刷新操作,同时在读写开始和完成时进行打开和关闭行操作,这样就使每一次的读写占用很多控制开销,使得底层操作效率不高,但这是易失性存储的特点,也就是刚性开销,所以对于整个系统的存储效率提升,外部数据流控和仲裁策略的设计就尤为关键。

基于FPGA的多通道仲裁设计总体结构

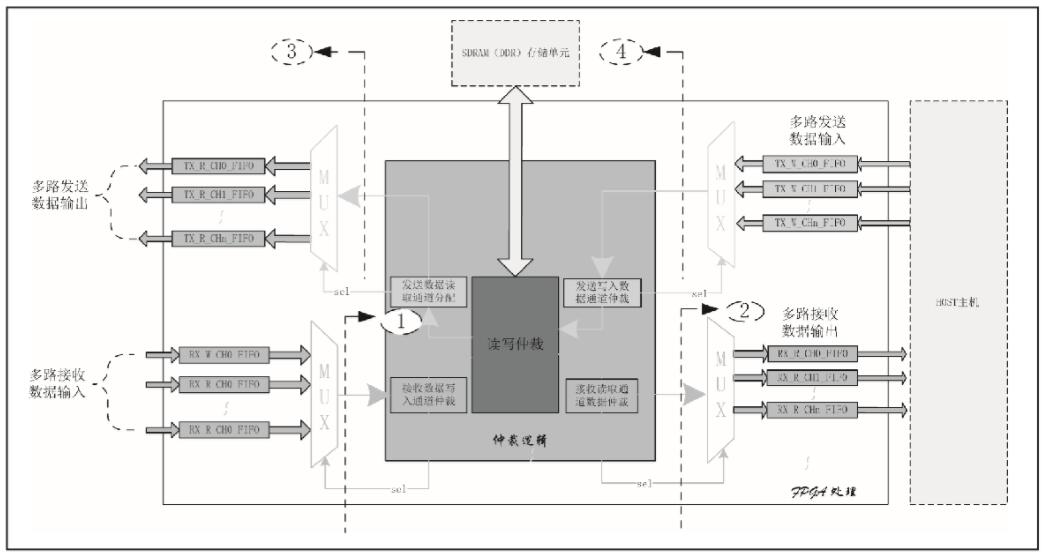

基于FPGA的多通道仲裁设计总体结构如图1所示。

图1逻辑处理多通道数据流程结构

使用场景描述

典型应用场景,主机通过软件和逻辑处理部分进行数据交互,交互包括发送数据处理和接收数据处理两部分(发送和接收都是想对于HOST主机来讲的)。

(1)发送处理部分:逻辑接收HOST主机的数据,然后根据仲裁逻辑的优先级策略分通道写入SDRAM (DDR)中进行缓存(写操作),在发送的下游数据接口,仲裁逻辑再从SDRMA(DDR)中读取数据发送到相应的通道出口中去

(2)接收处理部分︰逻辑从外部接口收到多通道数据,然后根据仲裁模块发出的仲裁优先级顺序将数据分通道写入SDRAM (DDR)中存储,在逻辑和主机HOST接口端,仲裁模块从SDRAM (DDR)中读出各通道数据送给HOST主机处理。

我要赚赏金

我要赚赏金