AVS是中国自主制定的第二代音视频编码标准。从编码效率上看,AVS与H.264/AVC相当,比MPEG-2高两倍;从编码的复杂度上看,AVS的编码复杂度相当于H.264的70%,解码复杂度相当于H.264的30%。同时,AVS不需要交纳高额的专利费用,具有很广阔的市场前景,如:数字音视频存储、IPTV和视频监控等。

TMS320DM642是TI公司推出的一款面向多媒体信号处理的DSP,采用了C64x核。它具有极强的处理能力、高度的灵活性和可编程性,同时又集成了音视频和网络通信等外设,特别适用于多媒体通信应用。DM642可应用于基于IP的音视频传输、数字视频记录、机器视觉、医学成像、安全监视和数字相机等领域。

本文把AVS解码软件移植到DM642平台上,并进行了优化,对于标清视频,解码速度达到30fps,完全满足实时播放的要求。

AVS标准

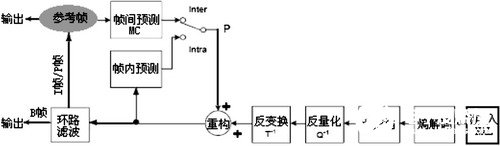

AVS的解码过程如图1所示。

图1AVS****

AVS视频编解码标准中的核心技术包括:帧内预测、1/4精度像素插值、特殊的帧间预测运动补偿、8×8整数变换、量化、二维熵编码和去块效应环内滤波等。

AVS亮度和色度帧内预测都是以8×8块为单位的。亮度块采用5种预测模式,色度块采用4种预测模式。在编码效率基本相同的情况下,AVS采用了更少的预测模式,使算法的复杂度大大降低。

对于帧间的运动补偿,AVS采用了4种块:16×16,16×8,8×16及8×8,可以更好地刻画物体运动,提高运动搜索的准确性,同时降低了运动矢量和块模式传输的开销,从而提高压缩效率,降低了编解码实现的复杂度。AVS与H.264、MPEG-4一样,采用了1/4像素插值,但与H.264的6抽头1/2像素插值和双线性1/4像素插值不同,AVS采用了两种4抽头滤波器对1/2和1/4像素进行插值,在不降低性能的情况下减少了插值所需要的参考像素点,减小了数据存取带宽需求。

8×8的整数变换可以在16位处理器上无失真的实现,克服了早期的8×8变换不能无失真的缺点,同时又比H.264中4×4的整数变换有更好的去相关性。

在AVS熵编码过程中,所有的语法元素和残差数据都是以指数哥伦布码的形式映射成二进制比特流。采用指数哥伦布码的优势在于:一方面,它的硬件复杂度比较低,可以根据闭合公式解析码字;另一方面,它可以根据编码元素的概率分布,灵活地确定以k阶指数进行哥伦布码编码,如果k选得恰当,则编码效率可以逼近信息熵。利用解码后的数据,通过查表得到残差数据。

AVS采用了两个级别的环路滤波,只对边界的两个像素进行滤波。与H.264的4个级别和边界3个像素的环路滤波相比,复杂度大为降低。

TMS320DM642平台

TMS320DM642/C64x系列芯片基于超长指令字结构VelociTI.2,在8个功能单元里扩展了88条新的指令,以增强其在视频/图像应用中的性能,并提高了视频处理的并行性。

本文的实验平台采用SEED公司的VPM642板卡,其主要配置如下:600MHz的TMS320DM642DSP芯片;DM642外部扩展4MBFlash,32MBSDRAM,可用于大量视频图像数据和程序的存储;4路视频端口(PAL/NTSC制式或S端子);10/100M以太网接口;板上JTAG仿真接口,通过JTAG仿真器可以方便地进行视频压缩算法的仿真调试。

AVS在DM642上的实时解码

针对DSP的特点,本文采用了大量行之有效的优化方法,使得解码速度大大提升。除了使用C6000编译器提供的编译选项-pm、-o3、-nodebug以外,其他优化措施主要包括以下几个方面。

程序结构的调整

为了满足DSP结构的需要,本文对AVS解码软件的程序结构进行了调整。

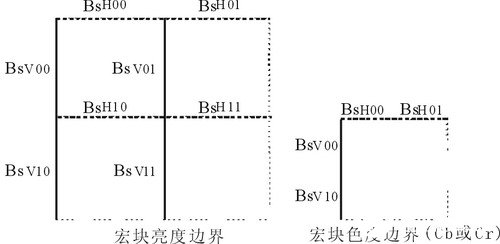

PC上的程序是在解码一帧后再进行环路滤波,需要两次把数据从片外搬移到片内。本文对此进行了修改,在每个宏块解码完成以后就对该宏块进行滤波。如图2所示。

图2环路滤波示意图

在解码一个宏块完成以后,先对每个8×8亮度块的垂直边界BsV00、BsV01、BsV10、BsV11和色度块BsV00(U)、BsV01(V)进行滤波,滤波的结果作为输入,再对水平边界进行滤波。

使用内联指令和数据打包

C++6000编译器提供了许多内联函数(instrinsics),如_add2、_avgu4、_dotpsu4等。内联函数是直接与C6000汇编指令映射的在线函数。不易用C/C++语言实现功能的汇编指令都有对应的内联函数。

对C6000的存储器进行访问是很费时的。要提高C6000的数据处理效率,应使1条Load/Store指令能够访问多个数据。当程序需要对一连串的字符型、短型数据进行访问时,可以使用数据打包,一次读写4个字符型、2个短型数据,并使用_dotpsu4、_add2等指令进行处理。

本文在优化过程中广泛采用了内联指令和数据打包,对于水平位置1/2像素插值,使用内联指令和数据打包的效果如表1所示。

使用线性汇编

经过C语言优化的解码程序如果仍然达不到实时的要求,则需要继续进行汇编优化。与标准的汇编语言相比,采用线性汇编语言进行编程不用考虑并行指令的安排、指令延迟和寄存器的使用,以上工作均由汇编优化器自动完成,而且,所产生的代码效率可以达到手工汇编的95%“100%。

由于IDCT在程序中使用频繁,比较占用时间,且程序相对简单。本文对此进行了线性汇编优化,优化前和优化后的时间比较见表2。

QDMA的合理使用

QDMA(快速存储器直接访问)是DMA和EDMA的进一步发展,其提交传输申请的速度比DMA和EDMA快很多。实际上,QDMA是C6000中搬移数据效率最高的手段之一。QDMA支持灵活的数据传输,它可以完成一维到一维的数据传输,也可以完成二维到一维或一维到二维的数据传输。

对于数据量较大的传输,要尽量采用QDMA。本文对QDMA进行了实验,在将两场数据合并为一帧数据时,分别采用memcpy和QDMA,其时间统计见表3。

Cache的合理分配

TMS320DM642提供了256KB的片上RAM,它既可以当作普通RAM使用,也可以配置为Cache。DM642的Cache设置可以是32KB、64KB、128KB、256KB不等。设置的Cache越大,命中率越高,但留给程序使用的片内RAM也就越少。为了可以把使用频率较高的数据和代码放置在片内,本文采用了128KB的Cache和128KB片内RAM的配置方案。

采用了以上的优化策略,AVS标清视频在DM642上的解码速度达到30fps,完全满足了IPTV(25fps)实时播放的要求。

结语

AVS解码在DSP上的实时实现具有重要的意义,它可以应用到IPTV、数字视频监控等领域,具有很好的市场应用前景。

我要赚赏金

我要赚赏金