数字前端设计也称逻辑设计,前端以设计架构为起点,以功能正确且满足目标时序的网表为终点,用逻辑电路实现预期的功能。主要包括:规则书制定、系统架构设计、部件详细设计、HDL编码、仿真验证、SDC编写、逻辑综合、STA检查、形式化验证等,系统架构设计最难掌握,需要有丰富的设计经验,对应用场景也需要有深入的理解。

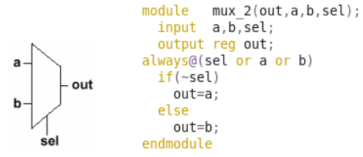

前端设计师需要掌握的最基本技能就是实现编码,但编码不是数字前端设计的全部,它只是前端设计过程中的部分工作。下面编写一个MUX逻辑,MUX的行为可以描述为:只要信号a或b或sel发生变化,如果sel为0则选择a输出;否则选择b输出。

学习前端设计首先要掌握数字电路基础知识并建立硬件意识,基本的数字电路像与或非门、D触发器、计数器、移位寄存器、状态机、多路选择器、译码器等一定要掌握,所有复杂的电路都可由这些基本电路构成,软件设计和逻辑设计的不同要明白,软件是顺序执行思维,而逻辑设计需要并发思维。

数字电路是由很多的与非门及D触发器构成,上电之后所有部件都同时运行,不会因为A触发器的代码描述在 B触发器之前A触发器就先工作,事实上,RTL级代码书写的先后顺序在综合成网表文件后就消失了,取代的是基本逻辑电路之间的互联关系描述。数字电路功能中存在先后顺序的关系,但这种顺序不是靠代码的先后顺序来实现,它的先后顺序是基于时间轴(时钟)来实现,它的承载体是时序逻辑(触发器)。

因此逻辑设计需要的是一种并发的思维,设计师需要用并发的思维去考虑电路的设计。

前端设计流程

1.规格制定

规格制定是芯片设计中最重要的步骤之一,这个步骤就像是在设计建筑前, 先决定要几间房间、浴室,有什么建筑法规需要遵守,在确定好所有的功能之后再进行设计,这样才不用再花额外的时间进行后续修改。如果规格还制定好就开始设计,很难确保设计中不出任何差错。

规格制定前需要进行市场调研,收集客户需求,第一步是确定芯片的功能、功耗、性能,对大方向做设定;接着需要确定兼容那些规范,如无线网卡的芯片就需要符合 IEEE 802.11 等规范;最后则是确立这颗 IC 的制作方法,将不同功能分配成不同的单元,并确立不同单元间连结的方法,如此便完成规格的制定。

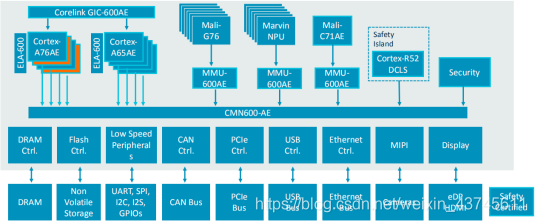

2.系统架构和部件详细设计

这个步骤就像初步有了建筑的规划,将整体轮廓描绘了出来,方便后续制图。根据规则需求编写详细设计文档,明确具体架构,划分功能模块。对不确定的功能进行建模测试确保方案可顺利实现,这个阶段就是确定芯片设计的细节。

基于ARM的自动驾驶芯片系统架构图

做好设计方案非常重要,这里说的方案绝不是只摆几个框图,设计的时候需要做总体设计方案、逻辑详细设计方案,这两种方案包括了很多东西,总体方案主要是一级功能模块的划分及接口时序的定义,而逻辑详细方案就是代码的文字及图形描述(模块内部所有关键信号的时序最好都设计好)。

3.HDL编码

很多人在做逻辑设计时喜欢一上来就狂写代码,写到一半后发现了功能问题,只好推倒重来,反复好几次才能做到仿真基本正确,最后通过修补凑时序达到对的功能。这个做法除了设计周期长外,代码的质量也难以保证,往往存在很多冗余的逻辑,甚至会有一些隐藏较深的bug。

所以数字逻辑设计一定要方案先行,根据方案写代码,这样才能在写代码时做到胸有成竹,避免逻辑混乱的情况。其实在方案阶段把时序设计好后,模块内部各个信号之间的逻辑关系也就理得差不多了,之后就是将它翻译成代码的体力劳动了。

HDL编码这个阶段是要使用硬体描述语言(HDL)描述实现功能模块,也就是把电路描写出来。常使用的HDL有 Verilog、VHDL等,国内一般使用verilog编写RTL(寄存器传输级)代码。

4.功能验证

功能验证就是检验编码设计的正确性,不符合规格的要重新设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。设计师一般只做基本通路验证,功能和代码的详细验证一般由验证工程师完成,验证和设计可同步进行。

常用仿真工具:

Synopsys的VCS,Mentor ModelSim(Linux版本为Questasim),Cadence Xcelium(老版本叫incisive)。

5.编写SDC和代码检查

SDC是一种约束文件,这里的约束是针对综合和布局布线工具而言的。为什么会有约束这个东西出现呢?主要原因是EDA软件比较笨,难以理解设计师的心思,如果设计师不把更详细的信息告诉它的话它就干不好活,所以设计师需要用SDC来把设计意图(时序、面积和功耗等)传达给EDA工具。

这里说的代码检查是指用EDA工具(spyglass最常用)来检查和诊断设计中可能存在的潜在问题,然后用其分析和追踪问题的根源,RTL级一般做lint、CDC(多时钟域检查)、Constraint(约束)三个方面的检查。

常用的检查工具:spyglass

6.逻辑综合

逻辑综合就是把HDL代码翻译成门级网表(netlist),综合需RTL代码和SDC文件。逻辑综合需要基于特定的综合库,不同库中的门电路基本标准单元(standard cell)的面积,时序参数是不一样的,因此综合出来的电路在时序,面积上是有差异的。一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真)。

常用综合工具:Synopsys的dc,cadence的genus

7.静态时序分析

Static Timing Analysis(STA),静态时序分析属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。

STA工具:Synopsys的Prime Time。

8.形式验证

形式化验证属验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。

形式验证工具:Synopsys的Formality,cadence Conformal。

前端设计入门要学的知识

前端设计所需知识很广,最好的学习方法就是项目实践,光看书和视频教程是学不会的,真正入门得靠项目。重点在于掌握设计思想和分析问题的方法,形成良好书写习惯(遵循代码书写、命名规范),最好把常用的基本的电路标准化、固定化。

高手水平高并不是体现在他能写出一些很奇特的电路,相反水平高体现在他们总能将复杂的电路用一些很朴素的基本电路去描述。

前端设计一般需要掌握的知识有Linux操作基础、数字电子基础、verilog语言、计算机体系结构、脚本语言、EDA仿真工具等。

我要赚赏金

我要赚赏金