作者:李晓欢,陈倩,李全,陈石平

引言

随着UWB(ultrawideband)信号产生与接收技术的发展,对UWB信号传播特性的认识逐渐完善,UWB在通信、雷达、定位、导航和电子对抗等诸多领域具有广泛的应用前景,已成为无线通信领域的一个研究热点。UWB是一种新颖无载波传输技术,利用纳秒及亚纳秒量级的非正弦式窄脉冲作为传输载体进行数据通信,因此其所占的频谱范围很宽。2002年FCC颁布了UWB的频谱规划,并规定在-10dB处信号绝对带宽大于0.5GHz或分数带宽大于20%。目前超宽带纳秒级脉冲的产生方法主要用模拟的隧道二极管或晶体管雪崩击穿翻转瞬间产生脉宽为纳秒级的脉冲,从其产生的原理可看出,这样的产生方法不利于电路设计的更改和实时调试,而且在晶体管雪崩击穿过程中会有一个比较高的瞬时电压,这会使得整个****机的功耗比较高,稳定性也随之减弱。

1全数字化UWB信号特性

TH-UWB信号由于具有良好的随机性和伪随机性、抗干扰性能好、****功率低等优势,使得超宽带技术在雷达、通信、定位领域得以迅速发展。UWB信号具有以下特点:

①低截获/检测概率:脉冲越窄,带宽越宽,功率谱密度越低。低功率谱密度使信号难于被敌方截获或检测到,非常适合于军事保密通信,同时对其他信号的干扰小,对商用通信也非常有利。

②强抗多径能力:脉冲窄,且占空比低,经传播延时的反射波与直射波的时间差一般会超过UWB脉冲宽度,所以多径信号在时间上是分离的,其重合或部分重合的概率很低,从而UWB通信系统具有很强的抗多径能力。

③具有良好的穿透障碍物能力:UWB信号可以穿透墙壁或其他障碍物,可用于对人或其他目标进行动目标检测和测距,也可穿透地面检测道路、桥梁的内部情况。

④数字UWB发生器结构简单,成本比较低,易于电路实现,工作稳定,效率高。

2脉冲位置调制(PPM)方式的TH-UWB信号设计

对于UWB发生器系统,信息调制方式非常重要,UWB发生器系统可用不同的伪随机码(PN码)来区分每个用户。实现多址的方法主要有低占空比的跳时(TH)和高占空比的直接序列相位编码(DSC)两种方法,可分为TH-UWB和DSC-UWB两种系统。本文采用PPM方式的TH-UWB信号设计。

PPM调制又称为跳时脉冲位置调制,是使用信息序列控制脉冲相对于参考位置提前或时延。为了达到信号要求,还要用伪随机码或伪随机噪声对数据符号进行编码。香农在证明编码定理时,提出用具有白噪声统计特性的信号来编码,其瞬时值服从正态分布,功率谱在很宽的频带内都是均匀的,具有极其优良的相关特性。由于硬件无法实现对白噪声信号的放大、调制、检测、同步及控制等,本文利用具有类似于带限白噪声统计特性的伪随机信号来逼近它。信号调制数学描述(方程式)如下

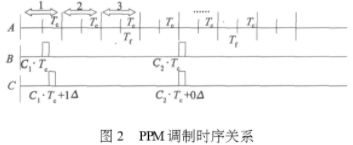

由于该调制系统比较抽象,本文采用图形化描述。图2表示当前PN码对应的值分别为1、2(p=3)时,对应位置在时间轴上的表示见图2。

图2中,A表示时间坐标轴,Tf是无调制时码元的重复周期——重复帧;由于周期p=3,故Tf=3×Tc;B表示PN码分别为C1和C2的两帧信号,可以看出第一帧为C1,第二帧为C2,实现第一轮位置调制;C表示加入数据码的位置跳变(延时△),可以看出第一帧携带的二进制信息为“1”,第二帧携带的二进制信息为“0”。以上调制由图1中两次时延调制完成,最后把携带位置信息调制信号经窄脉冲产生器产生窄脉冲信号。

3信号发生器设计原理

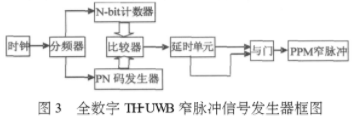

与传统的无线****机结构相比,UWB****机的结构相对比较简单,伪随机码产生器产生的序列状态并行输出,得到一个周期的随机码。开始时计数器计数,并每隔一个周期宽度时间计数器加1,再将两者送入比较器进行比较,当二者数值一致时,输出为脉位调制信号。最后经纳秒级脉冲电路产生携带位置调制信息的窄脉冲即为TH-UWB窄脉冲信号。能够准确产生脉宽较稳定的纳秒级窄脉冲的电路是工程设计过程中的关键。信号通过逻辑电路、逻辑门连接线、I/O连接线都会产生相应的逻辑门延时和走线延时,那么从理论上讲,连续偶数个非门相连,即可得到一个信号延时,但在实际的工程设计中,这样的逻辑连接方式在软件综合过程中可能被逻辑门连接线代替,达不到产生窄脉冲的延时效果,而通过I/O与片外逻辑门相连,会使逻辑延时难于准确控制,增加了整个系统的复杂度和不稳定因素。本文利用FPGA逻辑单元间的延时特性,考虑片内走线延时,利用等效逻辑运算原理编写了可控延时程序,在设计过程中可以根据信号输出的延时情况进行信号延时,调整输出脉冲的宽度。

其产生的系统框图如图3所示。

4建模及仿真

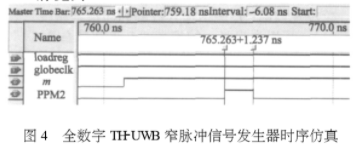

模型思想:经过位置调制之后的信号脉宽为一个全局时钟周期,故利用位置调制之后的信号经触发器进行触发,可以得到一个和原信号波形相同且有一个器件逻辑门延时的新信号,与此同时位置调制信号被整形,消除了原信号由于逻辑运算产生的毛刺(竞争冒险)。再利用所得的信号求非逻辑运算,最后与原输入信号求逻辑与运算,得到一个携带位置信息的窄脉冲。时序电路仿真如图4所示。图中PPM2为携带位置信息的窄脉冲信号,m为串行伪随机序列。

由图4可以看出伪随机序列确定输出脉冲在时间轴上的位置范围,且时序仿真测得TH-UWB信号PPM2脉宽为1.237ns。

5硬件电路实测及数据分析

TH-UWB窄脉冲信号发生器系统硬件平台AlteraDE2FPGA开发平台,采用50MHz的时钟,目标芯片:CycloneⅡEP2C35F672C6。

硬件电路利用AgilenTInfiniium数字示波器进行信号波形观测(带宽600NHz,采样深度4GHz)。图5、6为数字示波器实际观测波形图。图5所示波形为携带位置调制信息的输出纳秒级窄脉冲信号,据图中所测参数可知其脉冲的宽度为1.3088ns,上升时间为781ps,脉冲的峰峰值为2.041V。测试中的数据与前面仿真计算的结果非常相似。图6所示波形为携带位置调制信息的输出纳秒级窄脉冲信号及其频谱,测试其-10dB带宽约为0.55GHz。

从以上实测结果可以看出本设计电路产生的信号能够满足各项要求,具有很强的实用性;同时,在实际测试中,该电路可以稳定地产生重复频率达50MHz的TH-UWB脉冲,输出的脉冲已经携带位置调制信息,无需进行二次调制,实测脉冲宽度其脉宽在1.28ns±60ps,与时序仿真脉宽相符(约800MHz)(本文分析用波形图脉冲宽度为1.3088ns),信号-10dB带宽在0.55GHz左右,满足信号设计的要求。

6结语

本文利用FPGA实现了全数字化的TH-UWB窄脉冲信号发生器,并在AlteraDE2FPGA开发平台下实现并达到TH-UWB窄脉冲发生器的信号要求。该系统较其他模拟电路实现的超宽带纳秒级脉冲的产生方法更有利于电路的实现。模拟电路实现纳秒级脉冲发生器,虽然其脉冲宽度最窄可以达到亚纳秒级、幅度最高可以达到几十伏,但其电路规模较大,电路功耗较高,可调性较差;而利用FPGA设计的全数字发生器,系统的信号调制、脉冲产生都在片内进行,大大地降低了****机电路规模和功耗,提高了稳定性,更有利于低功耗手持超宽带设备的发展,同时数字电路易于实现,结构简单,具有成本低、开发周期短、应用范围广等优点。

我要赚赏金

我要赚赏金