目前的卫星遥感图像压缩系统硬件方案大多基于高性能可编程逻辑器件FPGA[2-4]。但这种方案整系统成本居高不下,且FPGA存在单粒子翻转效应。因此,笔者提出一种多DSP+FPGA的硬件设计结构,使用DSP取代FPGA完成核心算法,而仅用一个FPGA进行管理和控制。该硬件设计成本较低。

1 基于双正交叠式变换的低复杂度图像压缩方法

1.1 双正交重叠变换的快速整数实现

在有损压缩中,通常先对图像矩阵进行正交/双正交变换,使能量分布集中,表示更为稀疏。离散余弦变换(DCT)由于具有良好的去相关效果,并且存在相应的快速算法,应用广泛。双正交重叠变换继承了DCT 计算简便、存储要求低的特点,同时克服了DCT的块效应。这里以LBT为蓝本提出双正交重叠变换的快速整数实现算法,所有系数均采用分母为2的幂、分子为整数的分数近似,从而使整个变换过程只需要整数加法和位移运算。图1给出了一维binLBT的实现流程,二维变换按先行后列的顺序分别进行一维变换。

1.2 零树编码的简化与改进

SPIHT作为一种高效零树编码方法,对位平面进行了集合划分,将大量的非重要位0集中到几个具有特定模式的集合里面,并对含有重要位的此类集合进行划分,直至将集合划分为具体的元素。LBT系数块中存在着类似零树结构。图2中给出了模仿小波变换中树结构的LBT块变换中的零树划分方法,其中每一个线框对应着一个系数,实线则将64个系数分为10个子带。由于块变换具有集中能量的作用,系数的能量由左上到右下逐渐减少。

在每一子带中,首先使用Golomb方法编码,再将其输出码流输入到MQ编码器,进行下一步的编码。零树编码过程应用了零树结构中父子节点间的相关性,需要在已知父节点的情况下定位它的子节点。因此,在LBT系数输出后进入编码器前,利用线性索引的方法对LBT系数重新排序,将其放置在一维数组里。

2 并行多DSP+FPGA的硬件设计方案

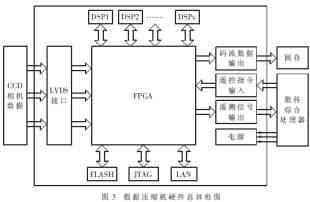

2.1 系统硬件整体框图

数据压缩系统硬件总体框图如图3所示。2x-1路串行CCD数据通过LVDS接口多路并行进入FPGA进行时序转换,每个DSP通过两个串口以EDMA方式从FPGA读取两路相机数据并缓存、压缩编码,整个数据压缩系统需要x个DSP并行处理。压缩后码流数据通过串口输出到FPGA,FPGA重新缓存、组帧、时序转换后输出到固存设备。码流数据输出、遥控指令输入、遥测信号输出和电源的接口均通过底板总线和数传综合处理器连接。

2.2 器件选择

DSP选择TMS320C6416,它是TI公司于2000年推出的一款具有C64XX系列新内核的高性能DSPs芯片。TMS320C6416采用一种高性能的先进的VLIW(非常长指令字)结构,其内部具有8个并行处理单元。因单指令字长为32位,8个指令可组成长达256位的指令包,由内部专门的指令分配模块同时分配到8个处理单元同时运行。因此在600MHz主频时,TMS320C6416的最大处理能力高达4800MIPS(百万条指令/秒)。TMS320C6416核心电压为1.2V,外围电压为3.3V,主频为400MHz"1GHz,并且在600MHz主频下,能够提供833B级器件。

FPGA选用X2V3000-5FG676C,该型号属于Xlinix公司的Virtex-II系列,300万门,676个管脚中包括484个I/O管脚。Xlinix FPGA的基本特点是由可配置逻辑块(CLB)、输入/输出块(IOB)以及可编程互连资源组成,另外还包括三态缓冲器、全局时钟缓冲器和边界扫描逻辑。CLB中包含有查找表(LUT)、寄存器和进位逻辑,IOB中包含DDR寄存器。存储器资源主要包括分布式SelectRAM/ROM以及18KB的块状SelectRAM。

2.3 接口设计

线阵CCD相机图像灰度数据以串行方式及LVDS信号电平输出。为了便于DSP串口接收,由FPGA进行电平转换,并依据相关串行协议进行时序转换。而压缩图像编码则经DSP串口输出,由FPGA进行电平转换,并依据压缩机输出接口时序进行相应的转换。

遥控机输出线有指令线、地线,在使用端上拉。指令整形输出后如需要负脉冲可再外加一级反相器或在FPGA内部实现。遥测接口分为模拟遥测、数字遥测和数据遥测三部分,模拟遥测主要针对电源(5V、1.5V、1.4V等)进行遥测,遥测输出电平为0~5V;数字遥测主要对分机中关键器件工作状态进行遥测,遥测输出电平为TTL电平;数据遥测主要对内部运行状态进行遥测。

3 压缩算法在DSP实现中的关键技术及并行处理

3.1 C6000系列CPU结构与流水线

C6000系列CPU采用哈佛结构,指令取指与执行可以并行运行。程序总线宽度为256bit,每一次取指操作都是取8条指令,成为一个取指包。取指、指令分配和指令译码都具备每周期读取并传递8条32位指令的能力。C64xx系列CPU有两个数据通路A和B,每个通路有4个功能单元(.L、.S、.M和.D),不同的8个功能单元中的指令均可并行执行。

现代微处理器把指令分成几个子操作,每个子操作在微处理器内部可由不同的部件来完成。在同一时间内,可有多条指令交迭地在不同部件内处理,这种工作方式就是“流水线”(pipeline)工作方式。TMS320C6000的特殊结构可使多个指令包(每包最多8条指令)交迭地在不同部件内处理,大大提高了微处理器的吞吐量。

3.2 数据类型转换与数据溢出问题

TMS320C6000系列DSP的数据打包处理技术,可以使用宽长度的存储器对短字长的数据访问,这样可使编译出的代码性能显著提高。压缩算法在DSP实现中,采用short代替int来存储图像像素值和变换后的系数,并确保不会产生数据溢出。

对|T|的每一行求和,最大为2.8284。进行行列两次变换,最终变换系数最大为图像像素值的8倍。当图像像素占8位或10位时,包括符号位1位,16位存储变换系数不会溢出。

3.3 并行计算

压缩算法核心软件结构如图4所示。

各子函数采用汇编语言编写,在C6000系列DSP中优化代码的关键是如何实现代码的并行。针对C64XX系列处理器的指令特点,采取以下并行处理措施:

(1)双通路。处理系数平均安排,分别分布在A、B两通路;

(2)数据打包处理技术。用LDW和STW一次读取和存储两个16位系数;

(3)半字操作指令。每条指令处理两个16位系数;

(4)多功能单元。两通路内各8个系数的计算充分利用L、S、M和D四个功能单元。

4 实验结果与结论

以一组40幅中科院遥感所提供的1024×1024×8图像为样本,用4:1和8:1两种压缩比,对遥感图像压缩系统样机进行测试。测试结果如下:

(1)压缩比为4:1时,PSNR平均40dB以上,最低38dB;压缩比为8:1时,PSNR平均35dB以上,最低32dB。

(2)对1024×1024×8图像,压缩比为4:1时,单DSP处理时间在64ms以下;压缩比为8:1时,单DSP处理时间在48ms以下,为优化前时间的1/30。

(3)单DSP内部RAM能满足2路相机数据及中间系数缓存要求;

(4)单路功耗在0.5W以下,整机功耗不足15W。

结果表明,数据压缩系统设计合理,实际工作能满足图像质量和高速实时处理要求。但从人工判图的结果看,8:1压缩时,算法小目标保持情况不如JPEG2000。系统目前已进入初样阶段,希望在算法尤其是编码算法上继续研究并优化,进一步提高图像质量。

我要赚赏金

我要赚赏金