本文将探讨半导体集成电路(LSI和IC)评估板的制作方法和电路板布局等内容。

冒昧地问一下,您喜欢制作电路板吗?

我很喜欢。电路板布局包括元器件的布置和信号线的走线等要素,其中对我来说,设计电路板布局就像玩拼图一样,思考如何让布局看起来很漂亮是一件很有趣的事。

虽是工学领域,可能不重视“美”这种感性视角,但整体俯瞰电路板得到的印象与电路板的性能是有关系的。元器件的布置是决定电路板的制作成功与否的第一个重点,也是非常重要的一点。一旦确定了元器件与元器件的位置,它们之间的布线就自然而然地确定了。在决定元器件的位置时,需要在脑海中想象重要的信号线和其他线路在电路板上如何走线。此外,在制作过程中,还需要充分发挥想象力,注意是否存在因元器件的位置而特别长的走线,以及是否有需要绕行的走线。

电路板布线的“美”是……

换句话说,是信号线和走线的井然有序。具体来讲,就是指布线的长度要短,没有奇怪的弯曲和绕行,元器件与元器件之间的走线是简洁直接的。最近,出现一种EDA工具(CAD工具),可以在输入电路板的电路图后自动生成电路板布局,不过我没用过。也许把电路板布局的工作交给工具,它会做得更完美,但对我来说,这是一项很有乐趣的工作,所以还是喜欢自己做。

电路板布局与电磁兼容性(EMC)密切相关,因此是非常重要的。

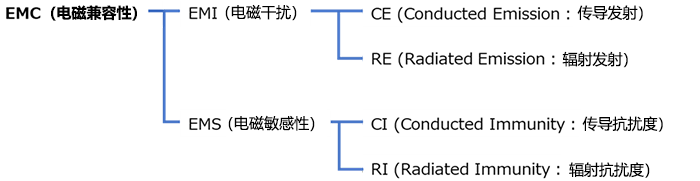

电磁兼容性(EMC)大致包括两部分,一部分是自身产生电磁噪声的电磁干扰(EMI,****),另一部分因外部电磁噪声而导致误动作或损坏的电磁敏感性(EMS,抗扰度)。另外,根据电磁噪声的传输路径又分为传导(Conducted)和辐射(Radiated)。在制作电路板时,必须考虑它们之间的四种组合,即传导****(CE: Conducted Emission)、辐射****(RE: Radiated Emission)、传导抗扰度(CI: Conducted Immunity)、辐射抗扰度(RI: Radiated Immunity)。这些术语之间的关系图如下:

制作电路板时最需要注意的是电路板的寄生电感(L)和寄生电容(C)。这是因为它们很可能会导致在高频段中的串联谐振频率和并联谐振频率处的电磁兼容性(EMC)特性变差。

那么如何通过电路板布局来改善电磁兼容性(EMC)呢?

“EMC对策元件”在各国市场上均有销售,可以使用这些产品来改善电磁兼容性,但是当使用这些产品也无法满足要求时,就需要思考对策方法,有一些方法可以参考。

对于电磁干扰(产生电磁噪声的一方),可以将电路板布线看作是电磁噪声的“****天线”。对于电磁敏感性(受电磁噪声影响而误动作的一方),可将电路板布线视为电磁噪声的“接收天线”。然后就可以比较清楚怎样布线更好。

近年来,多层电路板(比如4层)开始普及。在多层电路板中,可以看到很多是尽可能地使用电路板表面层和背面层作为完全接地面的。这是一种电路板的金属屏蔽方法,在内层创建信号线和控制线。

此外,需要尽可能地缩小电路板的尺寸。电路板越小,布线长度也就越短。这样可以减少寄生电感和电容。从同样的视角来看,元器件尺寸也尽量小的表面贴装型产品是比较理想的选择。事实上,“美”的电路板布局无外乎减少这些寄生分量。

感谢您阅读本文。

我要赚赏金

我要赚赏金