作者:Lin Wu,德州仪器 (TI) 产品市场营销经理

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI 是中断、阻碍或者降低电子器件有效性能的所有电磁干扰。其产生的方式有两种:1)通过存在于信号之间的寄生电感/电容,或者通过电源或接地连接的无用耦合,从而产生 EMI;或者2)直接通过电子/磁辐射,即辐射性 EMI。

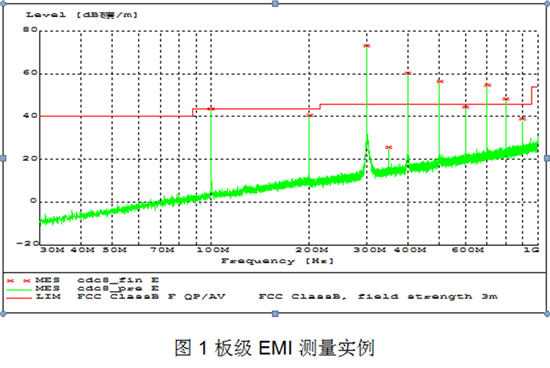

由于两个原因,时钟信号常归咎于 EMI。即使时钟低频率运行,较好的时钟上升/下降沿也包含大量的奇次谐波,其在更高频率时会引起 EMI。另外,时钟通常会在板上传播一段较长的距离,从而更可能给其他组件带来干扰。通常,EMI 可通过频谱分析仪测量,如图 1 所示。图中,绿色信号存在一些超出红色 FCC 屏蔽的频率分量(300MHz、400MHz 和 500MHz 等)。

控制时钟引起 EMI 的一些方法都基于上述两种方式:屏蔽、去耦、精心布局,以及改变时钟源特性。

屏蔽方法使用导体将 EMI 彻底包起来接地。利用这种方法,电磁能量被控制在系统内部。另外,它还使外部信号更难以将 EMI 带入系统。这种方法对传导性 EMI 和辐射性 EMI 都有效。一般而言,这种方法在保护系统的敏感部件时成本较高,并且占用空间。高频时效果较好。在 100MHz 以下时钟频率或边缘速率情况下,EMI 自屏蔽层以上时钟信号耦合,而屏蔽层本身也产生辐射。这种情况下,屏蔽的效果极其有限。一种解决方法是使用 RF 线圈。

大多数情况下,较好的去耦和精心的布局比屏蔽方法更能减少传导性 EMI。

在每个有源器件(尽可能靠近器件连接电源或接地)上安装旁路或者“去耦”电容有助于引导时钟或任何其他高频信号组件直接接地,而非干扰其他信号。至少用两个数量级,交替这些旁路电容器的值。如果可能,选择表面贴装类型。在板上给去耦组件一个占位器 (position holder) 一直都是一个不错的办法。

就您的布局而言,基本原则是让接地返回路径短一些,并最小化信号环路。使用较短的过孔组件线。尽可能地靠近 PCB 贴装组件,并将与时钟线迹相关的所有组件都靠近放置在一起。如果可以的话,请使用差分信号。实事证明,使用一个专用接地层和多层布局较为高效。但是,这会增加电路板成本。对于一些如便携式系统等成本敏感型设计而言,这样做并不可取。这些情况下,改变时钟信号本身可有效地减少 EMI 源,同时更便宜,也更灵活。

一种方法是减少信号摆动来降低峰值能量。增加串联电阻减慢时钟上升/下降沿,从而减少谐波。另一种普遍使用的方法是使用扩频时钟 (SSC),有意将时钟能量传播至更宽的频带,这样便使峰值能量降低。这种 SSC 功能被集成到大多数我们的时钟器件中。下次,我们将对其做更详细的讨论。

降低摆动或使用边缘控制的缺点是使时钟的抗噪性变差。使用 SSC 增加了时钟的抖动。就消费类电子产品而言,通常较少关注这些。但是,对于一些高精度应用而言,这些方法通常不是首选的方法。

结论

总之,降低 EMI 方法的选择涉及您的应用、时钟频率和成本/性能考虑等诸多方面。一般而言,它是所有上述方法的综合。

参考文献

《防止时钟分布电路中 EMI 的应用手册》TI,****: http://focus.ti.com/general/docs/techdocsabstract.tsp?abstractName=scaa031

如欲了解 CDCS502 的详情并获取 SSC 器件的样片,您可以登录 http://focus.ti.com/docs/prod/folders/print/cdcs502.html 下载产品说明时和其他技术文档;请登录 http://focus.ti.com/docs/prod/folders/print/cdce949.html 了解 CDCE949 详情。

作者简介

Lin Wu 现任 TI 接口和时钟产品部产品营销经理。 Lin 女士毕业于爱荷华州立大学(Iowa State University),获电子工程博士学位,现在拥有 3 项美国专利。