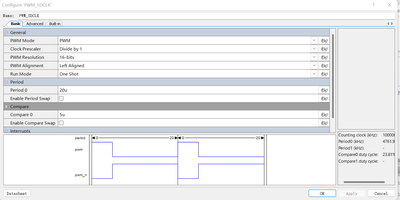

我用的芯片是CY8C6347BZI-BLD53,我设置了PWM one shot 发送 如图所示

初始化后 第一次触发 Cy_TCPWM_TriggerStart(PWM_SDCLK_HW, PWM_SDCLK_CNT_MASK )

PWM输出一直低电平,但是overflw 有溢出事件,

第一次溢出后 再TriggerStart PWM输出就正常了,这是什么问题

共2条

1/1 1 跳转至页

PSOC6PWM输出一直低电平的原因?

2楼

可能的原因有以下几个:

1. 初始化设置不正确:请确保你已经正确地配置了PWM输出的引脚和初始化寄存器。检查初始化代码以确保所有的参数都被正确地设置。

2. 时钟频率问题:有可能时钟频率设置不正确导致PWM输出不正常。请检查PWM的时钟源是否正确配置,并且时钟频率是否符合要求。

3. 周期参数设置不正确:请检查PWM的周期参数是否正确设置。如果初始化代码中的周期参数设置不正确,可能导致PWM输出一直为低电平。

4. 功能配置错误:请确定你已经正确地配置了PWM的功能模块和控制寄存器,以确保正确的功能被使能。

共2条

1/1 1 跳转至页

回复

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金

我要赚赏金