p { margin-bottom: 0.21cm; }

module dv3( output clk_out,

input clk_in,

input reset

);

reg [1:0] cnt;

reg clk_out_temp;

always @ (clk_in or reset)

begin

if(reset == 1)

begin

cnt <= 0;

clk_out_temp <= 0;

end

else if(cnt >= 2'b10)

begin

cnt <= 0;

clk_out_temp <= ~clk_out_temp;

end

else

cnt <= cnt + 1;

end

assign clk_out = clk_out_temp;

endmodule

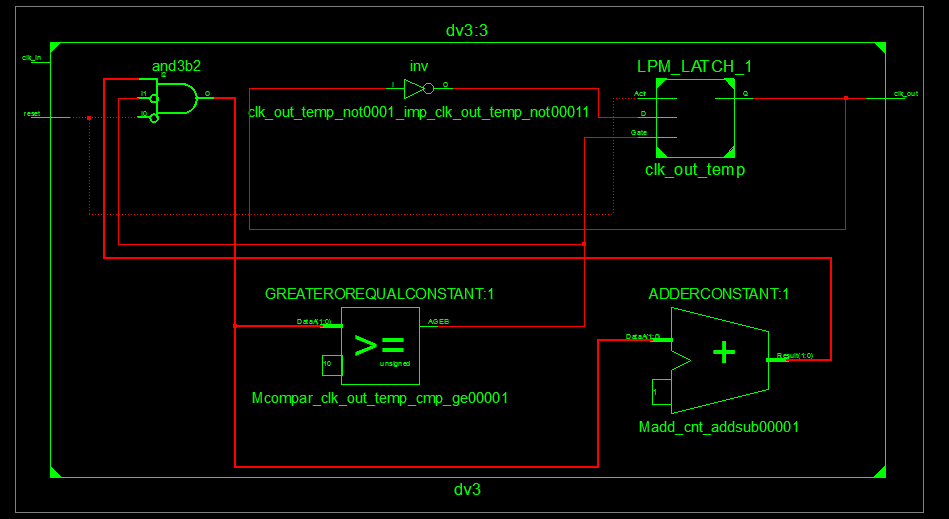

编译综合以后查看了一下RTL网表,发现不太友好:

没看见时钟到底怎么使用的,而且内部实现太没全弄明白,由于没有FPGA板子,没验证,仅仅是做了一下前仿,发现是可以实现3分频的,仿真波形如下:

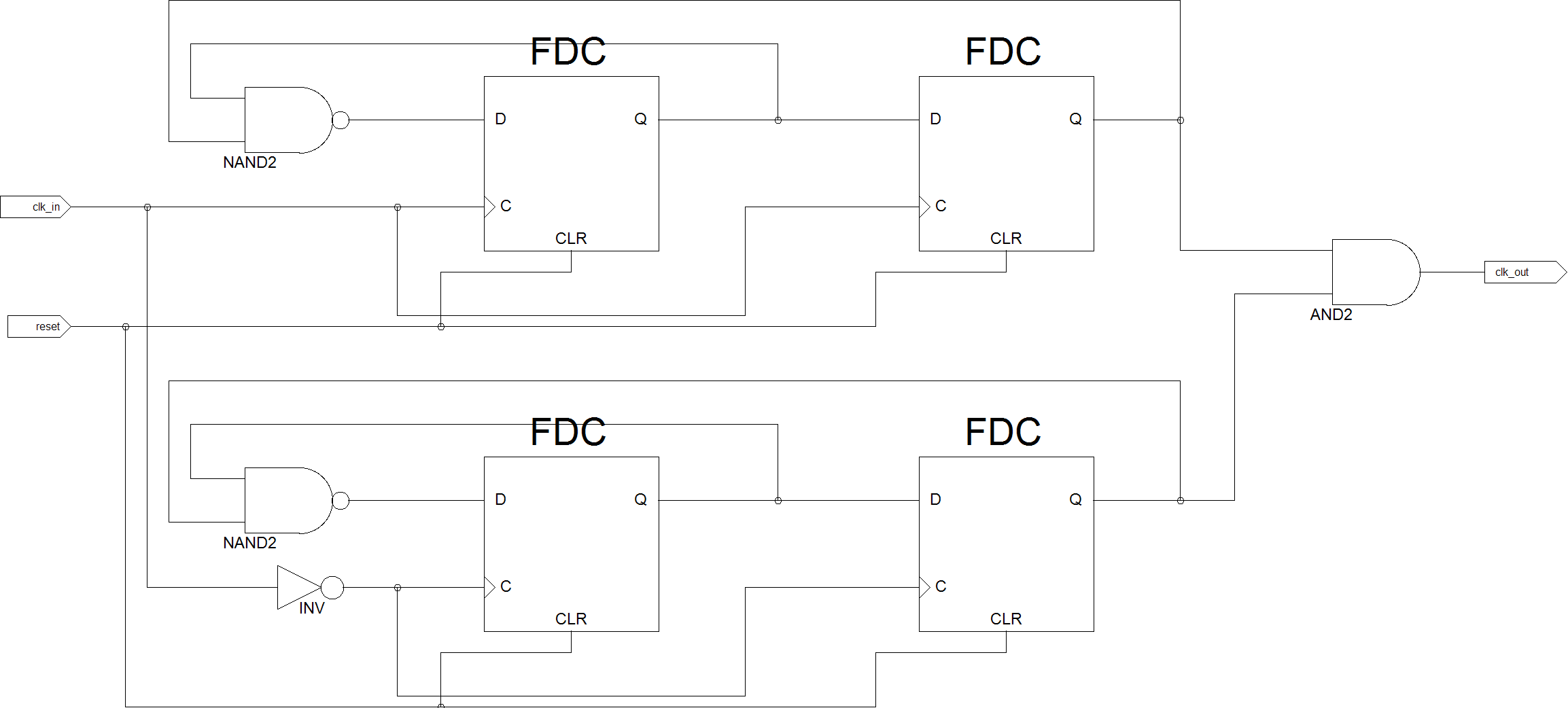

后来一次偶然机会作一个电路内部的移位寄存器处理,发现实际是可以用移位寄存器来实现3分频的,整理了一下思路,得到如下电路:

这个可以不用工具仿真,手工画以下时序图就可以得出结果啦。

后来在网上搜了一下3分频电路,发现也有用JK触发器实现的,当然,更多的是用verilog或者VHDL描述的一团糟的逻辑混乱代码,也不知道能否实现,鄙人无甚兴趣研究

其实这个思路是实现奇数分频的一个好思路,其他的如5、7、9.。。。分频,增加移位寄存器到长度即可同样实现。原理就是将时钟移位分频成占空比非50%的目标频率信号,然后用两路移相信号拼出所要的目标信号!

我要赚赏金

我要赚赏金