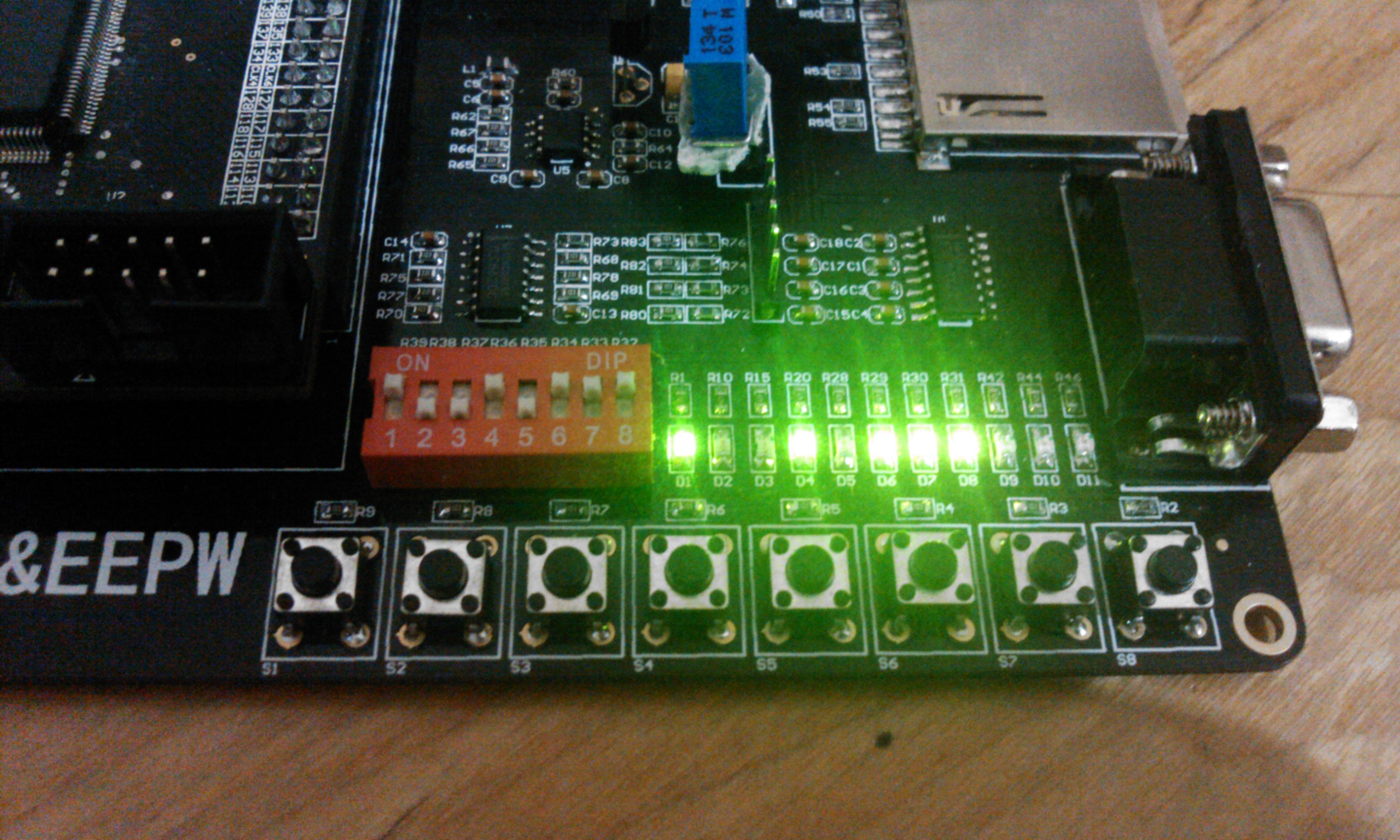

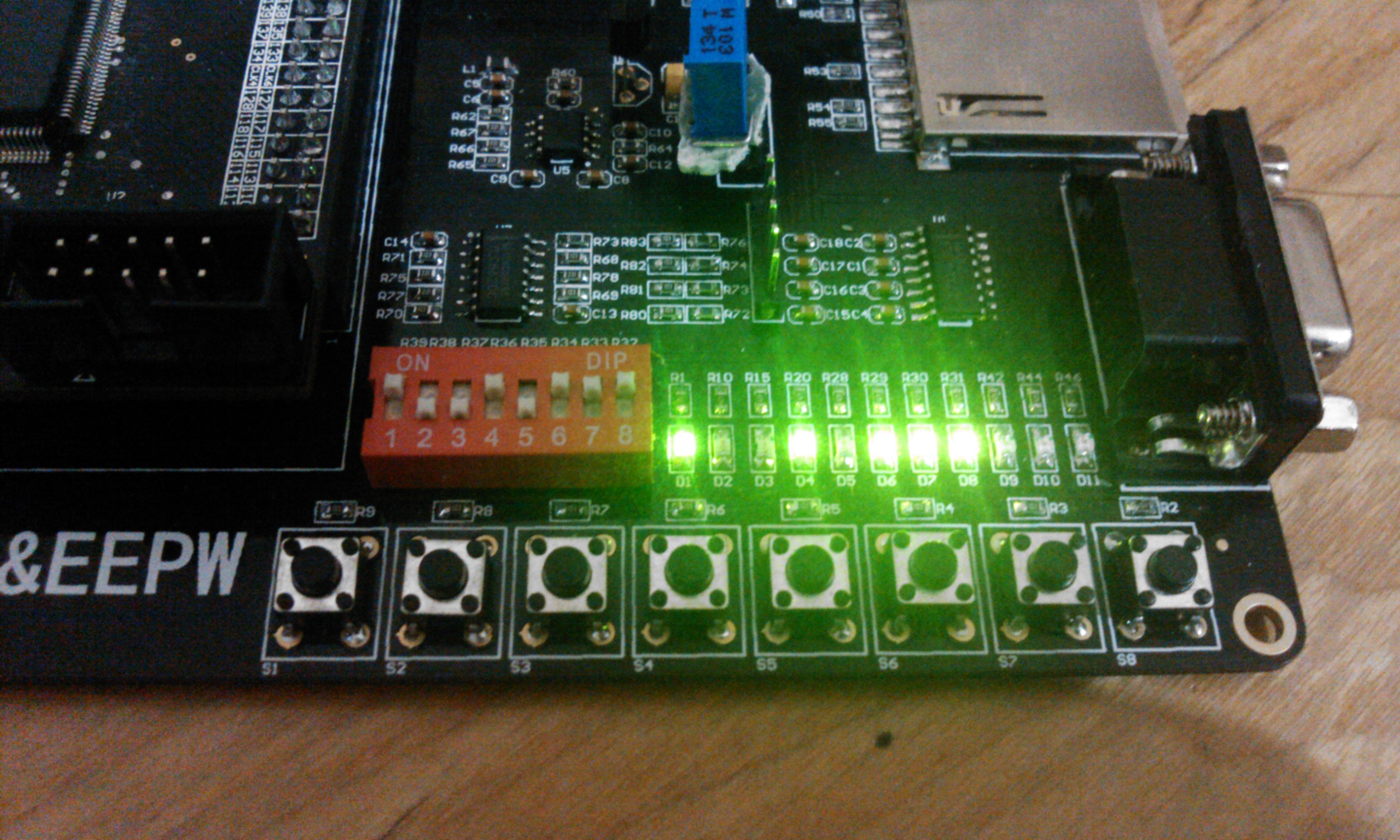

代码很简单

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LED_SW IS

PORT(

SW :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

LED :OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

end entity;

architecture one OF LED_SW IS

BEGIN

LED<=SW;

END one;

代码很简单

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LED_SW IS

PORT(

SW :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

LED :OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

end entity;

architecture one OF LED_SW IS

BEGIN

LED<=SW;

END one;

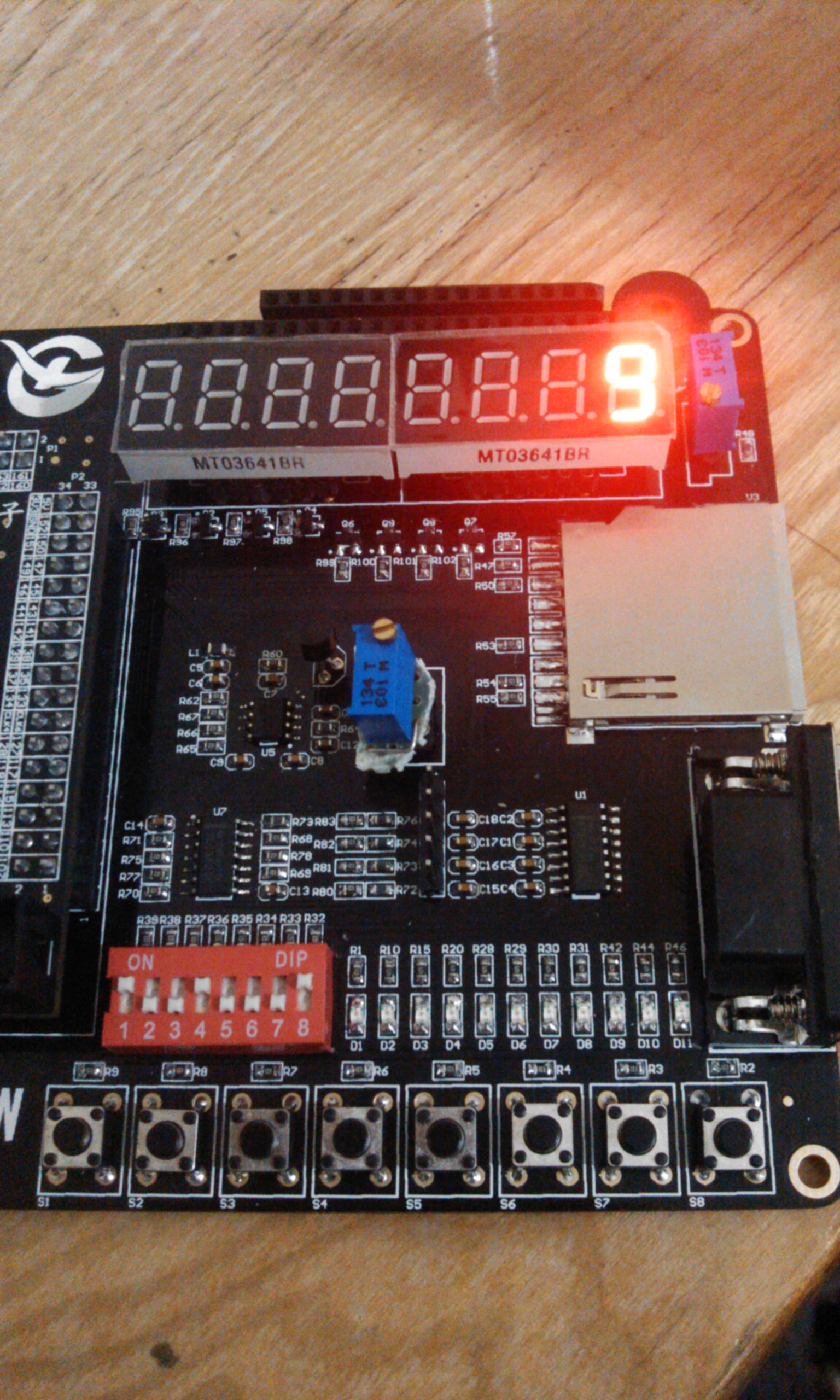

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SEG7 IS

PORT (

SW :IN STD_LOGIC_VECTOR(3 DOWNTO 0);

EN :IN STD_LOGIC;

SEG :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

DIG :OUT STD_LOGIC

);

END ENTITY;

ARCHITECTURE ONE OF SEG7 IS

BEGIN

PROCESS(SW)

BEGIN

CASE SW IS

WHEN "1111" => SEG <= "11000000";--0

WHEN "1110" => SEG <= "11111001";--1

WHEN "1101" => SEG <= "10100100";--2

WHEN "1100" => SEG <= "10110000";--3

WHEN "1011" => SEG <= "10011001";--4

WHEN "1010" => SEG <= "10010010";--5

WHEN "1001" => SEG <= "10000010";--6

WHEN "1000" => SEG <= "11111000";--7

WHEN "0111" => SEG <= "10000000";--8

WHEN "0110" => SEG <= "10010000";--9

WHEN "0101" => SEG <= "11001000";--A

WHEN "0100" => SEG <= "10000011";--B

WHEN "0011" => SEG <= "11000110";--C

WHEN "0010" => SEG <= "10100001";--D

WHEN "0001" => SEG <= "10000110";--E

WHEN "0000" => SEG <= "10001110";--F

WHEN OTHERS => SEG <= "11111111";--

END CASE;

END PROCESS; --enable

DIG<=EN;

END ONE;

| 有奖活动 | |

|---|---|

| 2026年“我要开发板活动”第三季,开始了! | |

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| PTC与NTC功能常规对比被打赏¥14元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于3pin锂电池接口的介绍/使用被打赏¥16元 | |

| 以启明云端ESP32P4开发板实现TF卡读写功能被打赏¥28元 | |

| 【分享开发笔记,赚取电动螺丝刀】树莓派5串口UART0配置被打赏¥25元 | |

| 【STM32F103ZET6】17:分享在Rtos项目中断管理的使用经验被打赏¥23元 | |

| 【STM32F103ZET6】16:分享在中断中恢复串口任务,遇到的问题被打赏¥31元 | |

| 在FireBeetle2ESP32-C5上实现温度大气压检测及显示被打赏¥21元 | |

| 【分享开发笔记,赚取电动螺丝刀】SAME51双串口收发配置被打赏¥27元 | |

| Chaos-nano操作系统在手持式VOC检测设备上的应用被打赏¥37元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于在导入第三方库lib时,wchart类型冲突的原因及解决方案被打赏¥30元 | |