好的,谢谢大老王。嘿嘿。

led_display实验一作业:拨码开关进行八进制数显示。led_key.zip

代码:

module led_key(sys_clk,key,sm_seg,sm_bit);

//输入输出信号

input sys_clk; //全局时钟 50Mhz

input[7:0] key; //按键输入

output[7:0] sm_seg;//数码管段码

output[7:0] sm_bit;//数码管位码

//寄存器定义

reg[7:0] sm_seg;//数码管段码输出寄存器

wire[7:0] sm_bit;//数码管位码输出寄存器

reg[3:0] key_dat;//显示数据寄存器

//*wire型数据常用来表示以assign为关键字组合逻辑信号,reg型为寄存器数据类型,常用来表示always模块内指定信号,常代表触发器。*/

//逻辑部分

always@(posedge sys_clk or negedge key )

begin

case (key)

8'hff:key_dat=4'h0;

8'hfd:key_dat=4'h1;

8'hfb:key_dat=4'h2;

8'hf7:key_dat=4'h3;

8'hef:key_dat=4'h4;

8'hdf:key_dat=4'h5;

8'hbf:key_dat=4'h6;

8'h7f:key_dat=4'h7;

endcase

end

always@(key_dat)

begin

case (key_dat)

4'h0:sm_seg=8'hf9;//"1"

4'h1:sm_seg=8'ha4;//"2"

4'h2:sm_seg=8'hb0;//"3"

4'h3:sm_seg=8'h99;//"4"

4'h4:sm_seg=8'h92;//"4"

4'h5:sm_seg=8'h82;//"6"

4'h6:sm_seg=8'hf8;//"7"

4'h7:sm_seg=8'h80;//"8"

endcase

end

/*begin...end类似于C语言里面的{}*/

assign sm_bit=8'b00000000 ;

endmodule

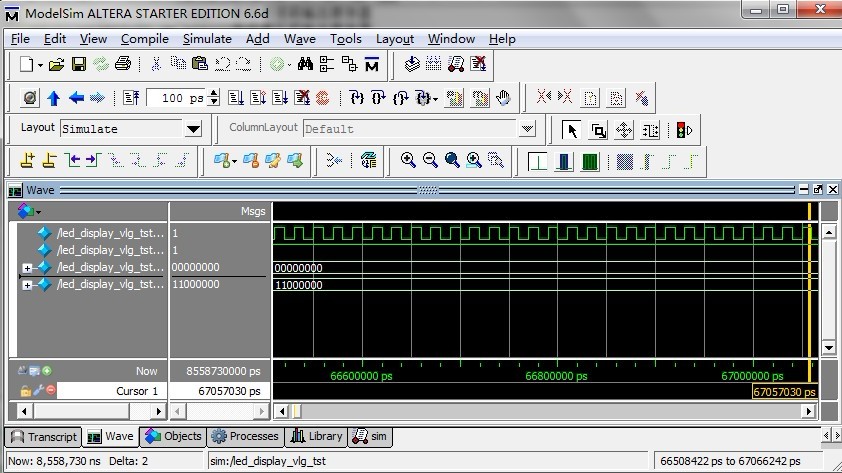

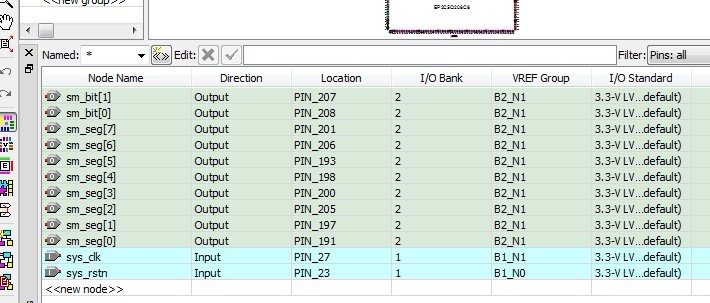

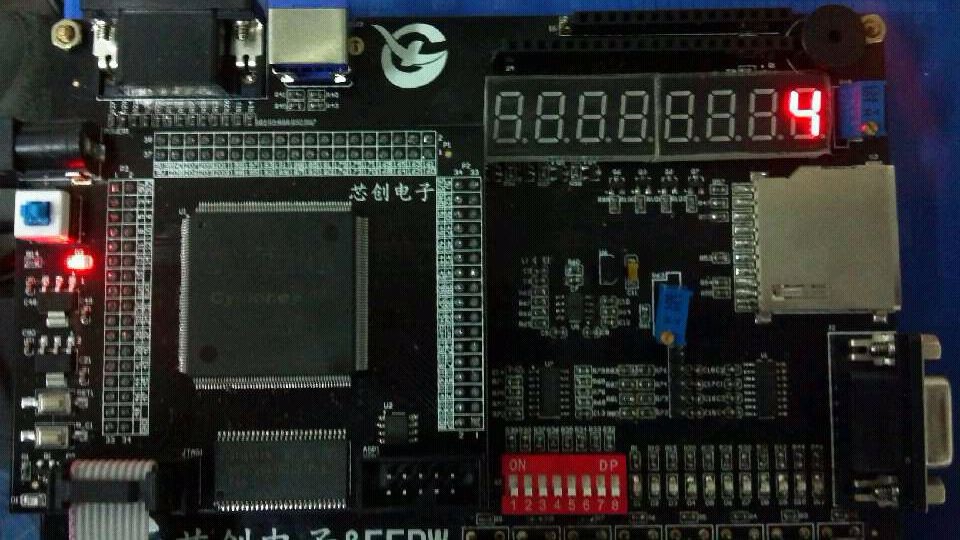

作业:模60的计数器。

module led_60cnt(sys_clk,sys_rstn,sm_seg,sm_bit);

//输入输出端口

input sys_clk;//50Mhz时钟

input sys_rstn;//复位信号

output [7:0] sm_seg;//数码管段码

output [1:0] sm_bit;//数码管位码

//寄存器定义

reg[7:0] sm_seg;//数码管段码输出寄存器

reg[1:0] sm_bit;//数码管位码输出寄存器

reg[25:0] delay_1S;//1s的延时计数器

reg[15:0] scan_1kHz;//short 1khz扫描

reg disp_dat;//位选计数器

reg[3:0] unit;//个位

reg[3:0] decade;//十位

reg[4:0] data_buf;//数据位

//初始化

/*initial

begin

delay_1S<=26'd0;

scan_1kHz<=16'd0;

disp_dat<=4'd0;

unit<=4'd0;

decade<=4'd0;

end

*/

//逻辑部分

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

unit<=4'h0;

decade<=4'h0;

end

else

begin

if(delay_1S==26'd49999999)

begin

unit<=unit+1'h1;

if(unit==4'h9)

begin

unit<=4'h0;

decade<=decade+1'b1;

if(decade==4'h5)

begin

decade<=4'h0;

end

end

end

else

begin

unit<=unit;

decade<=decade;

end

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_1S<=26'd0;

else

begin

if(delay_1S==26'd49999999)

delay_1S<=26'd0;

else delay_1S<=delay_1S+1'b1;

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

scan_1kHz<=16'd0;

else

begin

if(scan_1kHz==16'd49999)

scan_1kHz<=16'd0;

else scan_1kHz<=scan_1kHz+1'b1;

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

disp_dat<=1'd0;

end

else

begin

if(scan_1kHz==16'd49999)

disp_dat<=disp_dat+1'b1;

else

disp_dat<=disp_dat;

end

end

always@(disp_dat)

begin

case(disp_dat)

1'b0:sm_bit=2'b10;

1'b1:sm_bit=8'b01;

default:sm_bit=8'hfb;

endcase

end

always@(sm_bit)

begin

case(sm_bit)

2'b10:data_buf=unit;

2'b01:data_buf=decade;

endcase

end

always@(data_buf)

begin

case(data_buf)

4'h0:sm_seg=8'hc0;//"0"

4'h1:sm_seg=8'hf9;//"1"

4'h2:sm_seg=8'ha4;//"2"

4'h3:sm_seg=8'hb0;//"3"

4'h4:sm_seg=8'h99;//"4"

4'h5:sm_seg=8'h92;//"4"

4'h6:sm_seg=8'h82;//"6"

4'h7:sm_seg=8'hf8;//"7"

4'h8:sm_seg=8'h80;//"8"

4'h9:sm_seg=8'h90;//"9"

4'ha:sm_seg=8'h88;//"a"

4'hb:sm_seg=8'h83;//"b"

4'hc:sm_seg=8'hc6;//"c"

4'hd:sm_seg=8'ha1;//"d"

4'he:sm_seg=8'h86;//"e"

4'hf:sm_seg=8'h8e;//"f"

default: sm_seg=8'h00;

endcase

end

endmodule

按键篇:作业一 按键控制数码管0~9显示

这次作业是基于led_display改的,参考版主的按键程序,没有消抖,按键每次按下去不能正确的出现数字。

代码:

module led_8key(sys_clk,sys_rstn,key_in,sm_seg,sm_bit);

//输入输出信号

input sys_clk; //全局时钟 50Mhz

input sys_rstn; //复位信号

input key_in; //按键输入

output[7:0] sm_seg;//数码管段码

output[7:0] sm_bit;//数码管位码

//寄存器定义

reg[7:0] sm_seg;//数码管段码输出寄存器

wire[7:0] sm_bit;//数码管位码输出寄存器

reg[3:0] disp_dat;//显示数据寄存器

/*wire型数据常用来表示以assign为关键字组合逻辑信号,reg型为寄存器数据类型,常用来表示always模块内指定信号,常代表触发器。*/

//逻辑部分

/*begin...end类似于C语言里面的{}*/

initial

disp_dat<=4'd0;

always@(posedge sys_clk or negedge sys_rstn)always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

disp_dat<=4'd0;

else

if(!key_in)

begin

disp_dat<=disp_dat+1'd1;

if(disp_dat==4'h9)

disp_dat<=4'h0;

end

else

disp_dat<=disp_dat;

end

always@(disp_dat)

begin

case(disp_dat)

4'h0:sm_seg=8'hc0;//"0"

4'h1:sm_seg=8'hf9;//"1"

4'h2:sm_seg=8'ha4;//"2"

4'h3:sm_seg=8'hb0;//"3"

4'h4:sm_seg=8'h99;//"4"

4'h5:sm_seg=8'h92;//"4"

4'h6:sm_seg=8'h82;//"6"

4'h7:sm_seg=8'hf8;//"7"

4'h8:sm_seg=8'h80;//"8"

4'h9:sm_seg=8'h90;//"9"

default: sm_seg=8'hff;

endcase

end

assign sm_bit=8'b1111_1110;

endmodule

//输入输出信号

input sys_clk; //全局时钟 50Mhz

input sys_rstn; //复位信号

input key_in; //按键输入

output[7:0] sm_seg;//数码管段码

output[7:0] sm_bit;//数码管位码

output led_out;

//寄存器定义

reg[7:0] sm_seg;//数码管段码输出寄存器

wire[7:0] sm_bit;//数码管位码输出寄存器

reg[3:0] disp_dat;//显示数据寄存器

reg[19:0] delay_cnt;

wire key_scan;

wire key_low;

reg key_samp;

reg key_samp_r;

reg key_rst;

reg key_rst_r;

reg led_out;

/*wire型数据常用来表示以assign为关键字组合逻辑信号,reg型为寄存器数据类型,常用来表示always模块内指定信号,常代表触发器。*/

//逻辑部分

/*begin...end类似于C语言里面的{}*/

initial

disp_dat<=4'd0;

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_samp<=1'b1;

else key_samp<=key_in;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_samp_r<=1'b1;

else

key_samp_r<=key_samp;

end

assign key_scan=key_samp_r&(~key_samp);

//延时20ms

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt<=20'h0;

else

if(key_scan)

delay_cnt<=20'h0;

else

delay_cnt<=delay_cnt+1'b1;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_rst<=1'b1;

else if (delay_cnt==20'hfffff) //约20ms

key_rst<=key_in;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_rst_r<=1'b1;

else key_rst_r<=key_rst;

end

assign key_low=key_rst_r&(~key_rst);

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

disp_dat<=4'd0;

led_out<=1'd1;

end

else

if(key_low)

begin

led_out<=~led_out;

if(disp_dat==4'h9)

disp_dat<=4'h0;

else

disp_dat<=disp_dat+1'd1;

end

else

begin

disp_dat<=disp_dat;

led_out<=led_out;

end

end

always@(disp_dat)

begin

case(disp_dat)

4'h0:sm_seg=8'hc0;//"0"

4'h1:sm_seg=8'hf9;//"1"

4'h2:sm_seg=8'ha4;//"2"

4'h3:sm_seg=8'hb0;//"3"

4'h4:sm_seg=8'h99;//"4"

4'h5:sm_seg=8'h92;//"4"

4'h6:sm_seg=8'h82;//"6"

4'h7:sm_seg=8'hf8;//"7"

4'h8:sm_seg=8'h80;//"8"

4'h9:sm_seg=8'h90;//"9"

default: sm_seg=8'hff;

endcase

end

assign sm_bit=8'b1111_1110;

endmodule

基本上根据版主的代码改的,我还需要消化哈。消抖后的确效果很好。led等和数码管同时提示按键效果。

回复

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| Chaos-nano操作系统在手持式VOC检测设备上的应用被打赏¥37元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于在导入第三方库lib时,wchart类型冲突的原因及解决方案被打赏¥30元 | |

| 在FireBeetle2ESP32-C5上实现温湿度检测和显示被打赏¥20元 | |

| 在FireBeetle2ESP32-C5上实现光照强度检测及显示被打赏¥21元 | |

| 以FireBeetle2ESP32-C5实现数据识读播报被打赏¥19元 | |

| 【STM32F103ZET6】14:实测STM32F1的串口输出任务的挂起与恢复功能被打赏¥27元 | |

| Chaos-nano在压力容器监控系统中的项目应用被打赏¥23元 | |

| 基于FireBeetle2ESP32-C5的WS2812B彩色灯带控制被打赏¥21元 | |

| SWM221CBT7显示开发板驱动TFT显示屏被打赏¥19元 | |

| SWM221CBT7显示开发板驱动OLED屏显示被打赏¥19元 | |