【内容目录】

1.电子封装简

2.早期封装类型

3.2D: 倒装芯片封装

4.2D:晶圆级封装

5.先进封装的兴起

6.2.1D/2.3D:超薄有机中介层

7.2.5D: 硅中介层、微凸点、硅通孔与硅桥

8.3D-IC封装

9.混合键合

2.1D/2.3D: 超薄有机中介层(Interposer)

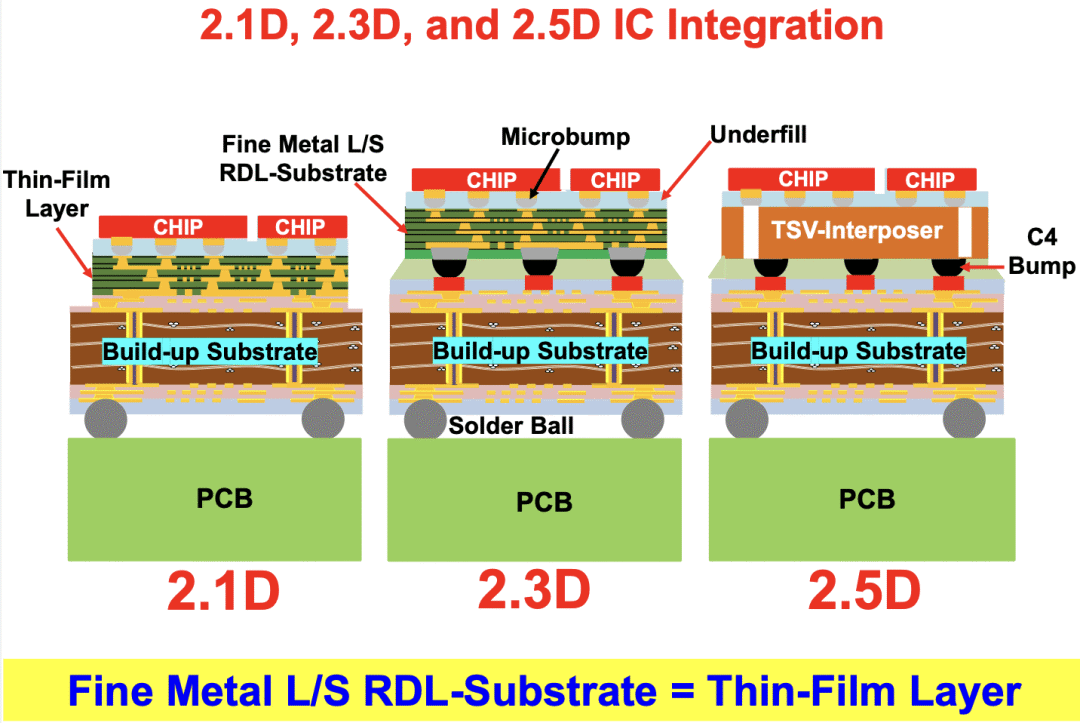

到目前为止,我们已经了解了如何将芯片翻转焊接到具有 FR4 核心和有机介电薄膜的封装基板上,也看过基于 RDL的晶圆级封装技术。所谓2.1D/2.3D 封装技术,是将 Flip-Chip 与类似 RDL 的工艺相结合的一种中间形态。有些通过晶圆级 RDL 工艺连接多个芯粒、并采用精细 L/S(金属线宽/间距)结构的方案,也被归为 2.1D 封装。

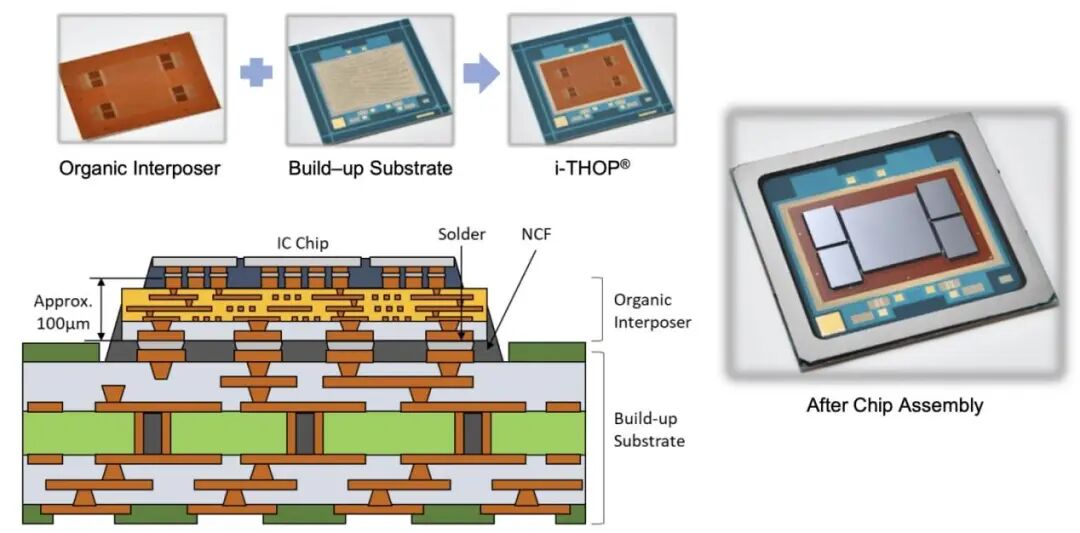

i-THOP (集成薄膜高密度有机封装) (图片来源:SHINKO)

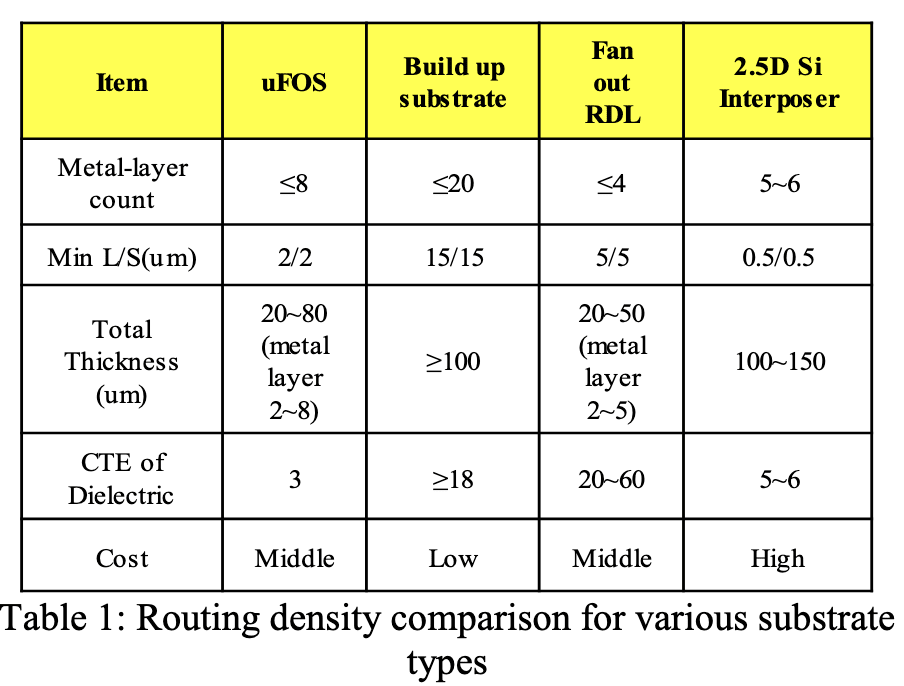

这里提到的类似 RDL 的层是一种超薄无芯基板,使用聚酰亚胺(Polyimide)类有机材料制成,可在其中制造出多达 8-10 层的金属互连。这类基板的典型代表包括SHINKO 的 i-THOP 封装和JCET 的超精细间距有机基板(uFOS)。其主要优势是可在所有金属层上实现精细的布线,典型 L/S 可达 2/2 微米。这对于那些采用先进工艺节点制造、需要在极小面积内完成大量互连的芯片尤为有利。

这些中介层通过焊球或铜柱与下方的ABF 介质 + FR4 核心基板连接,相较于我们之前介绍的2D封装结构,能提供更多的布线层次与更强的信号路由能力。

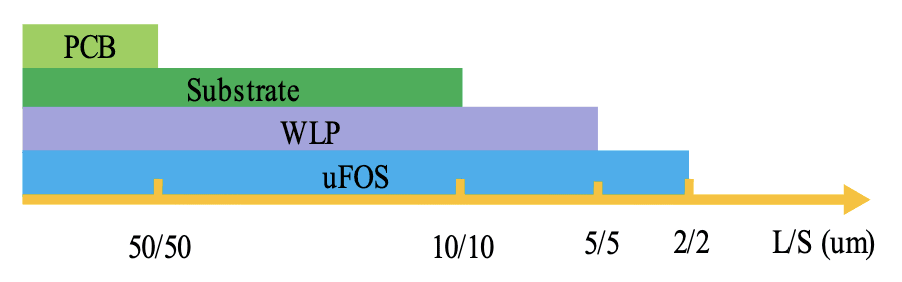

各种封装技术中的线宽/间距特征尺寸

2.1D / 2.3D这类命名主要表明了介于传统 2D与2.5D(采用硅中介层)封装之间的技术。实际上,并没有严格的界限来区分 2.1D 与 2.3D,很大程度上它只是业界采用的营销术语。

2.5D:硅中介层、微凸点、硅通孔(TSV)与硅桥(Bridge)

如果想在封装上进一步缩小金属线宽/间距,以实现更高密度的互连,就必须放弃有机中介层,进入最擅长制造微小结构的地方,硅晶圆厂(silicon foundry)。

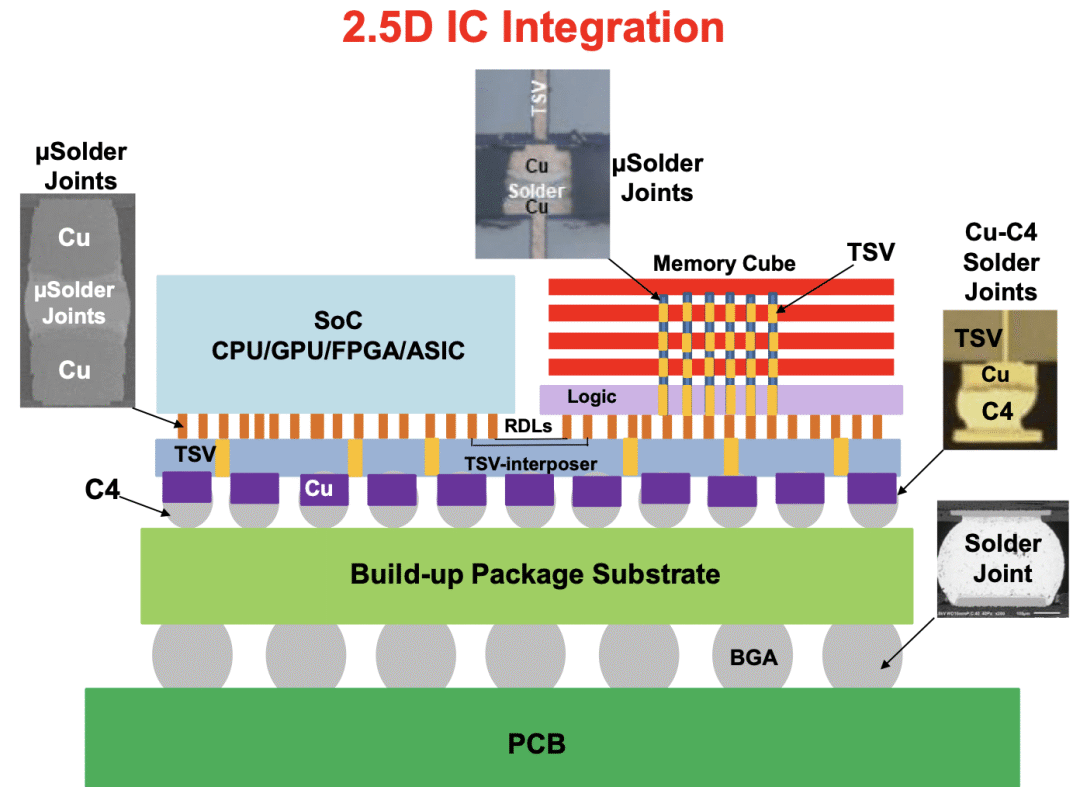

2.5D通常指一个包含了有源芯片和无源硅基板的封装结构。硅基板上没有晶体管等有源电路,只利用硅后段制程(back-end-of-line, BEOL)进行金属布线,因此比传统 2D 多出0.5D。

本节我们将讨论两种 2.5D 封装:硅中介层(Silicon Interposer)与多芯片硅桥(Multi-die Bridge),并介绍相关互连技术,包括微凸点(Micro-bump)与硅通孔(Through-Silicon Via, TSV)

硅中介层

中介层是在硅晶圆上使用硅后段制程工艺构建的,用于通过金属互连重新分布信号。虽然硅中介层上不集成晶体管,但可以集成电容等无源元件(例如旁路电容),类似的做法在有机中介层上也可实现。

硅中介层的三大优势包括:

1.精细特征尺寸:在硅中介层上,L/S 可缩至0.5/0.5 微米,能实现极高密度的互连,用于芯粒集成。

2.相匹配的热膨胀系数:与采用聚合物或有机材料的封装不同,硅中介层与芯片的 CTE 完全匹配,因此在封装过程中不易出现翘曲、应力或变形问题。

3.硅通孔集成:通过硅通孔可将中介层的上下两面直接互连,实现最短的电连接路径,从而大幅降低信号延迟与功耗。

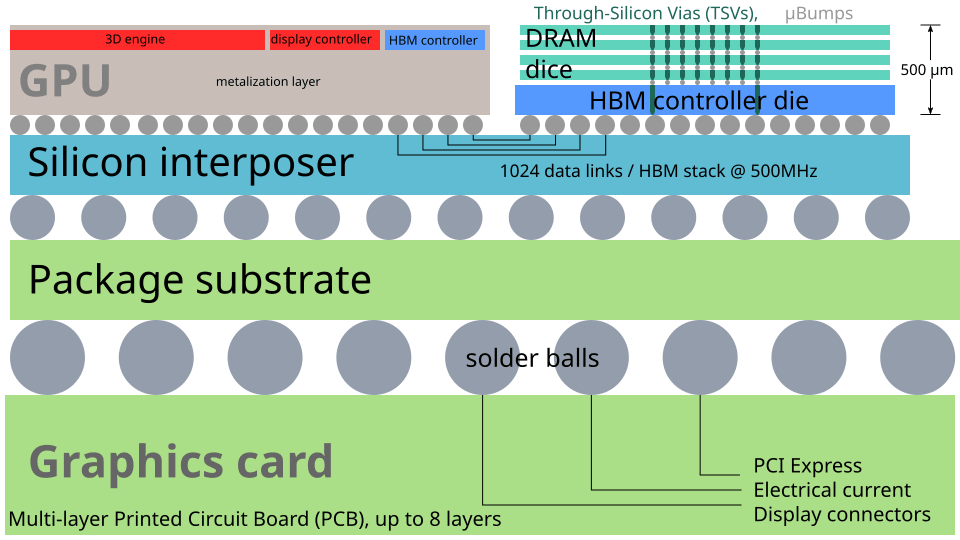

芯片封装中的硅中介层

硅中介层的局限

硅中介层的主要限制是成本高昂。硅中介层需要使用晶圆厂设备,即使仅用于简单的金属工艺,设备投资也十分昂贵,因此目前主要由英特尔、台积电、三星等 IDM 与晶圆代工厂生产。OSAT通常不自行制造硅中介层,只负责后续其与芯片的封装组装。

硅中介层的另一个限制是尺寸受光罩限制。在 12 英寸晶圆上,单个光罩的最大曝光面积约为858 mm²。若要制造更大的中介层,就必须使用光罩拼接(reticle stitching)技术,这会显著增加成本。不过,目前主要晶圆厂已能在晶圆的 X、Y 方向实现高精度拼接,并量产多种超大尺寸中介层。

玻璃中介层(Glass Interposer)现在正在成为一种新的选择。玻璃成本更低、CTE 较小,并且可在矩形面板(如 600×600 mm)上加工,不像硅晶圆那样受限于圆形晶圆。这与前面提到的面板级封装(PLP)类似,可有效降低单片成本。

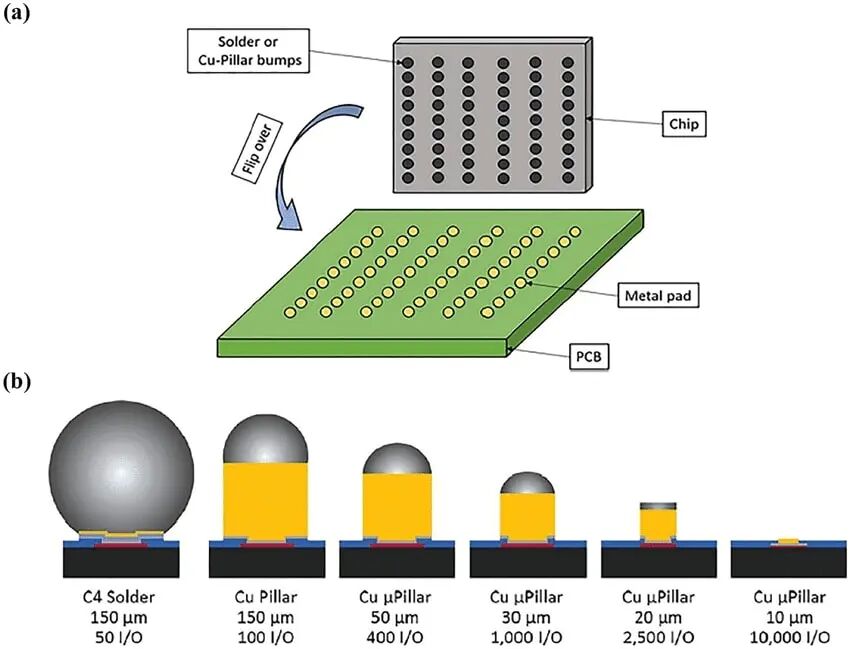

微凸点

硅中介层上的金属互连极为精细,芯片需要采用更细间距的凸点技术,即微凸点技术。通过缩小焊球直径,微凸点的间距可降至低于90 µm。常见中介层使用50 µm间距,而最先进的技术可做到10 µm 或更小。下图展示了焊锡-铜微凸点结构及不同间距下每平方毫米可实现的凸点数量。

(图片来源:Techlevated)

硅通孔

传统封装通常从芯片顶部的金属层引出信号,通过焊球、铜柱或 RDL接出。TSV 则允许从芯片底部贯穿硅片建立连接,在多种场景下,这种方法都极为有用。

最具代表性的应用是广泛用于 AI 加速器中的高带宽内存(HBM)。它垂直堆叠多层 DRAM 芯片,并用微凸点实现互连。每层 DRAM 芯片内部都有 TSV,可连接上下层芯片。

HBM 通常可堆叠8–16 层 DRAM,单层芯片厚度仅50–100 µm。最新一代HBM的 TSV 直径可达5 µm(纵横比 10:1),间距 30–50 µm,可提供大量并行通道,从而实现高带宽。

硅中介层中也可以加入 TSV,用于实现芯片与基板之间最短的电路径。中介层厚度通常为100–150 µm,TSV 直径为几十µm,以保持适当的纵横比。TSV 间距约20–100 µm。在 2.5D 与 3D 封装中,TSV 负责为上层芯片供电并引出信号,尽管尺寸缩小时会增加一些串联电阻。

最先进的 TSV 技术是用于背面供电网络(Backside Power Delivery Network)的纳米级TSV(nTSV)。

例如:

· 英特尔PowerVia 技术:在晶圆背面构建供电网络,以厚金属层降低电阻损耗。

· 台积电Backside Power Rail (BPR):采用类似概念,通过 nTSV 建立背面电源轨。nTSV间距可达5 µm 以下,直径甚至小于 1 µm,代表了 TSV 技术的最前沿。

TSV 的关键步骤是深反应离子刻蚀(DRIE),又称Bosch 工艺,包含交替的刻蚀/钝化步骤,用以在硅中形成深孔。该工艺成本高、时间长,这使 TSV制造成为制造环节中昂贵的一环。

根据工艺顺序,TSV有三种制造方法:

· TSV Last:在整个芯片完成后形成,常用于 CMOS 图像传感器。

· TSV Middle:在有源器件完成后、后段金属互连前形成,常见于 3D IC 封装。

· TSV First:在硅基板上早早形成,适用于硅中介层制造。

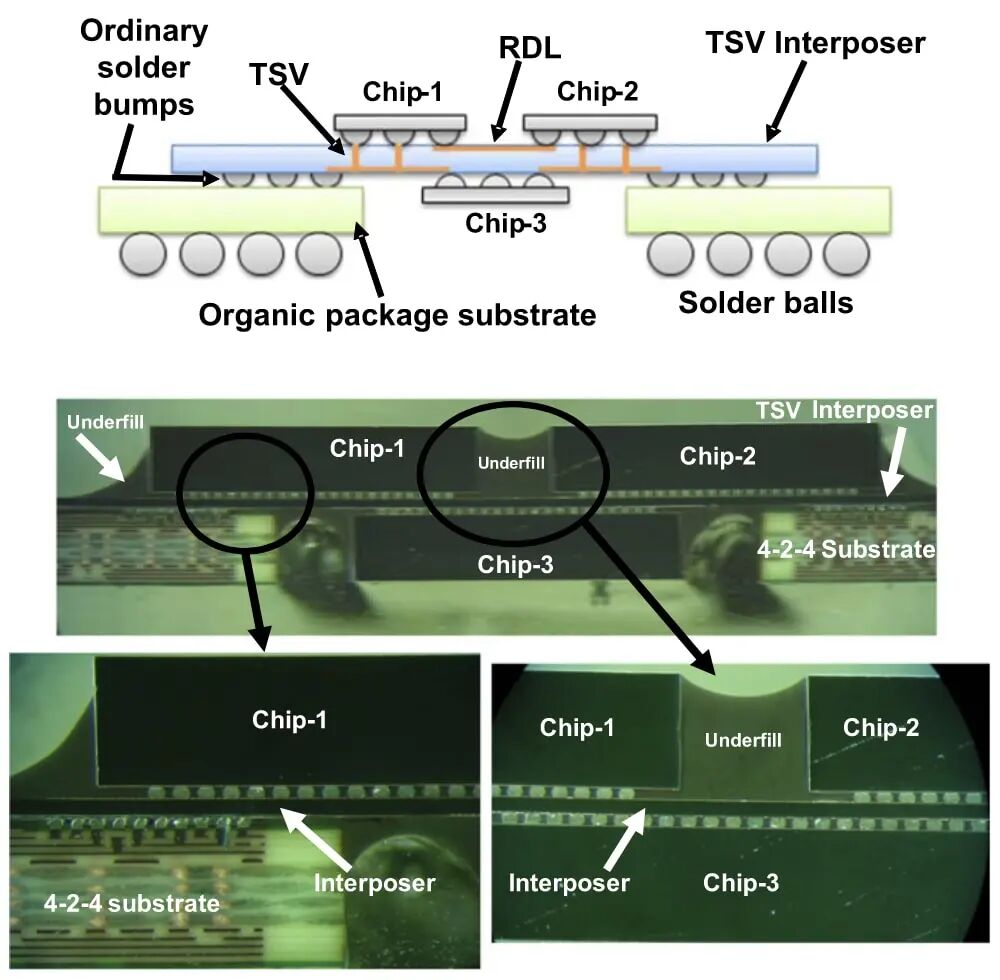

此外,带有 RDL 和 TSV 的硅中介层还能在两面同时集成芯片,从而实现更高的系统集成度。

具有双面有源芯片连接的 3D 硅中介层的工艺集成

硅桥

硅中介层的成本高、尺寸受限于光罩面积,这限制了中介层可连接芯片的总面积,使其在许多先进封装应用中并非最优方案。硅桥则是一种结合了硅中介层与有机叠层基板优势的封装方式。

目前,很多晶圆厂及多家封装代工厂均提供各自版本的硅桥技术,虽名称不同,但原理类似。

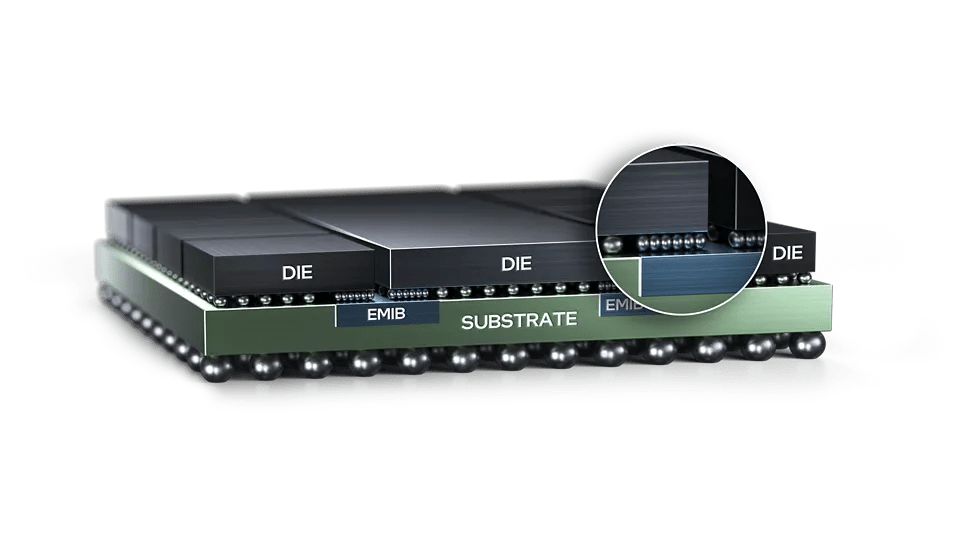

硅桥是一种微缩版中介层,通常不含 TSV以降低成本(部分版本仍带 TSV)。

它被嵌入到有机基板预制的腔体中,上方再组装芯片,相邻芯片之间的横向互连通过硅桥完成。每个硅桥仅放置在基板或有机中介层中晶粒之间的互连区域,因此整体占用面积很小。位于桥接区域之外的芯片可以直接通过基板通孔或铜柱进行连接,电阻远低于硅中介层的TSV。

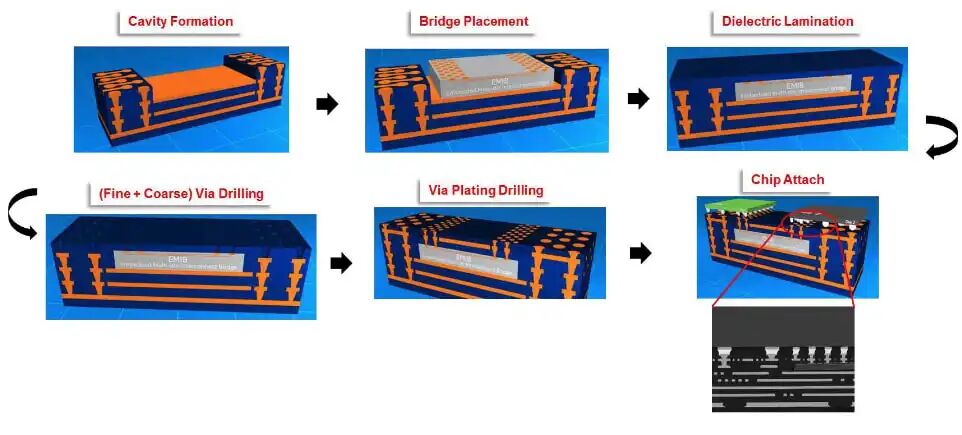

以英特尔的嵌入式多芯片互连桥(EMIB, Embedded Multi-die Interconnect Bridge) 为例,其工艺流程如下:

1.在晶圆厂中使用后段工艺制造硅桥,减薄并切割待用;

2.有机封装基板进行常规叠层工艺,直到最后一层;

3.在基板上蚀出腔体,用于放置硅桥;

4.将硅桥嵌入腔体中,并完成最终介电层的叠层;

5.在介电层上钻出细通孔(用于芯片与硅桥互连),在其他区域钻出较大通孔,随后进行金属化和平整化处理;

6.最后即可用于倒装芯片连接,从而连接多个需要桥接的硅芯片。

与硅中介层相比,硅桥的主要优势包括:

· 成本低

· 模块化灵活性高,不受光罩面积限制,尺寸小,仅用于连接多个芯粒的I/O接口,无需昂贵的光罩拼接工艺。

· 连接面积无限制,理论上可嵌入多个硅桥,只要基板或有机中介层支持即可。随着现代 CPU/GPU 在单封装中集成更多芯粒与 HBM,硅桥技术的应用正迅速增长。

英特尔EMIB 2.5D 封装技术(来源:Intel)

3D-IC 封装

前文讨论了利用不同封装技术将多个芯片并排互连的方法,我们通常称之为2D或2.5D 集成。封装技术的下一个发展方向是将芯片垂直堆叠,也就是所谓的3D IC 封装。其主要优势是缩小封装占板面积、缩短横向互连长度,从而降低功耗,以及实现异构集成。在 HBM中,我们已经看到通过微凸点与 TSV堆叠晶粒的实例。而3D-IC 封装则在此基础上更进了一步,垂直堆叠具备不同功能的硅芯片。

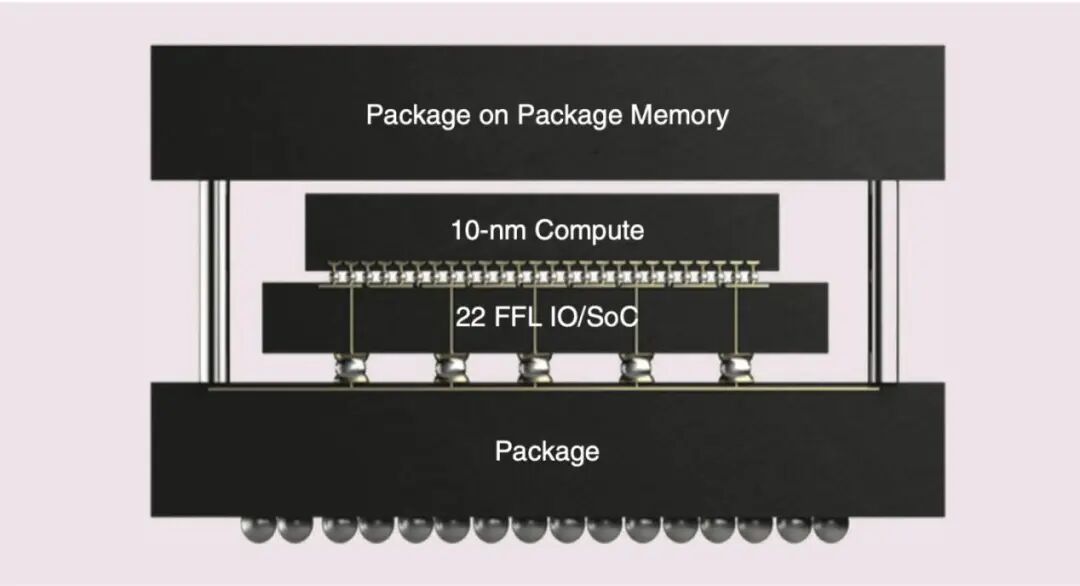

以英特尔为例,2019 年,英特尔在 Lakefield 移动处理器上首次展示其 3D 堆叠技术 Foveros,这是业界首个商用的逻辑芯片叠逻辑芯片堆叠方案。其顶层晶粒采用英特尔10 nm 工艺节点,包含计算核心;底层晶粒采用低功耗 22 nm FinFET 工艺节点,集成 PCIe、USB、安全单元及其他低功耗 I/O 模块;封装顶部还集成了一个通过焊球连接的 DRAM 模组。

英特尔 Lakefield 3D 集成与 Foveros 技术

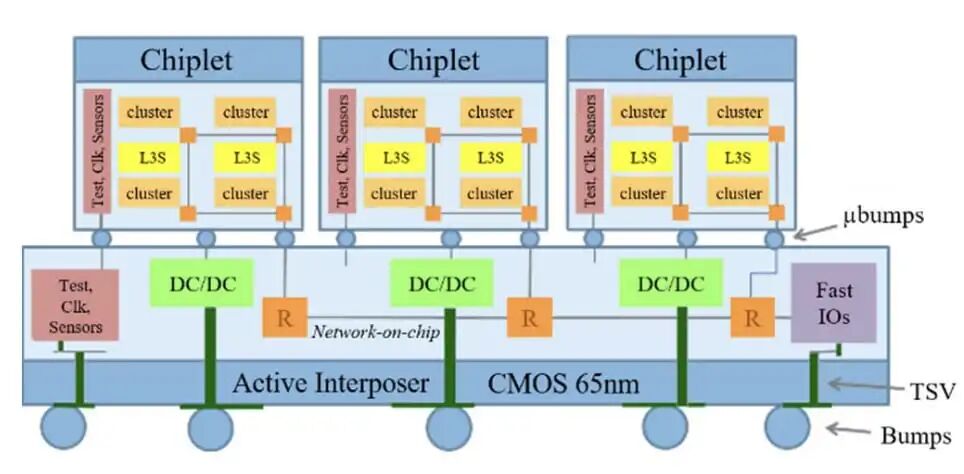

除了直接堆叠完整的芯片,另一种折中的 3D 集成方式是使用有源中介层。这种中介层与前面提到的无源硅中介层相似,但额外包含了有源电路,即除了 RDL(重布线层)和 TSV,还在前端集成了晶体管。

例如,CEA-LETI 于 2020 年 ISSCC 大会上展示了一种有源中介层方案。该系统包含 6 个基于 28 nm FD-SOI 技术制造的多 CPU Chiplet,它们堆叠在一个基于 65 nm CMOS 工艺制造的有源中介层上,并通过超细铜柱进行互连。

这种中介层内建片上网络(NoC),用作数据路由器,可在任意两个 CPU Chiplet 之间提供互连。此外,还可集成电源管理、I/O电路及传感器等功能。这些功能均采用成熟工艺节点实现,CPU Chiplet 则使用先进节点,从而在降低整体成本的同时实现系统级集成。

Chiplet-based先进3D系统架构中的有源中介层技术

3D 堆叠技术现在面临两大挑战:

· 热管理(Thermal Management):当芯片被垂直堆叠时,底层芯片的散热难度显著增加。因此需要在封装与芯片设计阶段引入三维热感知设计与冷却机制,以保持正常的工作温度。

· TSV 禁区(Keep-out Zone): 在有源中介层上使用 TSV 时,必须在 TSV 与有源晶体管之间预留隔离区,以避免 TSV 影响晶体管性能。这会导致有源中介层的 TSV 密度低于无源中介层,或者需要更大的面积(即 TSV penalty)来维持相同的 TSV 数量。

混合键合(Hybrid Bonding)

半导体分析机构SemiAnalysis 指出:“混合键合是自 EUV 光刻技术发明以来最具变革性的技术,是自90年代倒装芯片技术问世以来,芯片封装领域的又一次量子飞跃。” 此话不假。

目前最先进的微凸点技术可以做到5 微米的间距,要继续缩小已经非常困难。

而通过混合键合技术,研究人员已经实现了0.4 微米的间距,而这仅仅是开始。它可以实现每平方毫米超过一千万个互连点,其密度远超现有的任何微凸点技术。

混合键合是一种在无需焊球或铜柱的情况下垂直堆叠芯片甚至整个晶圆的工艺。其核心是铜-铜直接键合和介电层-介电层融合,因此得名混合键合(HB),又称混合键合互连(HBI, Hybrid Bonding Interconnect)。

(图片来源: 2025 ISSCC)

混合键合简化工艺流程如下:

1.两片晶圆经过表面处理,使其具有亲水性,并面对面对齐。此时互连所需的铜焊盘略低于周围氧化层;

2.晶圆接触后,氧化层在室温下形成弱键合;

3.随着温度缓慢升高:

a.氧化层之间形成更强的键合;

b.铜焊盘膨胀并相互接触。

4.在300–400°C下保持数小时,直至铜层与介电层完全融合;

5.最后将已键合的晶圆切割为3D堆叠芯片。

混合键合引领创新,迈向未来半导体集成之路

混合键合的可靠性取决于晶圆表面的极度平整和无颗粒。任何颗粒或不平整都会导致开路或鼓包。铜焊盘的凹陷深度也需精准控制,太浅可能导致无法有效接触,太深则膨胀,会造成界面脱层。

混合键合包括两种形式:

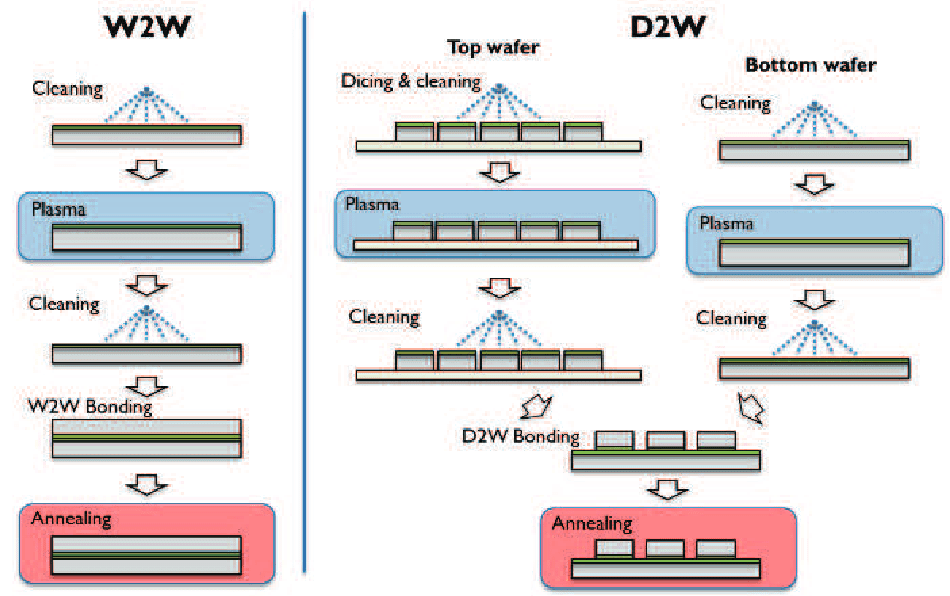

1.晶圆对晶圆(Wafer-to-Wafer, W2W):整片晶圆相互键合,这要求晶圆极度平整,无翘曲风险(可通过化学机械抛光 CMP 实现,这也是W2W HBI的关键步骤)。这种方法可实现小于0.5 微米的间距互连。其缺点是良率较低,尤其是采用先进工艺节点时,任一晶圆上的坏芯片都会导致配对失效。

2.晶粒对晶圆(Die-to-Wafer, D2W):先将晶圆切割成已知良品(Known Good Die),再翻转键合至整片晶圆上。其优点是良率更高,可避免浪费整片晶圆。缺点是互连间距约 2 微米,受限于对准精度及热膨胀差异。还有一个缺点就是芯片切割后的表面清洁,其难度要高于清洁整片晶圆。

die-to-wafer无机介质键合研究(ESTC)

混合键合技术目前仍处于早期发展阶段,现主要用于 3D NAND 闪存和部分 CMOS 图像传感器。业界认为,混合键合将是下一代 HBM发展的关键,有了它,16 层甚至更多 DRAM 堆叠都将成为可能,我们将拭目以待。

我要赚赏金

我要赚赏金