申请FPGA板子及进程更新

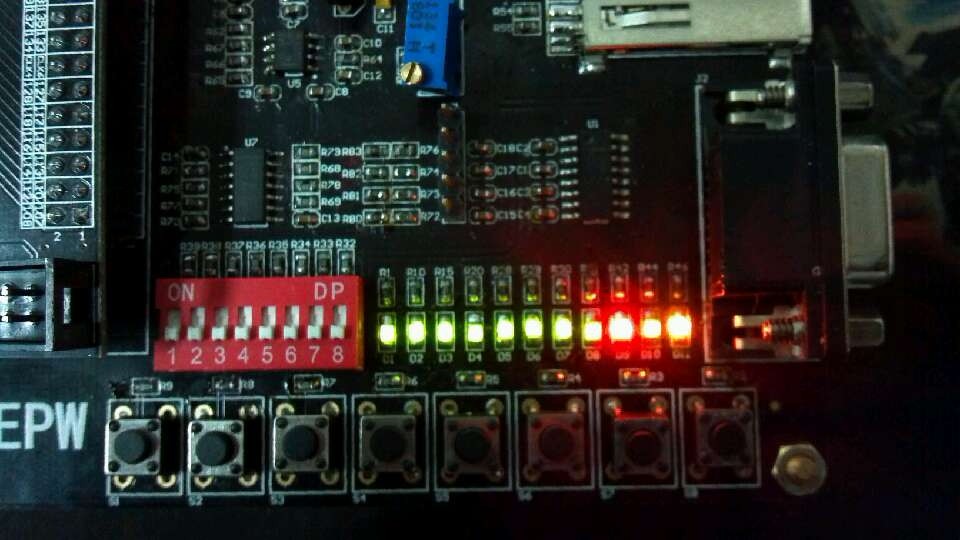

跑马灯程序

module led_water (sys_clk,sys_rstn,led) ; //输入输出信号定义

input sys_clk;//全局时钟,50Mhz

input sys_rstn;//复位信号,低电平有效

output [10:0] led ;//定义输出端口

reg [10:0] led ; //定义寄存器

reg [24:0] delay_cnt;//延时计数器

//逻辑部分

always @(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt<=25'd0;

else

begin

if(delay_cnt==25'd24999999)

delay_cnt<=25'd0;

else

delay_cnt<=delay_cnt+1'd1;

end

end

always @(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

led<=11'b11111111111;

else

begin

if(delay_cnt==25'd24999999)

begin

led<=led>>1;

if (led==11'b00000000000)

led<=~led;

end

else

led<=led;

end

end

endmodule

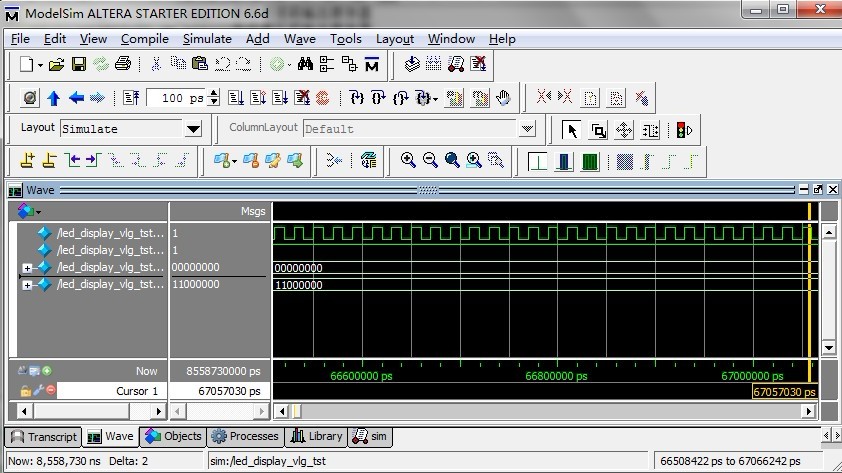

led_display实验一作业:拨码开关进行八进制数显示。led_key.zip

代码:

module led_key(sys_clk,key,sm_seg,sm_bit);

//输入输出信号

input sys_clk; //全局时钟 50Mhz

input[7:0] key; //按键输入

output[7:0] sm_seg;//数码管段码

output[7:0] sm_bit;//数码管位码

//寄存器定义

reg[7:0] sm_seg;//数码管段码输出寄存器

wire[7:0] sm_bit;//数码管位码输出寄存器

reg[3:0] key_dat;//显示数据寄存器

//*wire型数据常用来表示以assign为关键字组合逻辑信号,reg型为寄存器数据类型,常用来表示always模块内指定信号,常代表触发器。*/

//逻辑部分

always@(posedge sys_clk or negedge key )

begin

case (key)

8'hff:key_dat=4'h0;

8'hfd:key_dat=4'h1;

8'hfb:key_dat=4'h2;

8'hf7:key_dat=4'h3;

8'hef:key_dat=4'h4;

8'hdf:key_dat=4'h5;

8'hbf:key_dat=4'h6;

8'h7f:key_dat=4'h7;

endcase

end

always@(key_dat)

begin

case (key_dat)

4'h0:sm_seg=8'hf9;//"1"

4'h1:sm_seg=8'ha4;//"2"

4'h2:sm_seg=8'hb0;//"3"

4'h3:sm_seg=8'h99;//"4"

4'h4:sm_seg=8'h92;//"4"

4'h5:sm_seg=8'h82;//"6"

4'h6:sm_seg=8'hf8;//"7"

4'h7:sm_seg=8'h80;//"8"

endcase

end

/*begin...end类似于C语言里面的{}*/

assign sm_bit=8'b00000000 ;

endmodule

我要赚赏金

我要赚赏金