| 日期 | 内容 | 链接 |

| 2012年12月21日 | 惨痛的焊接经历以及点亮LED灯 | 2楼 |

| 2012年12月23日 | 2、FPGA各种LED点亮法 | 20楼 |

| 2013年1月3日 | 3、完成按键作业 | 21楼 |

| 2013年1月7号 | 4、完成LCD显示作业 | 24楼 |

anananjjj的FPGA_DIY进程贴的血泪史!

作为一名苦逼的学生!首先呢!是应为金钱方面的拮据,我本来打算放弃这次活动的!!恰好期间有了点收入,所以在活动进行了好长时间之后我才购买了商品二!

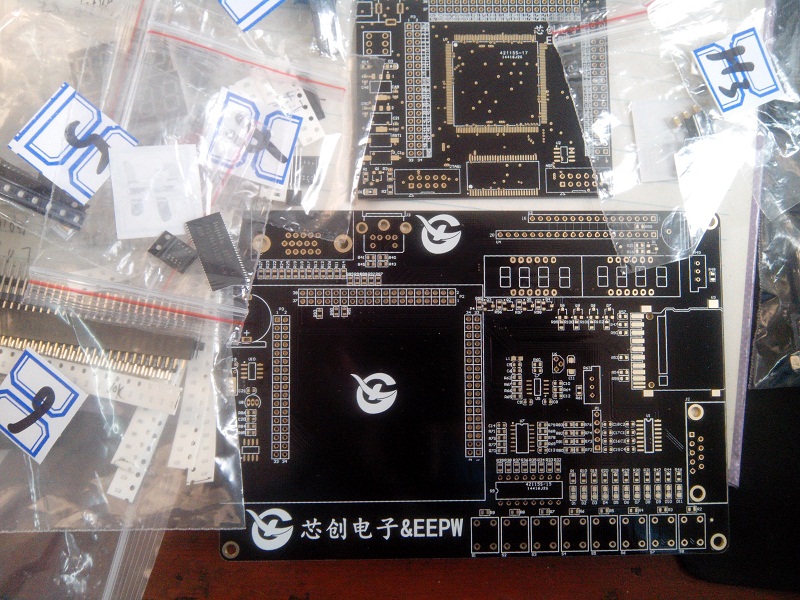

有着很多画板和焊板的经验,所以板子自然是自己焊了!!板子是买回来当天我就焊好了!

那大概是一个月之前的事情了!之后我就因为个人的原因,没再动它!所以并不知道他能否工作!

直到昨天,论坛询问为什么没更新进程的时候,我才觉得是时候跑跑它了!

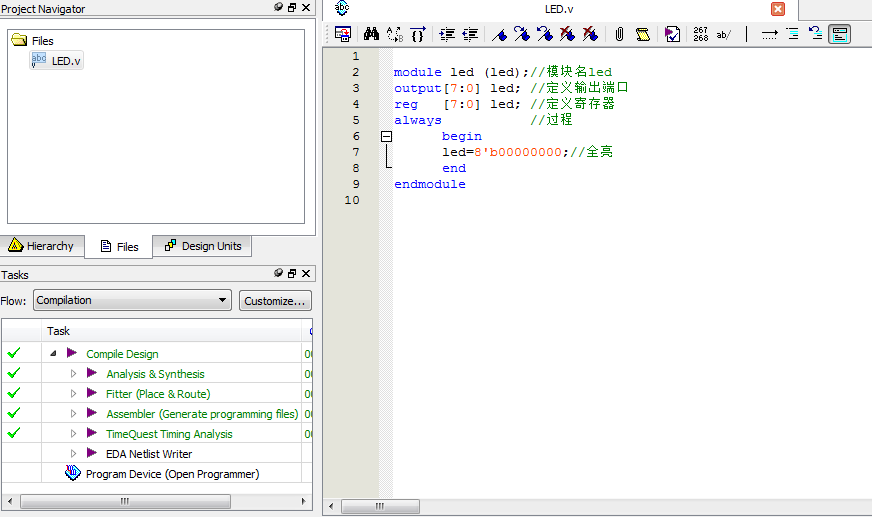

安装好Quartus II 12.0 (32-Bit)之后,我进行了作业1的内容,点亮LED!结果错误百出,问题百出!!!!!

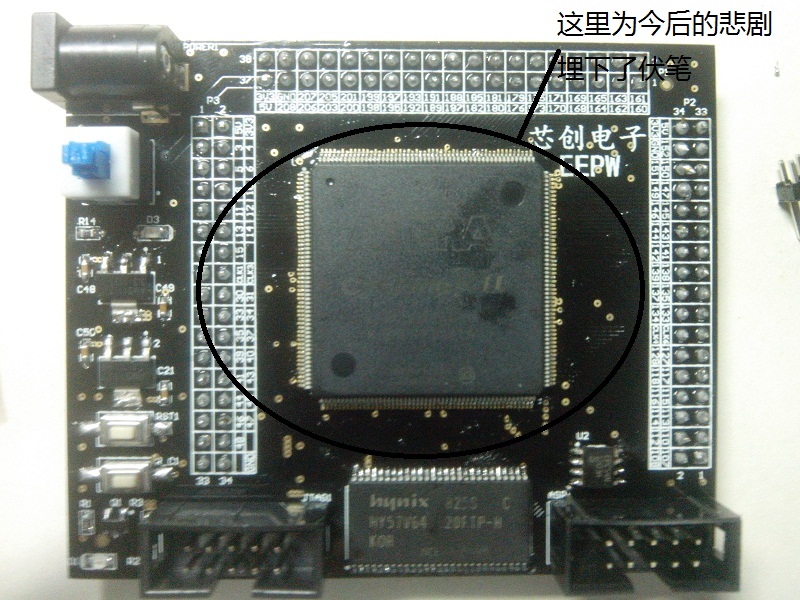

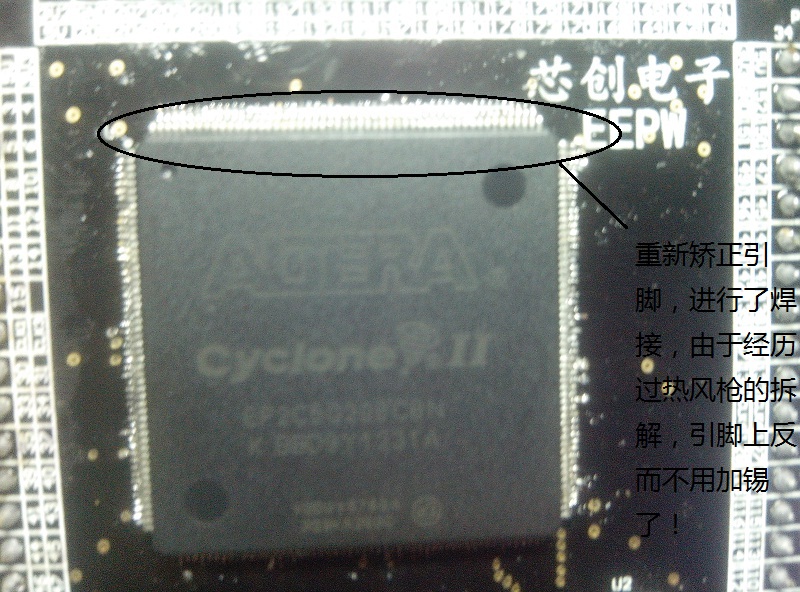

首先是编程环境不熟悉,居然连型号都选错了!!下载神马的也不会!这里就要感谢论坛里的朋友(啸风,Jobs......)在群里面对我的帮助了!他们耐心给我解释之后,我才发现是我的芯片引脚虚焊了!!

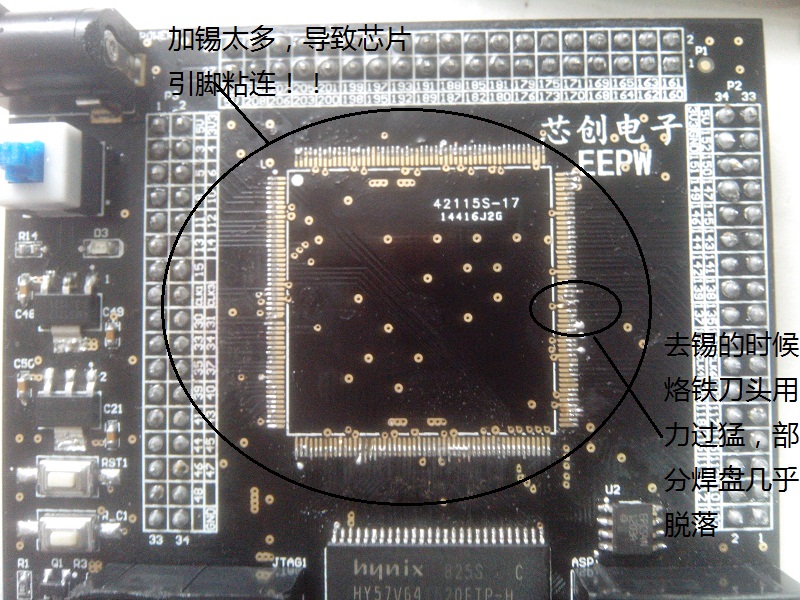

于是决定补焊!说实在的昨天我本来就有些莫名的心烦意乱!!感觉很差劲!这也导致我在补焊的时候放锡过多!!结果悲剧了!!引脚上连锡很厉害!焊盘也有些快要掉了!!

于是今天早起,我找Jackwang商量想再次购买元件,老王要我找51FPGA,他说没有元件了!!亲们啊!成品要160!!我。。我。。!!

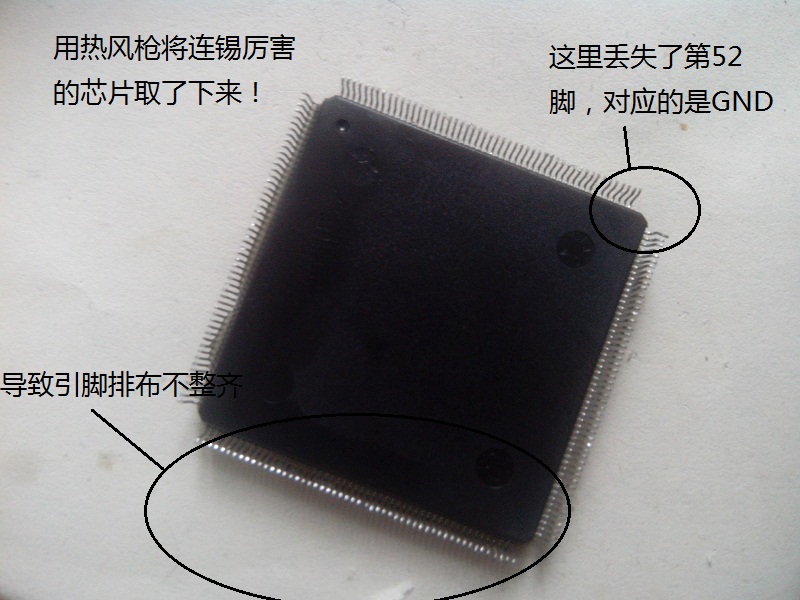

于是下午我索性死马当成活马医,拿热风枪将芯片给取下来了!!

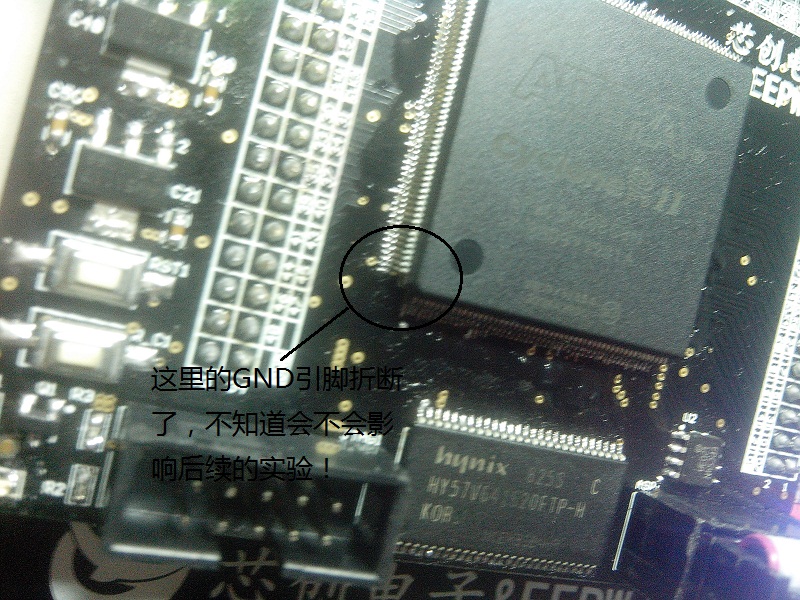

然后我小心翼翼地把松动的焊盘规整一下,将芯片引脚用镊子排整齐!!进行了二次焊接!!

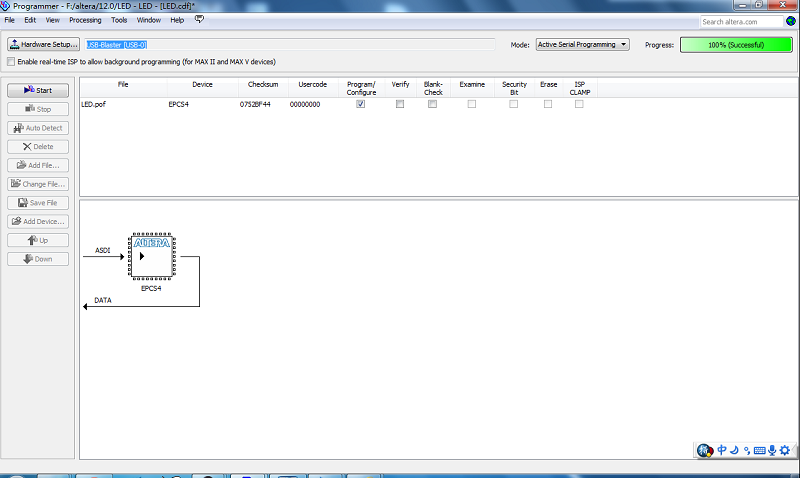

焊接好了之后,我怀着忐忑的心情下进了程序!

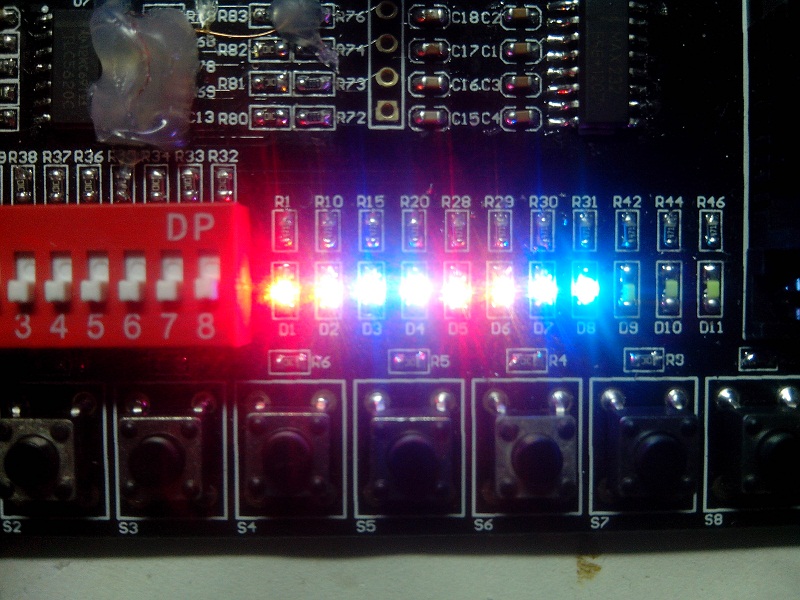

程序下进去了!八个LED亮了!!

其他的修正:

痛苦的经历!!幸好挽救了回来!!

2、FPGA各种LED点亮法:

按照活动提供的教程,我将LED的点亮方法跑了一遍,并完成了作业!

程序:

module Led_sample(sys_clk,sys_rstn,Led);//输入输出信号定义

input sys_clk;//全局时钟,50HZ

input sys_rstn; //复位信号,低电平有效

output [7:0] Led;//输出信号

//寄存器定义

reg [7:0] Led; //Led寄存器

reg [24:0] delay_cnt; //延时计数器

reg [24:0] cnt; //秒数

//逻辑部分

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

delay_cnt<=25'd0;

cnt<=25'd1;

end

else

begin

if(delay_cnt==25'd24999999)

begin

delay_cnt<=25'd0;

cnt<=cnt+1'b1;

begin

if(cnt==25'd63)

cnt<=25'd0;

end

end

else

delay_cnt<=delay_cnt+1'b1;

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

Led<=8'b11111110;//由左向右

else

begin

if(delay_cnt==25'd24999999)

begin

case(cnt/25'd16)

25'd0:

begin

Led<={Led[6:0],Led[7]};//由左向右

if(cnt==25'd15)

Led<=8'b01111111;//由左向右

end

25'd1:

begin

Led<={Led[0],Led[7:1]};//由右向左

if(cnt==25'd31)

Led<=8'b11111111;//由右向左

end

25'd2:

begin

Led<=~Led;

if(cnt==25'd47)

Led<=8'b11111111;

end

25'd3:

begin

Led<=Led<<1;

if(Led==8'b00000000)

Led<=8'b11111111;

if(cnt==25'd63)

Led<=8'b11111110;

end

endcase

end

else

Led<=Led;

end

end

endmodule

程序很简单,毕竟我是初学嘛!

上了演示视频吧:

按顺序,循环作向左跑马灯,向右跑马灯,集体闪烁和流水灯演示

3:完成按键作业:

忙着做项目,所以只能闲暇时做做DIY的作业,只是想有些自己的收获,所以慢慢更新,活动的日期就不关心了!关键是能学到东西!

利用去抖动按键切换数码管,显示0~9.

程序:

module key_data(sys_clk,sys_rstn,key_in,sm_seg,sm_bit);

//输入信号

input sys_clk;//50Hz

input sys_rstn;

input key_in;

//输出信号

output [7:0] sm_seg; //段码

output [7:0] sm_bit; //位码

//寄存器

reg [7:0] sm_seg;

reg [7:0] sm_bit;

reg [15:0] cnt ;

reg [19:0] delay_cnt;

wire key_scan;

wire key_low;

reg key_samp;

reg key_samp_r;

reg key_rst;

reg key_rst_r;

/*************************

按键脉冲边沿检测

***************************/

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_samp<=1'b1;

else

key_samp<=key_in;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_samp_r<=1'b1;

else

key_samp_r<=key_samp;

end

assign key_scan=key_samp_r&(~key_samp);

/*************************************

延迟20ms

************************************/

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt<=20'h0;

else if(key_scan)

delay_cnt<=20'h0;

else//按键按下

delay_cnt<=delay_cnt+1'b1;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_rst<=1'b1;

else if(delay_cnt==20'hfffff)

key_rst<=key_in;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_rst_r<=1'b1;

else

key_rst_r<=key_rst;

end

assign key_low=key_rst_r&(~key_rst);

/***********************************

***********************************/

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

cnt<=4'b0000;

else if(key_low)

begin

cnt<=cnt+1'b1;

if(cnt==4'b1001)

cnt<=4'b0000;

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

sm_bit<=8'b10101010;

case(cnt)

4'b0000:sm_seg<=8'hc0;

4'b0001:sm_seg<=8'hf9;

4'b0010:sm_seg<=8'ha4;

4'b0011:sm_seg<=8'hb0;

4'b0100:sm_seg<=8'h99;

4'b0101:sm_seg<=8'h92;

4'b0110:sm_seg<=8'h82;

4'b0111:sm_seg<=8'hf8;

4'b1000:sm_seg<=8'h80;

4'b1001:sm_seg<=8'h90;

default:sm_seg<=8'hc0;

endcase

end

endmodule

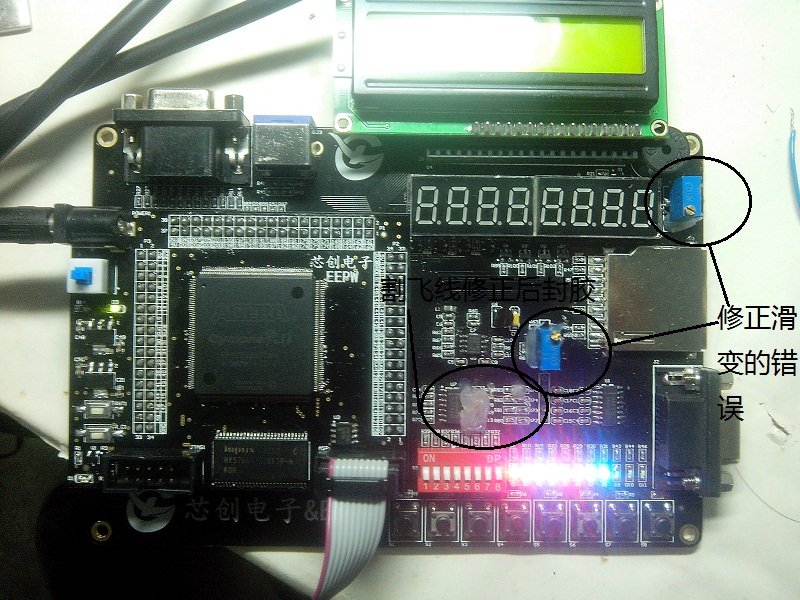

图片:

视频:

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |