LM75使用篇

看见群里一直有人问这个芯片肿么焊,我是这样焊的,板子正对着自己,芯片倒着放,芯片上的字是反着的。这样焊,芯片工作正常,读出的数据也很完美,你值得一试。

这款芯片怎么说呢,知名度没有DS18b20高,谁让别人是单总线这么个新鲜玩意呢。理论上说一条IIC总线上可挂接8个LM75,这样的规定地址和24C0X系列一样,言归正传,看看FPGA是怎么样模拟IIC总线的呢。

首先咱们打开LM75数据手册LM75.pdf,看到SCL的周期最小到2.5us,也就是说,IIC的操作频率不能高于400KHz,这速度可比串口快多了哈,我这里用的是100KHz,同理,写了一个分频器。然后我将一个周期分成4个部分,分别是“上升沿”、“高电平中心”、“下降沿”、“低电平中心”(这里参考了网上默默奉献的大牛们的思路,在此表示非常的感谢,是你们带领我们这些菜鸟进步),“上升沿”对应的计数值到来时,SCL=1,“下降沿”对应的计数值到来时,SCL=0,这样SCL就一直在工作了,不仅如此,众所周知,sda在SCL上升沿时锁存信号,这时,我们可以每次在SCL在“低电平中心”时送sda数据,这样的话,SCL上升沿的时候,sda数据必定是稳定的,至于为什么要在低电平中心呢?我想可能中心点的SCL有比较稳定的电平(相比在上升沿会有上升时间或波动啥的),这里希望大牛们能给我们指点一些迷津。

底层工作做好啦,下面就是搭建上层建筑,包括起始时序、写时序、(从机、主机)应答时序、停止时序、读时序,这些可以从24C02的数据手册里看到24c02串行储存器中文官方资料手册.pdf

知道了以上这些时序呢,最后就是先发啥指令,再发啥指令。。。。。。我是这样的:

1. 写指令:0x90,这是写器件地址,意思就是我选你了。

2. 写温度寄存器地址:0x00,这是存温度值的寄存器,即写入要读的寄存器的地址。

3. 结束一个写周期

4. 重新开始,写指令:0x91,这是读器件地址。

5. 读16位温度值(其实就前8位是有效的 ),记住:每读8位温度值,主机要给LM75一个应答,最后一个字节读完,主机来一个非应答(用完了就不管别人死活)然后停止。

),记住:每读8位温度值,主机要给LM75一个应答,最后一个字节读完,主机来一个非应答(用完了就不管别人死活)然后停止。

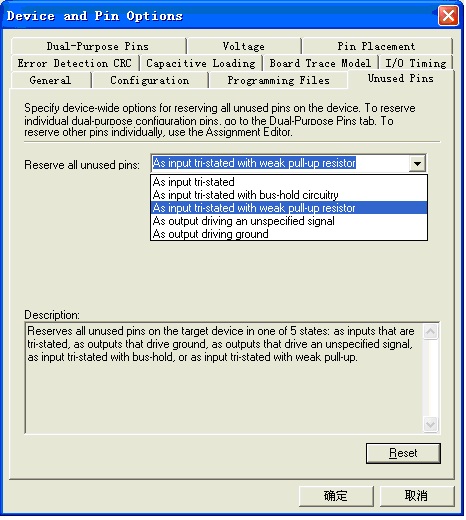

注意:每次应答的时候我都是象征性的跳过一个SCL周期,以前死磕着判断sda是否为低,最后程序就一直循环着死磕,可能从机都应答完了,你没采到值罢了;sda未使用或者作为input使用时最好将其设置为高阻态。

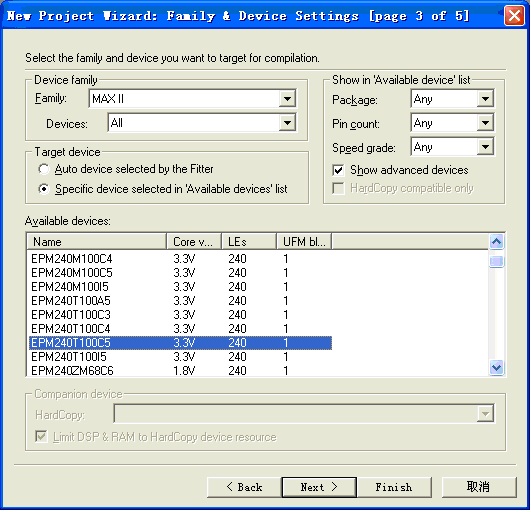

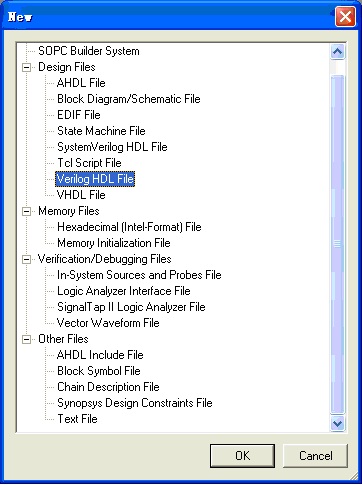

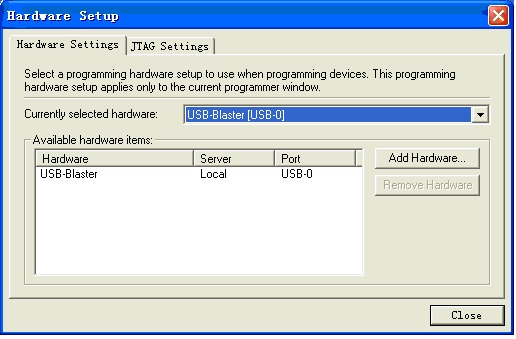

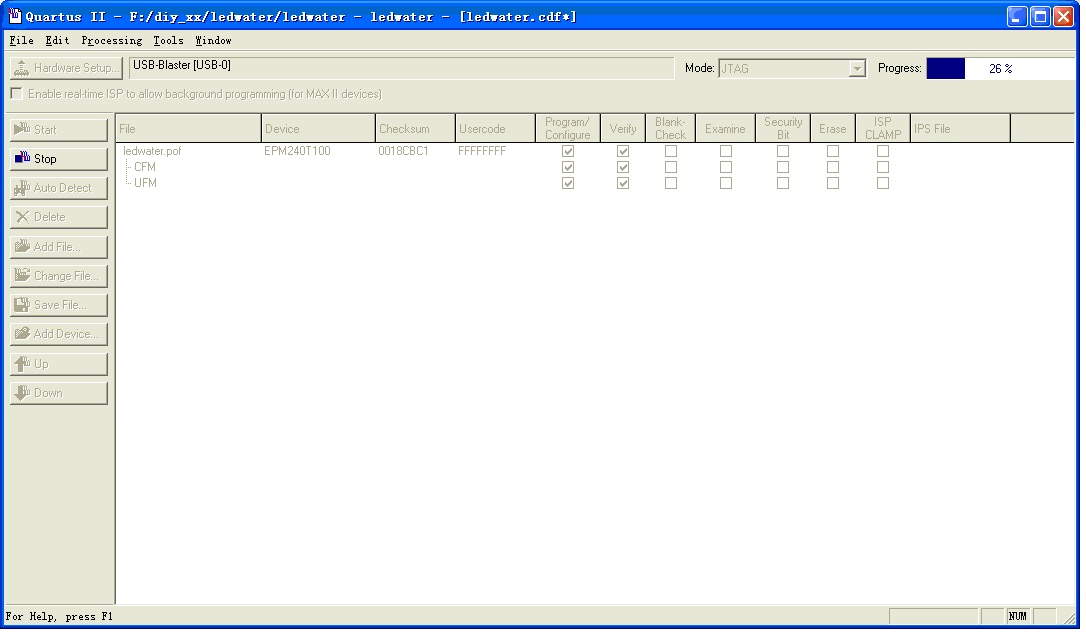

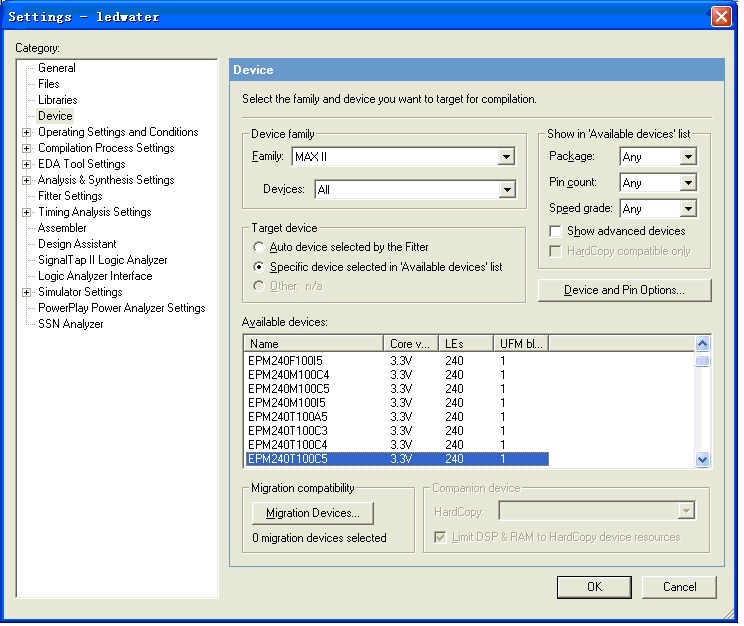

特别注意:由于读出的温度值要分离出十位和个位,我们自然而然的想到用“/”和“%”,之前一直使用的ISE,FPGA不支持除法,ISE也不支持,得自己添加核。早就听闻Quartus比较人性化,编译的时候自动添加除法和取模的核,我自然而然的跃跃欲试,综合一下,果然自动添加核,令我兴奋不已,可是却显示使用了300多个逻辑门,而这款CPLD却只有240(单位不知道是什么呀),一看两个核用了100多逻辑门,心里顿时拔凉拔凉的,无奈,还是用了老办法:case语句罗列出所有可能性,大神们有什么更可行的方案不?咱们可以交流交流。

还有,IIC时序控制我全部使用的是状态机来控制的,使得程序十分累赘,但自己读起来比较好理解,想请教一下大神们有什么好办法不?

视频观看:

我要赚赏金

我要赚赏金