V 型开发过程详解

一、V 型开发模型的核心架构与理论基础

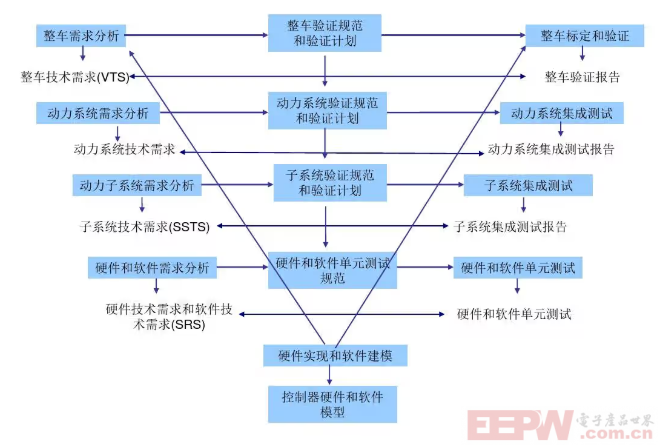

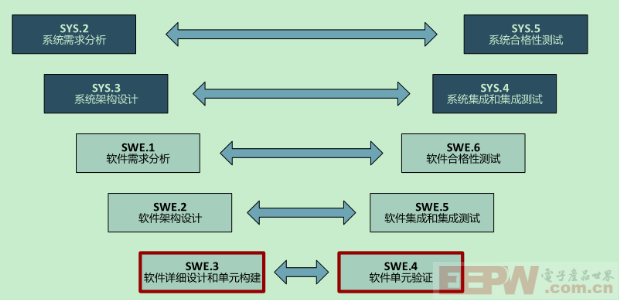

V 型开发模型作为系统工程领域的经典方法论,其本质是将抽象需求通过结构化流程转化为可验证的物理实现,因开发与验证环节呈对称 “V” 型分布而得名。在汽车电子领域,该模型以 ISO 26262 功能安全标准、ASPICE 软件开发流程等行业规范为支撑,通过 “左半设计 - 右半验证” 的闭环逻辑,确保电子模块从需求定义到量产交付的全周期可控。

层级对应关系:左侧设计阶段(需求分析→顶层设计→细节设计)与右侧验证阶段(系统实施→单元测试→整合测试→设计验证)形成严格的映射关系,每个设计环节均有对应的验证节点;

迭代优化机制:引入循环设计理念,允许通过测试反馈对前期设计进行多轮修正,避免 “瀑布式开发” 的单向性缺陷;

跨学科协同框架:打破系统、硬件、软件、测试等团队的职能壁垒,通过标准化接口定义实现并行开发。

二、V 型开发模型的左侧流程:从需求到设计的解构

定义开发边界与技术基准

需求分析是 V 型模型的逻辑起点,需由系统工程师牵头,联合硬件、软件、测试等职能团队,对客户需求(整车厂技术规范)或内部需求(平台化设计要求)进行系统性拆解。该环节的核心工作包括:

需求分类与标准化

将原始需求转化为可量化的技术文件,常见分类包括:

硬件设计规范(HDS):明确供电范围( 12V±30%)、EMC 等级(CISPR 25 Class 5)、环境适应性(-40℃~125℃工作温度)等指标;

软件设计规范(SDS):定义控制逻辑(电机 PWM 调速算法)、通信协议(CAN/LIN 总线数据帧格式)、诊断功能(UDS 协议支持)等要求;

测试验证规范(TVS):制定功能测试用例(电源模块启动时间≤50ms)、可靠性测试标准(振动测试加速度≥50G);

机械设计规范(MDS):规定安装尺寸(PCB 板长 × 宽≤100mm×80mm)、防护等级(IP6K9K 防水防尘)等机械参数。

需求冲突管理

当多源需求存在矛盾时(高算力芯片与低功耗要求冲突),需通过 DFMEA(设计失效模式分析)评估风险等级,结合成本与性能优先级制定折中方案。

(二)顶层设计:构建系统级技术架构

基于需求分析结果,各职能团队开展全局性方案规划,形成跨领域的技术协同框架:

硬件顶层设计

芯片选型策略:根据功能需求初步确定核心器件,MCU 选型需权衡算力(DMIPS/MHz)、存储容量(Flash/RAM)、外设接口(ADC 通道数、PWM 频率)及成本(英飞凌 AURIX 系列 vs 恩智浦 S32K 系列);

热分析建模:通过 ANSYS 等工具预估关键器件(功率 MOSFET)的功耗密度,规划散热路径(自然冷却 / 强制风冷),确保结温≤150℃安全阈值;

系统架构设计:绘制电子模块框图,定义信号流(传感器→ADC→MCU→驱动芯片→执行器)、电源树(主电源→LDO→DC-DC)及接口规范(连接器引脚定义、ESD 防护等级)。

软件顶层设计

采用分层架构(应用层→中间件→驱动层),汽车电子典型架构符合 AUTOSAR 标准,通过 MCAL(微控制器抽象层)隔离硬件差异;

定义任务调度机制(基于 OSEK 操作系统的抢占式多任务调度),分配各功能模块的 CPU 占用率(通信任务≤20%,控制任务≤50%)。

(三)细节设计:从架构到工程的落地

顶层设计完成后,进入工程实现的细节验证阶段,以硬件设计为例,该环节需完成:

原理图精细化设计

基于顶层架构绘制详细电路图,包含:

电源电路:反激式开关电源的变压器匝比计算、输出滤波电容 ESR 选型;

信号链电路:运算放大器的增益带宽积(GBP)匹配、RC 滤波网络的截止频率计算;

保护电路:TVS 管的钳位电压选择、保险丝的熔断电流标定。

设计可靠性评估

失效率分析:运用 FMEA 工具对元器件进行风险排序,电解电容(失效率 λ≥10 FIT)需优先选用车规级产品(NCC UTS 系列);

最坏情况分析(WCA):模拟极端工况下的电路参数漂移,电阻温度系数(±50ppm/℃)对分压精度的影响;

热应力分析:计算元器件实际工作温度与额定温度的比值(MOSFET 温升 ΔT=70℃,额定结温 Tj=175℃,则热应力 = 70/175=40%≤80% 安全阈值)。

三、V 型开发模型的右侧流程:从实现到验证的闭环

(一)系统实施:物理实体的工程实现

该阶段将设计文件转化为可测试的物理载体,涉及多领域并行作业:

硬件实施

PCB 设计:采用 Altium Designer 等工具完成 Layout,遵循汽车电子 PCB 设计规范(电源层与地层间距≤5mil、信号线特性阻抗控制 50±10%);

元器件焊接:通过回流焊工艺(峰值温度 230±5℃)完成 SMT 贴片,车规级产品需满足 IPC-A-610 Class 3 标准。

软件实施

代码实现:基于 MATLAB/Simulink 模型自动生成 C 代码(dSPACE TargetLink 工具链),或手动编写底层驱动(GPIO 初始化、SPI 通信协议);

代码静态分析:使用 Polyspace 等工具检测代码缺陷(数组越界、除零错误),确保 MISRA C 合规率≥95%。

(二)单元测试:模块级功能验证

针对单个部件或功能模块开展针对性测试,典型场景包括:

硬件单元测试

电源模块:测试输出电压纹波(≤50mVpp)、负载调整率(≤0.1%/A)、启动浪涌电流(≤额定电流 3 倍);

信号调理电路:验证放大电路的增益精度(±1%)、滤波电路的截止频率偏差(±5%)。

软件单元测试

函数级测试:CAN 通信接收函数需验证不同 ID 报文的解析正确性、错误帧处理逻辑;

覆盖率测试:通过 LDRA 工具统计代码分支覆盖率(车规级要求≥90%)、条件覆盖率(≥75%)。

(三)整合测试:系统级功能联调

在单元测试通过后,开展跨模块的整合验证,核心包括:

软硬件联调

验证 MCU 控制逻辑与硬件驱动的协同性,电机控制模块需测试 PWM 占空比与电机转速的线性度(误差≤2%);

模拟传感器输入(0~5V 电压信号),验证 ADC 采样精度与软件滤波算法的有效性。

通信协议测试

在 CAN 总线环境中,测试多节点通信的实时性(报文传输延迟≤1ms)、容错性(总线故障时的恢复机制),符合 ISO 11898 标准。

(四)设计验证:全场景可靠性评估

按整车厂标准对电子模块进行全面考核,涵盖:

环境适应性测试

温度循环:-40℃~125℃,1000 次循环,测试元器件焊点抗热疲劳能力;

湿度测试:85℃/85% RH 环境下持续 1000 小时,验证 PCB 三防漆(聚氨酯涂层)的防潮性能。

EMC 测试

辐射发射:在 30MHz~1GHz 频段内,确保辐射骚扰场强≤40dBμV/m(Class 5 标准);

抗干扰测试:施加 ±25V 静电放电(ESD)、100V/m 射频电磁场,模块功能不得失效。

功能安全测试

针对 ISO 26262 ASIL-D 等级需求,验证安全机制有效性,看门狗电路的复位精度(超时响应≤10ms)、电源监控电路的欠压保护阈值(9V±0.5V)。

四、V 型开发模型的行业实践与优化策略

(一)模型调整与企业适配

不同车企与供应商会根据项目特点对 V 型模型进行定制化改造:

敏捷开发融合:在细节设计与单元测试环节引入迭代机制,采用 Scrum 框架将软件模块划分为多个 Sprint 周期,每个周期包含 “设计 - 编码 - 测试” 小闭环;

虚拟验证前置:通过 MATLAB/Simulink 搭建系统仿真模型,在顶层设计阶段完成控制算法的硬件在环(HIL)测试,减少物理样件迭代次数。

以上内容来自网络,供大家了解学习。

我要赚赏金

我要赚赏金