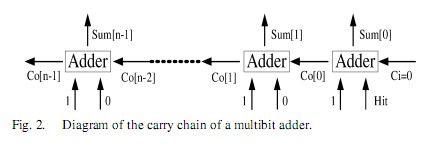

如上图所示,怎么样才能把所有的加法器链接到一起呢?因为adder有很多,直接在原理图画很吃力,有没有什么好方法啊?

虽然,循环结构经常用在Testbench中,但在可综合的语句中也可以用,你的语句展开综合,也就是面积的复制。

能说一下你的Adder的1、0、Hit表示什么意思吗?应该是加法器的两个加数吧,值应该来自wire或reg?

今天中午试了下,好像还真不行。

如果是使用例化语句的话,好像不能for,因为实在always外面的。

如果直接在alwasys里面写,如下:

module TestAdder( Hit, CoOut

);

input Hit;

output CoOut;

parameter N=10;

(*keep="1"*) reg [N-1 : 0] Sum;

(*keep="1"*) reg [N-1 : 0] Co;

//OneBitAdder Adder1 ( .A( Hit ), .B(1), .Ci(0), .Co( Co[0] ), .Sum( Sum[0] ) );

integer i;

assign CoOut = Co[N-1];

always @ ( Hit )

begin

{ Co[0], Sum[0] } = 1 + Hit + 0;

for( i=1; i<N; i++ )

{ Co[i], Sum[i] } = 1 + 0 + Co[i-1];

end

endmodule

综合时又被优化了,Synplify Pro的综合结果如下:

只综合得到一个缓冲器,还是不行。

271303204是需要什么样的延时效果呢?要用这种加法器做延时。我觉得即使是用例化的,也还是会有被综合器优化的可能。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |