格雷码计数器的问题

在数字系统中只能识别0和1,各种数据要转换为二进制代码才能进行处理,格雷码是一种无权码,采用绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。格雷码属于可靠性编码,是一种错误最小化的编码方式,因为,自然二进制码可以直接由数/模转换器转换成模拟信号,但某些情况,例如从十进制的3转换成4时二进制码的每一位都要变,使数字电路产生很大的尖峰电流脉冲。而格雷码则没有这一缺点,它是一种数字排序系统,其中的所有相邻整数在它们的数字表示中只有一个数字不同。它在任意两个相邻的数之间转换时,只有一个数位发生变化。它大大地减少了由一个状态到下一个状态时逻辑的混淆。另外由于最大数与最小数之间也仅一个数不同,故通常又叫格雷反射码或循环码。下表为几种自然二进制码与格雷码的对照表:

┌─────┬─────────┬────┬─────┬─────────┬─────┐

│十进制数│自然二进制数│格雷码│十进制数│自然二进制数│ 格雷码 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 0 │ 0000 │ 0000 │ 8 │ 1000 │ 1100 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 1 │ 0001 │ 0001 │ 9 │ 1001 │ 1101 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 2 │ 0010 │ 0011 │ 10 │ 1010 │ 1111 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 3 │ 0011 │ 0010 │ 11 │ 1011 │ 1110 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 4 │ 0100 │ 0110 │ 12 │ 1100 │ 1010 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 5 │ 0101 │ 0111 │ 13 │ 1101 │ 1011 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 6 │ 0110 │ 0101 │ 14 │ 1110 │ 1001 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

│ 7 │ 0111 │ 0100 │ 15 │ 1111 │ 1000 │

├─────┼─────────┼────┼─────┼─────────┼─────┤

一般的,普通二进制码与格雷码可以按以下方法互相转换:

二进制码->格雷码(编码):从最右边一位起,依次将每一位与左边一位异或(XOR),作为对应格雷码该位的值,最左边一位不变(相当于左边是0);

格雷码-〉二进制码(解码):从左边第二位起,将每位与左边一位解码后的值异或,作为该位解码后的值(最左边一位依然不变).

数学(计算机)描述:

原码:p[0~n];格雷码:c[0~n](n∈N);编码:c=G(p);解码:p=F(c);书写时从左向右标号依次减小.

编码:c=p XOR p[i+1](i∈N,0≤i≤n-1),c[n]=p[n];

解码:p[n]=c[n],p=c XOR p[i+1](i∈N,0≤i≤n-1).

Gray Code是由贝尔实验室的Frank Gray在20世纪40年代提出的(是1880年由法国工程师Jean-Maurice-Emlle

Baudot发明的),用来在使用PCM(Pusle Code Modulation)方法传送讯号时避免出错,并于1953年3月17日取得美国专利。由定义可知,Gray Code的编码方式不是唯一的,这里讨论的是最常用的一种。

格雷码

(英文:Gray Code, Grey Code,又称作葛莱码,二进制循环码)是1880年由法国工程师Jean-Maurice-Emlle Baudot发明的一种编码,是一种绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。格雷码属于可靠性编码,是一种错误最小化的编码方式,因为,虽然自然二进制码可以直接由数/模转换器转换成模拟信号,但在某些情况,例如从十进制的3转换为4时二进制码的每一位都要变,能使数字电路产生很大的尖峰电流脉冲。而格雷码则没有这一缺点,它在相邻位间转换时,只有一位产生变化。它大大地减少了由一个状态到下一个状态时逻辑的混淆。由于这种编码相邻的两个码组之间只有一位不同,因而在用于风向的转角位移量-数字量的转换中,当风向的转角位移量发生微小变化(而可能引起数字量发生变化时,格雷码仅改变一位,这样与其它编码同时改变两位或多位的情况相比更为可靠,即可减少出错的可能性。

但格雷码不是权重码,每一位码没有确定的大小,不能直接进行比较大小和算术运算,也不能直接转换成液位信号,要经过一次码变换,变成自然二进制码,再由上位机读取。解码的方法是用‘0’和采集来的4位格雷码的最高位(第4位)异或,结果保留到4位,再将异或的值和下一位(第3位)相异或,结果保留到3位,再将相异或的值和下一位(第2位)异或,结果保留到2位,依次异或,直到最低位,依次异或转换后的值(二进制数)就是格雷码转换后自然码的值.

异或:异或则是按位“异或”,相同为“0”,相异为“1”。例:

10011000 异或 01100001 结果: 11111001

举例:

如果采集器器采到了格雷码:1010

就要将它变为自然二进制:

0 与第四位 1 进行异或结果为 1

上面结果1与第三位0异或结果为 1

上面结果1与第二位1异或结果为 0

上面结果0与第一位0异或结果为 0

因此最终结果为:1100 这就是二进制码即十进制 12

当然人看时只需对照表1一下子就知道是12

思路为:

两个状态,一个表示低4bit,一个表示高4bit。用状态切换来实现计数。第一个状态机的时钟为计数时钟,当低一个状态机计满后产生进位,这个进位信号作为第二个状态机的时钟。

你可以照这个方法试试看,要是写不出来,我给你写一个。

8位格雷码计数器的Verilog描述如下:

module GrayCnt( Clk, nRst, CntOut );

input Clk, nRst;

output [7:0] CntOut;

reg [7:0] CntOut;

reg [7:0] NextCnt;

always @(posedge Clk)

begin

if (~nRst)

CntOut <= 8'b0000_0000;

else

CntOut <= NextCnt;

end

reg [7:0] tmpCnt;

integer k;

always @( CntOut )

begin

tmpCnt[7] = CntOut[7];

for( k=6; k>=0; k=k-1 )

tmpCnt[k] = CntOut[k] ^ tmpCnt[k+1];

if( tmpCnt[0]==1'b0 )

begin

NextCnt[0] = ~CntOut[0];

NextCnt[7:1] = CntOut[7:1];

end

else if( tmpCnt[1]==1'b0 )

begin

NextCnt[0] = CntOut[0];

NextCnt[1] = ~CntOut[1];

NextCnt[7:2] = CntOut[7:2];

end

else if( tmpCnt[2]==1'b0 )

begin

NextCnt[1:0] = CntOut[1:0];

NextCnt[2] = ~CntOut[2];

NextCnt[7:3] = CntOut[7:3];

end

else if( tmpCnt[3]==1'b0 )

begin

NextCnt[2:0] = CntOut[2:0];

NextCnt[3] = ~CntOut[3];

NextCnt[7:4] = CntOut[7:4];

end

else if( tmpCnt[4]==1'b0 )

begin

NextCnt[3:0] = CntOut[3:0];

NextCnt[4] = ~CntOut[4];

NextCnt[7:5] = CntOut[7:5];

end

else if( tmpCnt[5]==1'b0 )

begin

NextCnt[4:0] = CntOut[4:0];

NextCnt[5] = ~CntOut[5];

NextCnt[7:6] = CntOut[7:6];

end

else if( tmpCnt[6]==1'b0 )

begin

NextCnt[5:0] = CntOut[5:0];

NextCnt[6] = ~CntOut[6];

NextCnt[7] = CntOut[7];

end

else

begin

NextCnt[6:0] = CntOut[6:0];

NextCnt[7] = ~CntOut[7];

end

end

endmodule

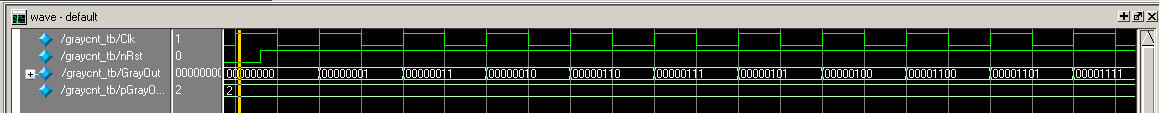

仿真截图(Modelsim):

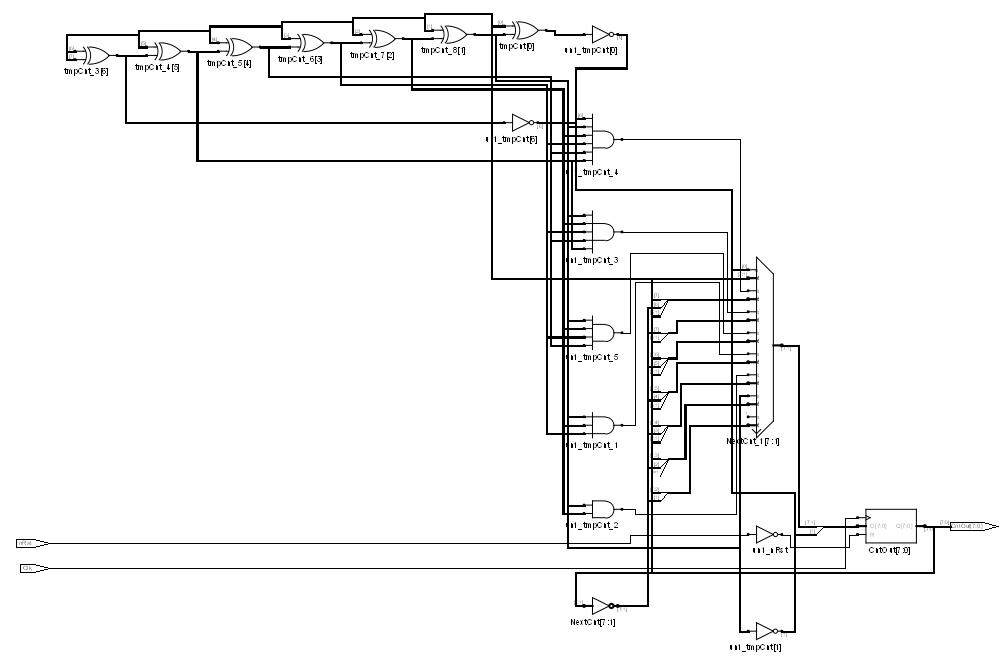

综合RTL结果(Synplify):

可以看到,只适用了异或门、非门、选择器和寄存器。

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |