共6条

1/1 1 跳转至页

FPGA constraint设置讨论

FPGA设置开发中有很多难点,其中之一就是constraint的设置。

望各位朋友展开讨论,并给予指导。

感谢!

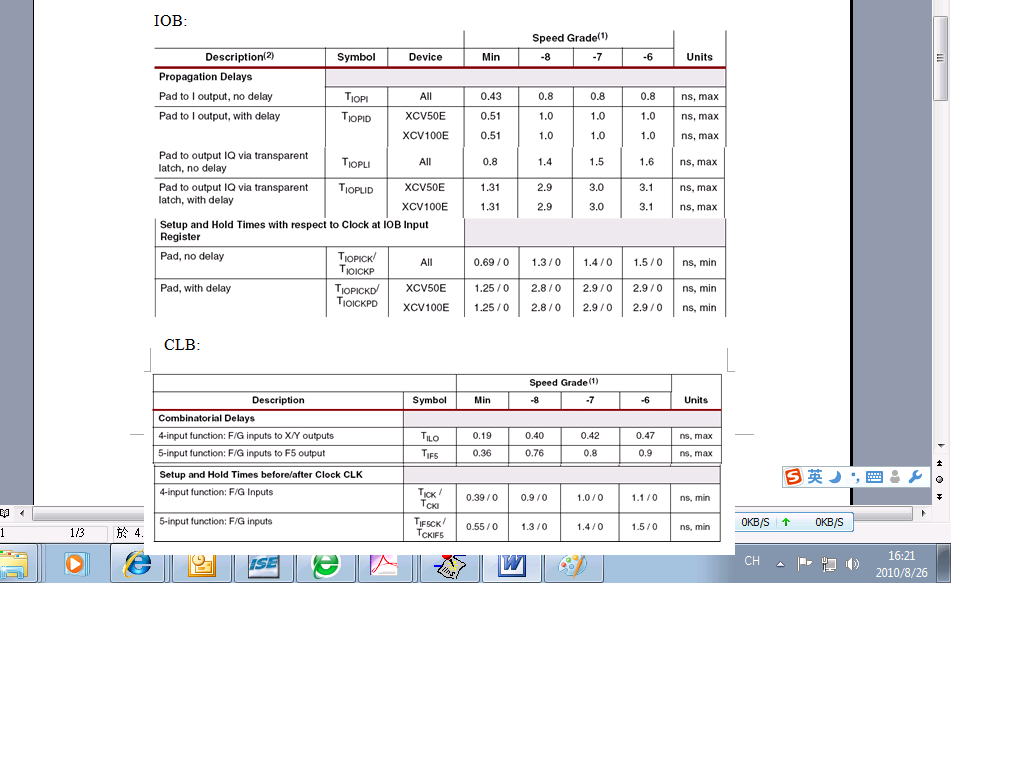

当我们在设置FPGA constraint的时候,我们应该是首先要了解该器件的参数。如频率参数,setup time和hold time参数等。

但问题是,有如此多的参数,我们该使用datasheet中的哪些参数来估算PERIOD/OFFSET的 time scale?

如何设置FF—FF之间的setup/hold time?是否是使用FROM_TO的TS_C2S进行设置?

还有问题的是,比如为了保证得到正确的传输,DATA_IN 的offset该如何设置?

如下例子,我看到xilinx 介绍说DATA_IN至少要比CLK早20ns到达,问题来了:我们知道对于已经设计好的device,DATA到越早越好,但问题是对于使用DATA_IN_BEFORE而言DATA到的时间已经给定了,不能改变。 也就是说我们只是在开发接收端的功能,这时Tsu,Tclk已知,其实Tdata才是使用到constraint的设置后强行要求满足的参数,(Tin_before=Tdata+Tsu-Tclk;=> Tdata=Tin_before+Tclk-Tsu),在Tin_before刚好等于Tdata+Tsu-Tclk时,是正确latch到data的极限,为了保证正确latch到数据那么这个时候 应该把Tin_before设置小一点才能得到更小的Tdata,也就是DATA才更早到达FF.可为什么xilinx的constraint说明却要写成Tin_before>=Tdata+Tsu-Tclk ,如果没有仔细分析直接去一个比较大的值是否会造成Tdata比较大,造成latch的错误?

以上是本人的观点,请各位给予指导,谢谢

关键词: constraint 设置 讨论

I read the xilinx’s constraint guide, it said that Tin_before>=Tdata+Tsu-Tclk, we knew the Tin_before is good as large as possible for a fixed device that we can do nothing.

the question is that the designing FPGA device receives the data from other device when we use the DATA_IN_BEFORE to set the constraints,so the Tin_before is a known characteristic,we can get it using the oscilloscope. Using Tin_before to set the Tdata is our purpose,so optionally choosing a large Tin_before that is larger than Tdata+Tsu-Tclk maybe get larger Tdata,result in failure for latching data.my guess is that setting small Tin_before characteristic can get small Tdata,so can latch correct data.

So is the constraint book wrong, or my thought wrong ?

When we want to set the constraint, how do we estimate the period,DATA_IN_BEFORE,DATA_OUT_AFTER?

Which characteristics do we need to get from the FPGA datasheet ?

And,when we set the global constraints,because have IOB’s setup and CLB’s setuptime,which characteristic do we choose ?

How to set the FF ot FF timing,like setup/hold time ? use FROM_TO’s TS_C2S ?

And,because both IOB and CLB have FFs, their FFs setup/hold time characteristics are different, so how to estimate the FFs’s timing ?

Expect the reply,thanks everybody

5楼

可以上传附件的。

就在发帖时编辑框的最后一行倒数第二个那个蓝白相间的图标,点击就可以打开“分享下载”,按提示操作就可以了。

共6条

1/1 1 跳转至页

。

。 我要赚赏金

我要赚赏金