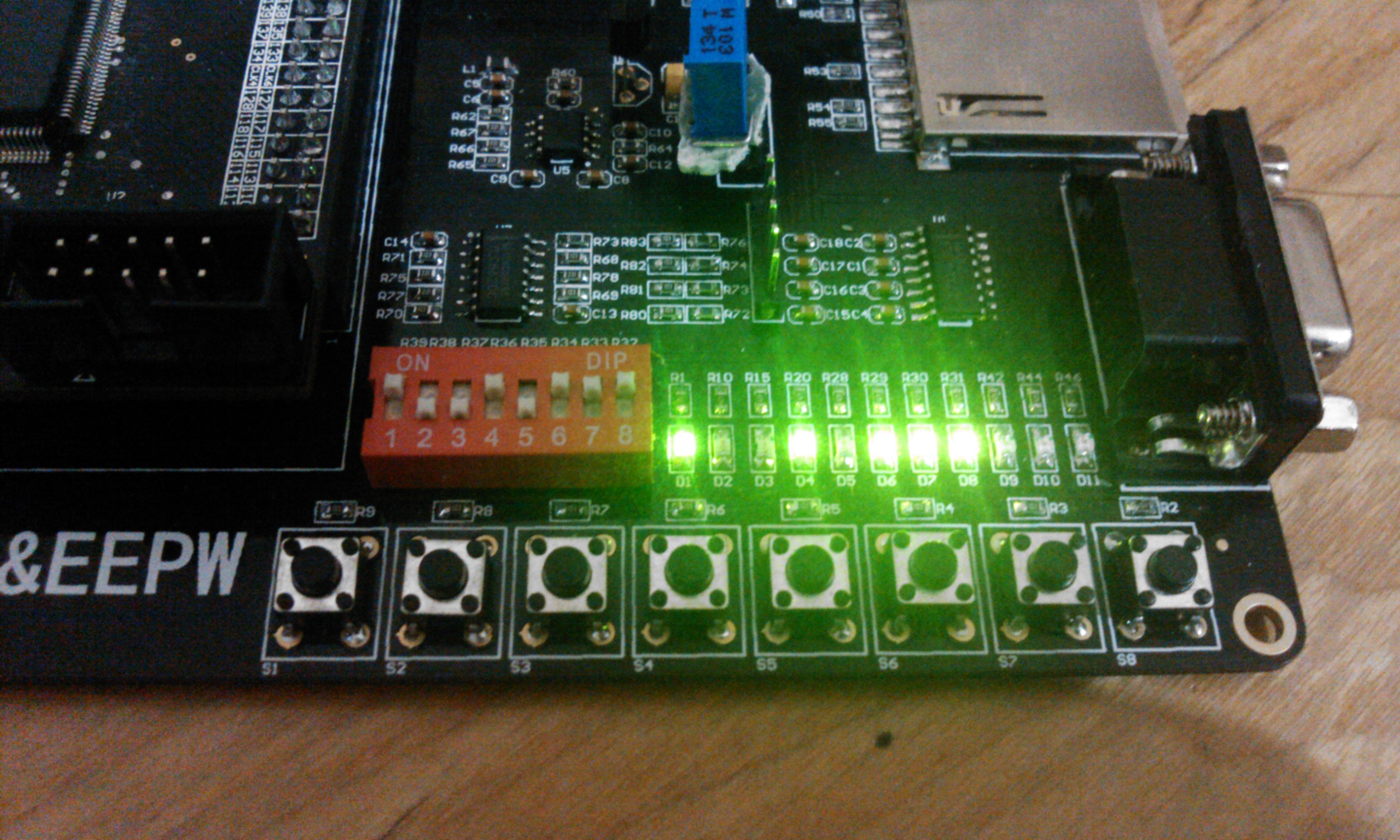

代码很简单

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LED_SW IS

PORT(

SW :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

LED :OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

end entity;

architecture one OF LED_SW IS

BEGIN

LED<=SW;

END one;

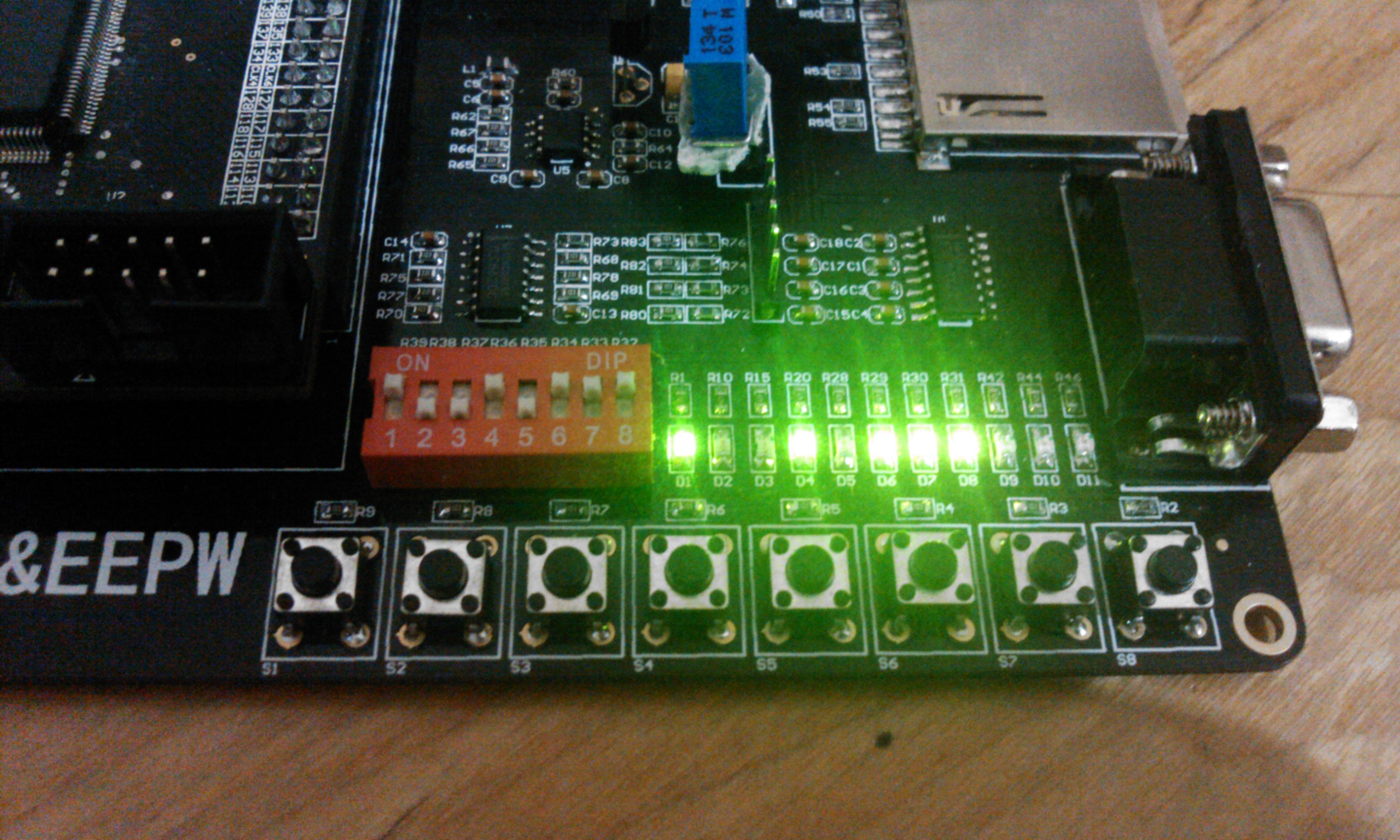

代码很简单

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LED_SW IS

PORT(

SW :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

LED :OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

end entity;

architecture one OF LED_SW IS

BEGIN

LED<=SW;

END one;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SEG7 IS

PORT (

SW :IN STD_LOGIC_VECTOR(3 DOWNTO 0);

EN :IN STD_LOGIC;

SEG :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

DIG :OUT STD_LOGIC

);

END ENTITY;

ARCHITECTURE ONE OF SEG7 IS

BEGIN

PROCESS(SW)

BEGIN

CASE SW IS

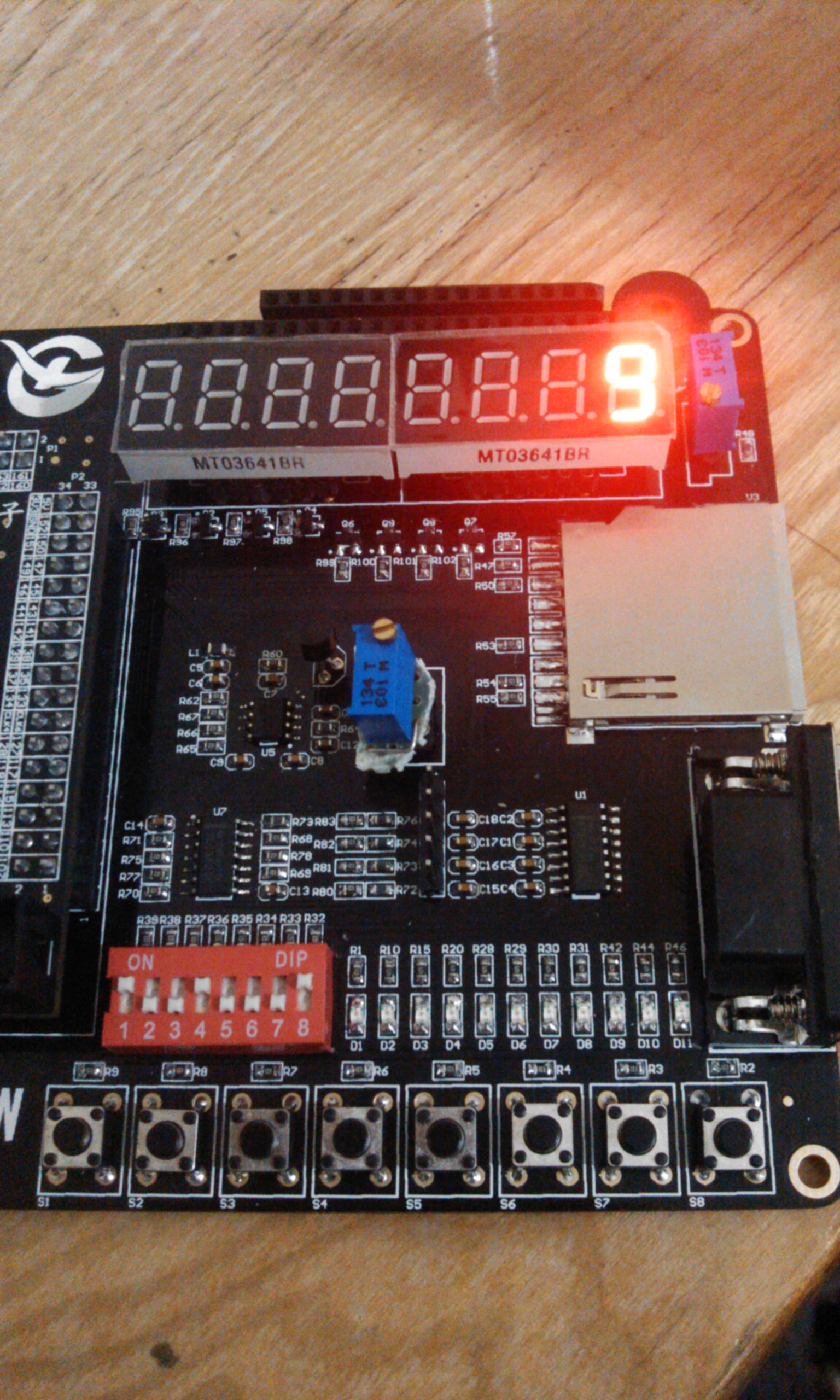

WHEN "1111" => SEG <= "11000000";--0

WHEN "1110" => SEG <= "11111001";--1

WHEN "1101" => SEG <= "10100100";--2

WHEN "1100" => SEG <= "10110000";--3

WHEN "1011" => SEG <= "10011001";--4

WHEN "1010" => SEG <= "10010010";--5

WHEN "1001" => SEG <= "10000010";--6

WHEN "1000" => SEG <= "11111000";--7

WHEN "0111" => SEG <= "10000000";--8

WHEN "0110" => SEG <= "10010000";--9

WHEN "0101" => SEG <= "11001000";--A

WHEN "0100" => SEG <= "10000011";--B

WHEN "0011" => SEG <= "11000110";--C

WHEN "0010" => SEG <= "10100001";--D

WHEN "0001" => SEG <= "10000110";--E

WHEN "0000" => SEG <= "10001110";--F

WHEN OTHERS => SEG <= "11111111";--

END CASE;

END PROCESS; --enable

DIG<=EN;

END ONE;