代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY decl7s IS

PORT(

-- d: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --输入4位二进制码

d: in std_logic;

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --七段译码输?

dig: out std_logic_vector(7 downto 0)

);

END;

ARCHITECTURE ONE OF decl7s IS

signal bcd: std_logic_vector(3 downto 0);

SIGNAL seg_r:STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管输出寄存器

signal dig_r:std_logic_vector(7 downto 0);

BEGIN

seg<=seg_r; --输出数码管译码结果

dig<=dig_r;

PROCESS(d) --七段译码

BEGIN

--seg_r<="11111111";

if d'event and d='1' then

bcd<=bcd+1;

dig_r<="00000000";

--seg_r<="11111111";

CASE bcd IS

WHEN X"0"=> seg_r<=X"c0";--显示0

WHEN X"1"=> seg_r<=X"f9";--显示1

WHEN X"2"=> seg_r<=X"a4";--显示2

WHEN X"3"=> seg_r<=X"b0";--显示3

WHEN X"4"=> seg_r<=X"99";--显示4

WHEN X"5"=> seg_r<=X"92";--显示5

WHEN X"6"=> seg_r<=X"82";--显示6

WHEN X"7"=> seg_r<=X"f8";--显示7

WHEN X"8"=> seg_r<=X"80";--显示8

WHEN X"9"=> seg_r<=X"90";--显示9

WHEN X"a"=> seg_r<=X"88";--显示a

WHEN X"b"=> seg_r<=X"83";--显示b

WHEN X"c"=> seg_r<=X"c6";--显示c

WHEN X"d"=> seg_r<=X"a1";--显示d

WHEN X"e"=> seg_r<=X"86";--显示e

WHEN X"f"=> seg_r<=X"8e";--显示f

WHEN OTHERS=> null;

END CASE;

end if;

END PROCESS;

END

由于我们这次活动的板子做交通灯有一定的局限性,所以我就自己焊接了个交通灯,在这个过程中我遇到些小问题:

我用的原理图是如下:

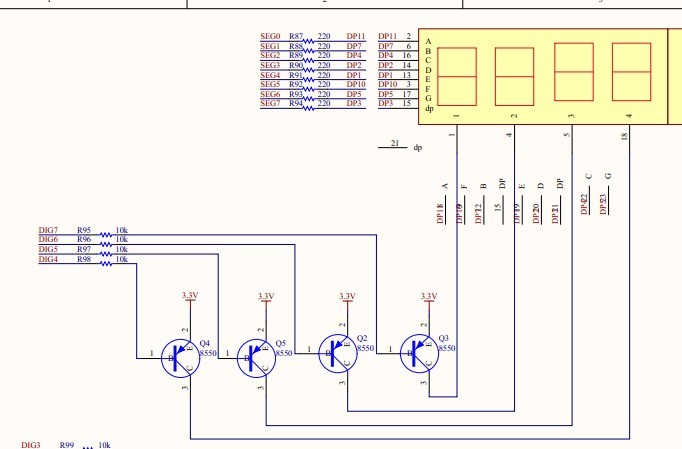

数码管部分:

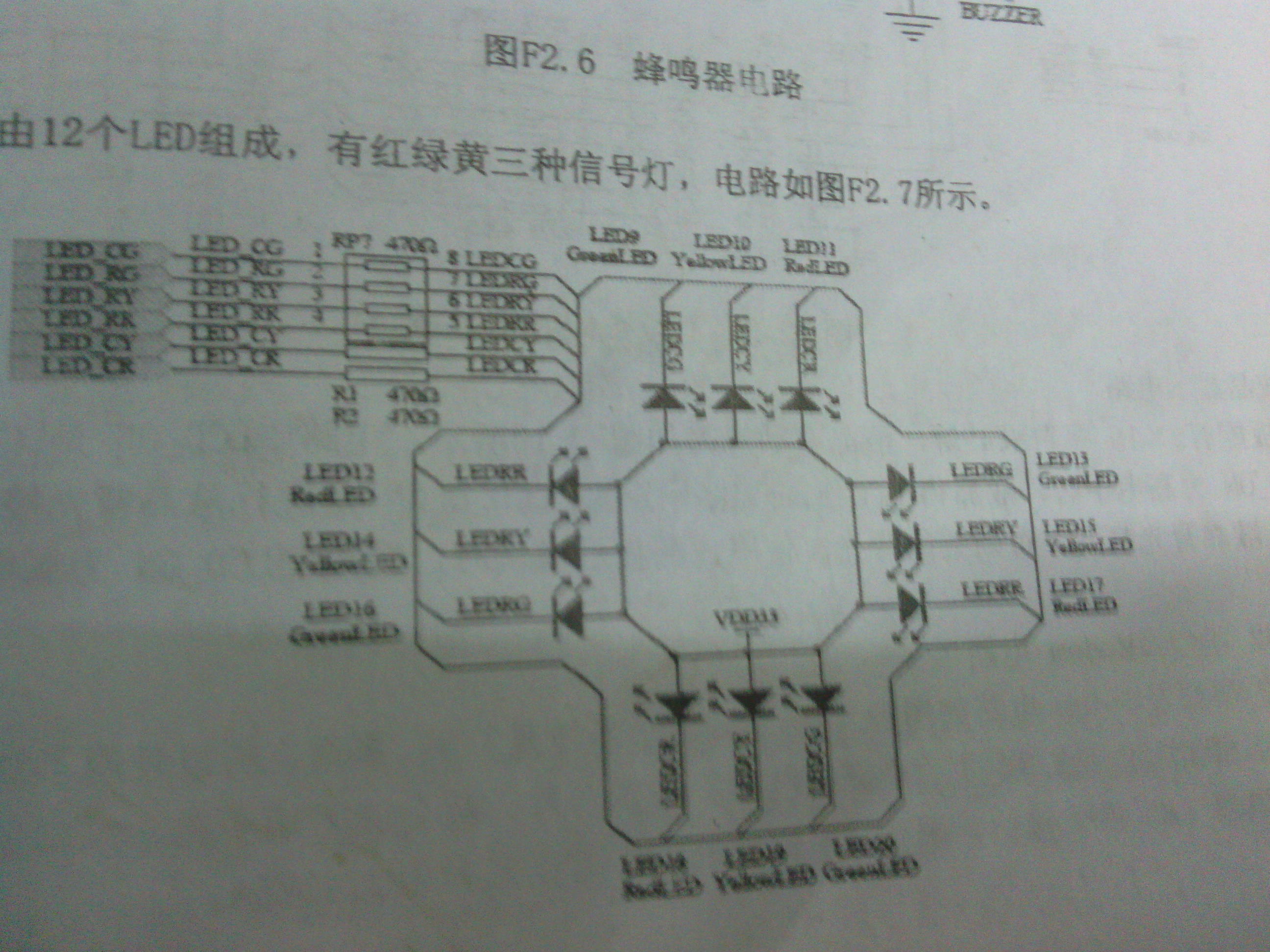

LED部分:

按照上图我将元器件焊接到万用板上,并且和FPGA的核心板连接好,下载程序后发现一个一个问题,那就是数码管没用任何反应,当时很郁闷,还以为是哪里没有接好,所以检查了好几遍,还是没用,我不经意把3.3V电源线拔掉,发现数码管有很暗的显示,很难看清,于是我想是不是原图有什么问题。由于我用的数码管是共阴极,而上面数码管部分图是共阳,这样就有问题了,当时我问@啸风:上面这个数码管图可以用共阴极的数码管吗?他告诉我不可以,所以我就想,把数码管接入的3.3V电源接地可不可以,经过修改后果然是这样。

通过这件事告诉我们要多动手,有问题多想办法去解决,这样才有进步!

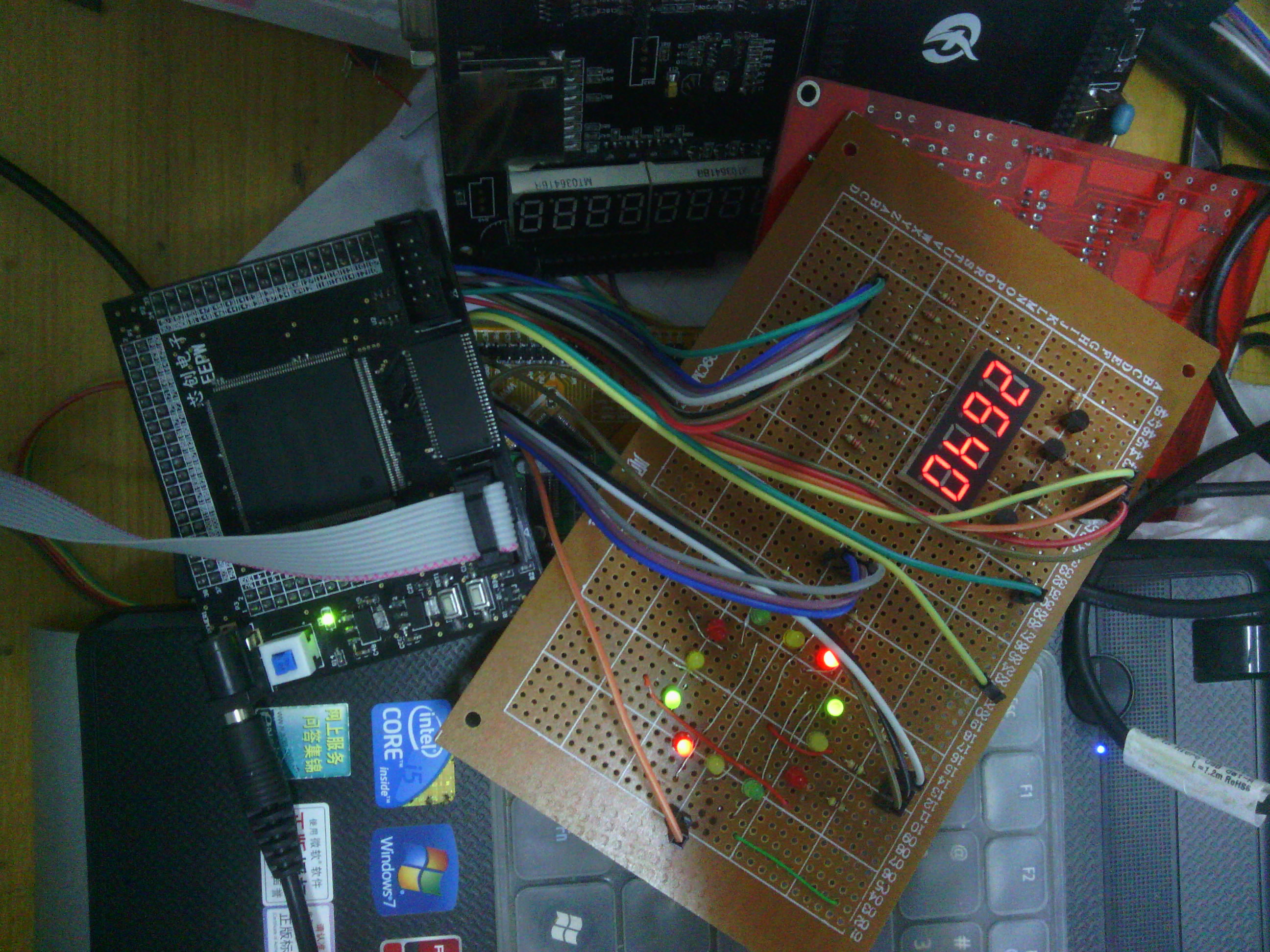

下面是我做好的FPGA交通灯:

交通灯演示视频:

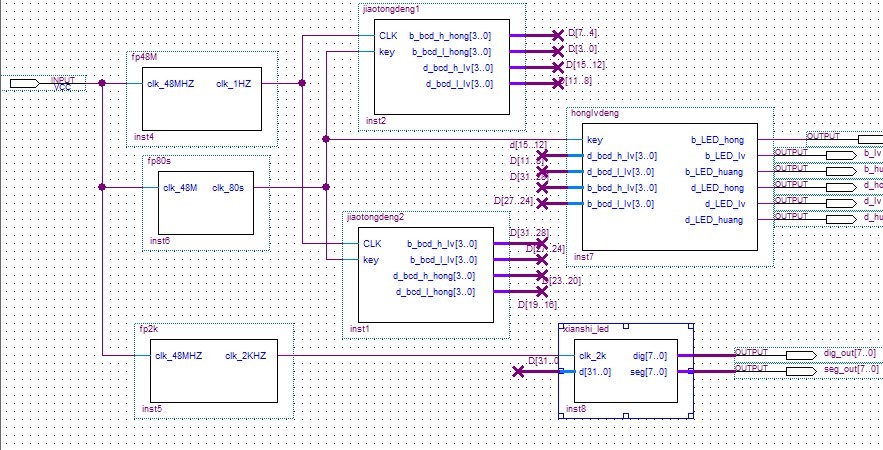

交通灯程序设计如下:

分频模块:由三个分频组成:1、1HZ分频,2、2KHZ分频,为数码管提供,3、分出80秒循环程序。

下面是一个1HZ分频程序,其他两个都可以这样分频。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity fp48M is

port(clk_48MHZ: in std_logic;

clk_1HZ: out std_logic

);

end fp48M;

architecture behav of fp48M is

signal clk_1HZ_r: std_logic;

signal count : std_logic_vector(24 downto 0);

begin

process (clk_48MHZ)

begin

if clk_48MHZ'event and clk_48MHZ='1' then

if count="1011011100011010111111111"then

count<=(others=>'0');

clk_1HZ_r<=not clk_1HZ_r;

else count<=count+1;

clk_1HZ<=clk_1HZ_r;

end if;

end if;

end process;

end behav;

控制数码管显示程序:两个方向可以分两个模块写:

下面提供一个方向的程序。另一个同理:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH;

entity jiaotongdeng1 IS

PORT (CLK,key: IN STD_LOGIC;

b_bcd_h_hong : out std_logic_vector(3 downto 0);

b_bcd_l_hong : out std_logic_vector(3 downto 0);

d_bcd_h_lv:out std_logic_vector(3 downto 0);

d_bcd_l_lv:out std_logic_vector(3 downto 0));

END jiaotongdeng1 ;

ARCHITECTURE behave OF jiaotongdeng1 IS

signal b_bcd_h_hong_r : std_logic_vector(3 downto 0);

signal b_bcd_l_hong_r : std_logic_vector(3 downto 0);

signal d_bcd_h_lv_r: std_logic_vector(3 downto 0);

signal d_bcd_l_lv_r: std_logic_vector(3 downto 0);

begin

u1:process(clk,key)

begin

if clk'event and clk='1' then

if key='1' then

if b_bcd_l_hong_r<="0000"then

b_bcd_h_hong_r(3 downto 0)<= b_bcd_h_hong_r(3 downto 0)-1;

b_bcd_l_hong_r<="1001";

else

b_bcd_l_hong_r(3 downto 0)<= b_bcd_l_hong_r(3 downto 0)-1;

end if;

else

b_bcd_h_hong_r<="0100";

b_bcd_l_hong_r<="0000";

end if;

end if;

end process;

b_bcd_h_hong<=b_bcd_h_hong_r;

b_bcd_l_hong<=b_bcd_l_hong_r;

u2:process(clk,key)

begin

if clk'event and clk='1' then

if key='1' then

if d_bcd_l_lv_r<="0000"then

d_bcd_h_lv_r(3 downto 0)<= d_bcd_h_lv_r(3 downto 0)-1;

d_bcd_l_lv_r<="1001";

else

d_bcd_l_lv_r(3 downto 0)<= d_bcd_l_lv_r(3 downto 0)-1;

end if;

else

d_bcd_h_lv_r<="0100";

d_bcd_l_lv_r<="0000";

end if;

end if ;

end process;

d_bcd_h_lv<=d_bcd_h_lv_r;

d_bcd_l_lv<=d_bcd_l_lv_r;

end behave;

红绿灯切换模块!

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH;

ENTITY honglvdeng IS

PORT (key: IN STD_LOGIC;

d_bcd_h_lv: in std_logic_vector(3 downto 0);

d_bcd_l_lv: in std_logic_vector(3 downto 0);

b_bcd_h_lv: in std_logic_vector(3 downto 0);

b_bcd_l_lv: in std_logic_vector(3 downto 0);

b_LED_hong,b_LED_lv,b_LED_huang :OUT STD_LOGIC;

d_LED_hong,d_LED_lv,d_LED_huang :OUT STD_LOGIC);

END honglvdeng;

ARCHITECTURE behave OF honglvdeng IS

--signal b_LED_hong_r,b_LED_lv_r,b_LED_huang_r : STD_LOGIC;

--signal d_LED_hong_r,d_LED_lv_r,d_LED_huang_r : STD_LOGIC;

begin

process(key)

variable b_LED_hong_r,b_LED_lv_r,b_LED_huang_r : STD_LOGIC;

variable d_LED_hong_r,d_LED_lv_r,d_LED_huang_r : STD_LOGIC;

begin

if key='1'then

b_led_hong_r:='0';

b_led_lv_r:='1';

b_led_huang_r:='1';

d_led_lv_r:='0';

d_led_huang_r:='1';

d_led_hong_r:='1';

if d_bcd_h_lv="0000" and d_bcd_l_lv<"0101" then

d_led_lv_r:='1';

d_led_huang_r:='0';

end if;

end if;

b_led_hong<=b_led_hong_r;

b_led_lv<=b_led_lv_r;

b_led_huang<=b_led_huang_r;

d_led_hong<=d_led_hong_r;

d_led_lv<=d_led_lv_r;

d_led_huang<=d_led_huang_r;

if key='0'then

d_led_hong_r:='0';

d_led_lv_r:='1';

d_led_huang_r:='1';

b_led_lv_r:='0';

b_led_hong_r:='1';

b_led_huang_r:='1';

if b_bcd_h_lv="0000" and b_bcd_l_lv<"0101" then

b_led_lv_r:='1';

b_led_huang_r:='0';

end if;

end if;

b_led_hong<=b_led_hong_r;

b_led_lv<=b_led_lv_r;

b_led_huang<=b_led_huang_r;

d_led_hong<=d_led_hong_r;

d_led_lv<=d_led_lv_r;

d_led_huang<=d_led_huang_r;

end process;

end behave;

数码管动态显示模块:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY xianshi_led IS

PORT(

clk_2k: IN STD_LOGIC;

d: IN STD_LOGIC_VECTOR(31 DOWNTO 0); --输入要显示的数据

dig: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管选择输出引脚

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --数码管段输出引脚

);

END ENTITY;

ARCHITECTURE one OF xianshi_led IS

SIGNAL seg_r: STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管输出寄存器

SIGNAL dig_r: STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管选择输出寄存器

SIGNAL disp_dat: STD_LOGIC_VECTOR(3 DOWNTO 0); --定义显示数据寄存器

SIGNAL count: STD_LOGIC_VECTOR(2 DOWNTO 0); --定义计数寄存器

BEGIN

dig<=dig_r;

seg<=seg_r;

PROCESS(clk_2k)

BEGIN

IF RISING_EDGE(clk_2k) THEN

count<=count+1;

END IF;

END PROCESS;

PROCESS(clk_2k)

BEGIN

IF RISING_EDGE(clk_2k) THEN

CASE count IS

WHEN "000"=> disp_dat<=d(31 DOWNTO 28); --第一个数码管

WHEN "001"=> disp_dat<=d(27 DOWNTO 24); --第二个数码管

WHEN "010"=> disp_dat<=d(23 DOWNTO 20); --第三个数码管

WHEN "011"=> disp_dat<=d(19 DOWNTO 16); --第四个数码管

WHEN "100"=> disp_dat<=d(15 DOWNTO 12); --第五个数码管

WHEN "101"=> disp_dat<=d(11 DOWNTO 8); --第六个数码管

WHEN "110"=> disp_dat<=d(7 DOWNTO 4); --第七个数码管

WHEN "111"=> disp_dat<=d(3 DOWNTO 0); --第八个数码管

END CASE;

CASE count IS --选择数码管显示位

WHEN "000"=> dig_r<="01111111"; --选择第一个数码管显示

WHEN "001"=> dig_r<="10111111"; --选择第二个数码管显示

WHEN "010"=> dig_r<="11011111"; --选择第三个数码管显示

WHEN "011"=> dig_r<="11101111"; --选择第四个数码管显示

WHEN "100"=> dig_r<="11110111"; --选择第五个数码管显示

WHEN "101"=> dig_r<="11111011"; --选择第六个数码管显示

WHEN "110"=> dig_r<="11111101"; --选择第七个数码管显示

WHEN "111"=> dig_r<="11111110"; --选择第八个数码管显示

END CASE;

END IF;

END PROCESS;

PROCESS(disp_dat)

BEGIN

CASE disp_dat IS

WHEN X"0"=> seg_r<=X"3f";--显示0

WHEN X"1"=> seg_r<=X"06";--显示1

WHEN X"2"=> seg_r<=X"5b";--显示2

WHEN X"3"=> seg_r<=X"4f";--显示3

WHEN X"4"=> seg_r<=X"66";--显示4

WHEN X"5"=> seg_r<=X"6d";--显示5

WHEN X"6"=> seg_r<=X"7d";--显示6

WHEN X"7"=> seg_r<=X"07";--显示7

WHEN X"8"=> seg_r<=X"7f";--显示8

WHEN X"9"=> seg_r<=X"6f";--显示9

WHEN X"a"=> seg_r<=X"77";--显示a

WHEN X"b"=> seg_r<=X"7c";--显示b

WHEN X"c"=> seg_r<=X"39";--显示c

WHEN X"d"=> seg_r<=X"5e";--显示d

WHEN X"e"=> seg_r<=X"79";--显示e

WHEN X"f"=> seg_r<=X"71";--显示f

--WHEN X"0"=> seg_r<=X"c0";--显示0

-- WHEN X"1"=> seg_r<=X"f9";--显示1

--WHEN X"2"=> seg_r<=X"a4";--显示2

-- WHEN X"3"=> seg_r<=X"b0";--显示3

-- WHEN X"4"=> seg_r<=X"99";--显示4

-- WHEN X"5"=> seg_r<=X"92";--显示5

-- WHEN X"6"=> seg_r<=X"82";--显示6

-- WHEN X"7"=> seg_r<=X"f8";--显示7

-- WHEN X"8"=> seg_r<=X"80";--显示8

-- WHEN X"9"=> seg_r<=X"90";--显示9

-- WHEN X"a"=> seg_r<=X"88";--显示a

--WHEN X"b"=> seg_r<=X"83";--显示b

-- WHEN X"c"=> seg_r<=X"c6";--显示c

-- WHEN X"d"=> seg_r<=X"a1";--显示d

-- WHEN X"e"=> seg_r<=X"86";--显示e

-- WHEN X"f"=> seg_r<=X"8e";--显示f

END CASE;

END PROCESS;

END

总模块图:

由动态显示代码和分频组成:分频代码以前公布过这次就不公布。

动态显示代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY decl7s IS

PORT(

-- d: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --输入4位二进制码

clk: in std_logic;

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --七段译码输?

dig: out std_logic_vector(7 downto 0)

);

END;

ARCHITECTURE ONE OF decl7s IS

signal bcd: std_logic_vector(3 downto 0);

SIGNAL seg_r:STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管输出寄存器

signal dig_r:std_logic_vector(7 downto 0);

BEGIN

seg<=seg_r; --输出数码管译码结果

dig<=dig_r;

PROCESS(clk) --七段译码

BEGIN

--seg_r<="11111111";

if clk'event and clk='1' then

bcd<=bcd+1;

dig_r<="00000000";

--seg_r<="11111111";

CASE bcd IS

WHEN X"0"=> seg_r<=X"c0";--显示0

WHEN X"1"=> seg_r<=X"f9";--显示1

WHEN X"2"=> seg_r<=X"a4";--显示2

WHEN X"3"=> seg_r<=X"b0";--显示3

WHEN X"4"=> seg_r<=X"99";--显示4

WHEN X"5"=> seg_r<=X"92";--显示5

WHEN X"6"=> seg_r<=X"82";--显示6

WHEN X"7"=> seg_r<=X"f8";--显示7

WHEN X"8"=> seg_r<=X"80";--显示8

WHEN X"9"=> seg_r<=X"90";--显示9

WHEN X"a"=> seg_r<=X"88";--显示a

WHEN X"b"=> seg_r<=X"83";--显示b

WHEN X"c"=> seg_r<=X"c6";--显示c

WHEN X"d"=> seg_r<=X"a1";--显示d

WHEN X"e"=> seg_r<=X"86";--显示e

WHEN X"f"=> seg_r<=X"8e";--显示f

WHEN OTHERS=> null;

END CASE;

end if;

END PROCESS;

END;

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |