led_2<=~led_2;改为led_2=8'b11111111;led_2=~led_2;灯就不会亮了,为什么?如果说这是信号的赋值符号,那为什么其余三个 led_yellow=led_yellow; led_red=led_red; led_green=led_green;就没有问题????

还有就是把@(posedge sys_clk)去掉,也不行,这又是为什么,如果去掉的话难道不是每个时钟周期去执行完一行代码吗?跟加上的区别又在哪里?

module led_2

(led_2,

led_green,

led_red,

led_yellow,

sys_clk);

output [8:1] led_2;

output led_red;

output led_green;

output led_yellow;

input sys_clk;

reg [8:1] led_2;

reg flag;

reg flag_times;

reg [27:0] delay_ms;

reg led_red;

reg led_green;

reg led_yellow;

always@(posedge sys_clk)

begin

if(delay_ms>28'd50999999)

delay_ms=28'd0;

else delay_ms=delay_ms+1;

end

always@(posedge sys_clk)

begin

led_2<=8'b11111111;

if (delay_ms==28'd50999999)

begin

led_2<=~led_2;

led_yellow=~led_yellow;

led_red=~led_red;

led_green=~led_green;

end

else

begin

led_2<=led_2;

led_yellow=led_yellow;

led_red=led_red;

led_green=led_green;

end

end

endmodule

----------------------

上面的帖子是11月18号写的,后来也没有人给出直接的回复,这两天自己仿真了一下,结果跟大家一起讨论分享。

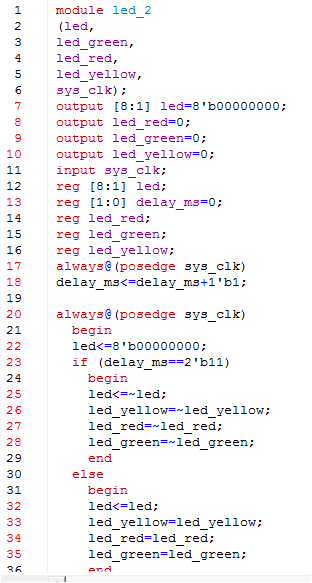

首先为了仿真方便,我把code里的reg [27:0] delay_ms;值缩小了

直接上仿真波形,,如果led的值为0,执行取反操作后,led变为1,

可以看出,跟单片机不同的时,即使一个时钟周期下,所有的代码都会被执行到

同时发现else begin下的led<=led的赋值优先权竟然高于第一句的led<=8'b00000000;

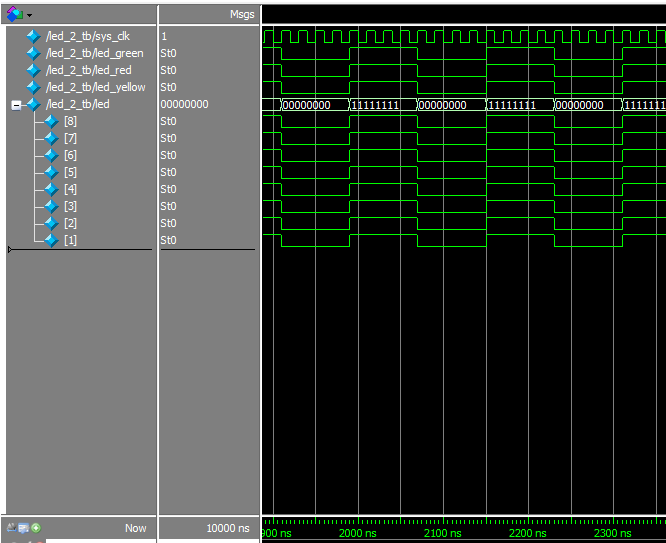

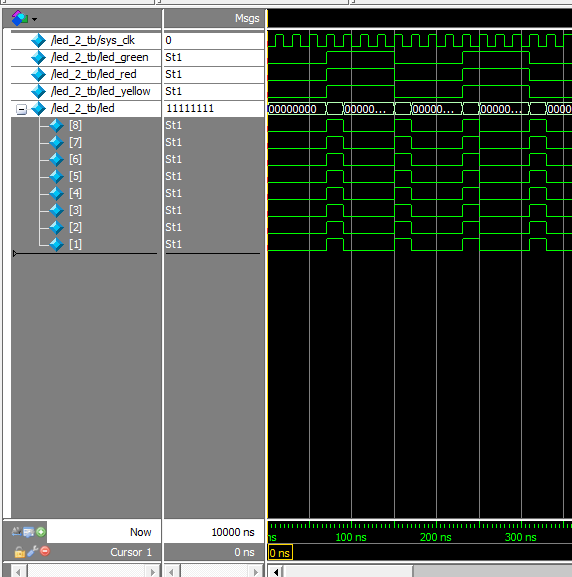

如果将上面的程序中按照我说的,改为led=8'b00000000;led=~led;仿真结果如下图所示

可以看出,led的高电平只是持续了一个周期,执行完if (delay_ms==2'b11);后,下一个时钟沿时先去执行led=8'b00000000;(阻塞语句),然后再执行后面的语句。

但是即使有先后,也会在一个时钟周期内执行,这点跟单片机确实不一样。

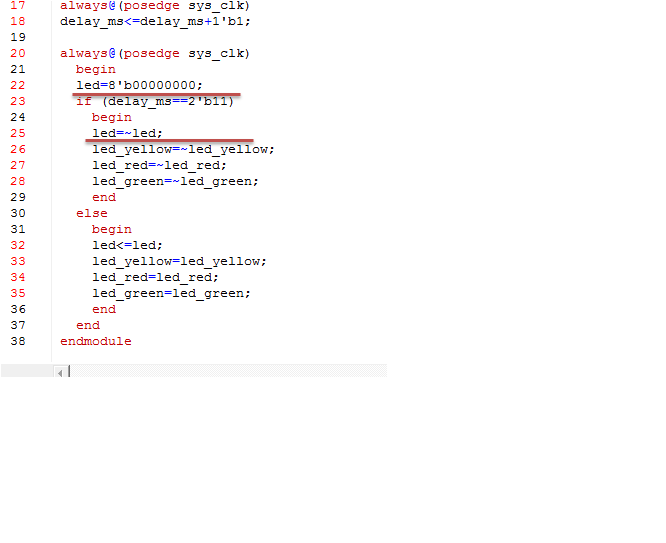

再次回到我原来的问题,这一部分模块就是让灯大约1s亮一次但是如果把 下面标示红色的两句led_2<=8'b11111111;

led_2<=~led_2;改为led_2=8'b11111111;led_2=~led_2;灯就不会亮了,为什么?

其实灯只是亮了一个时钟周期,也就是20ns,人眼是不会发觉的

同时在仿真中发现,下面的这些值应该设定初始值,否则仿真不成功

这也说明芯片在实际工作时,若不设定初始值,会默认为低电平

output [8:1] led=8'b00000000;

output led_red=0;

output led_green=0;

output led_yellow=0;

reg [1:0] delay_ms=0;

我要赚赏金

我要赚赏金