always块里边语句执行顺序问题

3楼

实验了一下 确实如此

在一个always块里边连续对一个寄存器两次赋值。

出来的结果是最后一次的赋值。中间不会发生信号变化什么的

在一个always块里边连续对一个寄存器两次赋值。

出来的结果是最后一次的赋值。中间不会发生信号变化什么的

6楼

无论是阻塞还是非阻塞赋值,最终结果都是一样的。

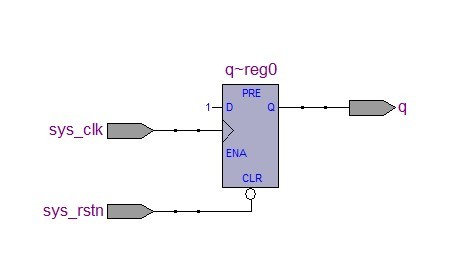

像下边这段,出来的波形就是最后一句的。

所以,期望always里边顺序执行是不可能的了

always @(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

q <= 0;

else

begin

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

//q=1'b0;

end

end

像下边这段,出来的波形就是最后一句的。

所以,期望always里边顺序执行是不可能的了

always @(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

q <= 0;

else

begin

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

q=1'b0;

q=1'b1;

//q=1'b0;

end

end

7楼

我认为在这里还应该注意的是:always块内是阻塞赋值还是非阻塞赋值,虽然边沿到来之后always块内的语句都执行。但是阻塞和非阻塞还是不同的。

比如

always@(posedge clk)

begin

b = a ;

c = b ;

end

和

always@ (posedge clk)

begin

b <= a;

c <= b;

end

是不同的。

假设 a = 0、b =1;

第一段的结果是 c =b=a=0;第二段结果是 b = a = 0,c = 1.

也就是说 阻塞赋值是在一条语句完成的时候,变量值就发生了变化。

而非阻塞赋值是在整个begin...end块结束后才开始赋值(把a的值给b的时候同时把b的值给c,这样b的值就没有覆盖。),在end之前只是描述了相互变量之间的逻辑关系。

9楼

被优化掉了。

我最后整成这样的了。将信号串行化。在需要写命令的地方,使用该模块

还没有完善,命令传入之后需要有一个信号控制着开始写入12864.命令成功执行之后,需要有一个信号作为反馈。这些还没做呢

/*************************************************

* Module Name : 向12864写命令

* Engineer : hanshuyujifen

* Target Device : EP2C5Q208C8

* Tool versions :

* Create Date :

* Revision : v1.0

* Description :

**************************************************/

module lcd_write_cmd(sys_clk,sys_rstn,isready,cs,rs,rw,cmddata,dataport);

input sys_clk,sys_rstn;

input [15:0] cmddata;

output isready;

output cs,rs,rw;

output [7:0] dataport;

reg [7:0] dataport;

reg isready;

reg clk1m; //1M时钟信号

//分频器,产生1M时钟

reg [4:0] cnt1;

always @(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

cnt1 <= 5'd0;

clk1m <= 1'd0;

end

else if(cnt1 == 5'd24)

begin

cnt1<= 5'd0;

clk1m <= ~clk1m;

end

else

begin

cnt1 <= cnt1+1'b1;

clk1m <= clk1m;

end

end

reg [5:0] delay_cnt;

always@(posedge clk1m or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt <= 6'd0;

else if(~isready)

begin

if(delay_cnt == 20)

delay_cnt<= 6'd0;

else

delay_cnt <= delay_cnt +1'b1;

end

end

//写命令

reg cs,rs,rw;

always @(posedge clk1m or negedge sys_rstn)

begin

if(!sys_rstn)

begin

cs<= 1'b0;

rs<= 1'b0;

rw<= 1'b0;

isready <= 1'b0;

dataport <= 8'd0;

end

else

begin

case(delay_cnt)

0: begin

cs = 0;

rs = 0;

end

1:

dataport = cmddata[15:8];

2:

begin

rw = 0;

end

3:

rw = 1;

4:

dataport = cmddata[7:0];

5:

rw = 0;

6:

begin

rw = 1;

cs = 1;

isready = 1;

end

endcase

end

end

endmodule

我最后整成这样的了。将信号串行化。在需要写命令的地方,使用该模块

还没有完善,命令传入之后需要有一个信号控制着开始写入12864.命令成功执行之后,需要有一个信号作为反馈。这些还没做呢

/*************************************************

* Module Name : 向12864写命令

* Engineer : hanshuyujifen

* Target Device : EP2C5Q208C8

* Tool versions :

* Create Date :

* Revision : v1.0

* Description :

**************************************************/

module lcd_write_cmd(sys_clk,sys_rstn,isready,cs,rs,rw,cmddata,dataport);

input sys_clk,sys_rstn;

input [15:0] cmddata;

output isready;

output cs,rs,rw;

output [7:0] dataport;

reg [7:0] dataport;

reg isready;

reg clk1m; //1M时钟信号

//分频器,产生1M时钟

reg [4:0] cnt1;

always @(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

cnt1 <= 5'd0;

clk1m <= 1'd0;

end

else if(cnt1 == 5'd24)

begin

cnt1<= 5'd0;

clk1m <= ~clk1m;

end

else

begin

cnt1 <= cnt1+1'b1;

clk1m <= clk1m;

end

end

reg [5:0] delay_cnt;

always@(posedge clk1m or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt <= 6'd0;

else if(~isready)

begin

if(delay_cnt == 20)

delay_cnt<= 6'd0;

else

delay_cnt <= delay_cnt +1'b1;

end

end

//写命令

reg cs,rs,rw;

always @(posedge clk1m or negedge sys_rstn)

begin

if(!sys_rstn)

begin

cs<= 1'b0;

rs<= 1'b0;

rw<= 1'b0;

isready <= 1'b0;

dataport <= 8'd0;

end

else

begin

case(delay_cnt)

0: begin

cs = 0;

rs = 0;

end

1:

dataport = cmddata[15:8];

2:

begin

rw = 0;

end

3:

rw = 1;

4:

dataport = cmddata[7:0];

5:

rw = 0;

6:

begin

rw = 1;

cs = 1;

isready = 1;

end

endcase

end

end

endmodule

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| OK1126B-S开发板下函数构建及步进电机驱动控制被打赏¥25元 | |

| 【S32K3XX】LPI2C 参数配置说明被打赏¥20元 | |

| OK1126B-S开发板的脚本编程及应用设计被打赏¥27元 | |

| 5v升压8.4v两节锂电池充电芯片,针对同步和异步的IC测试被打赏¥35元 | |

| 【S32K3XX】S32DS LPI2C 配置失败问题解决被打赏¥22元 | |

| 【S32K3XX】FLASH 的 DID 保护机制被打赏¥19元 | |

| OK1126B-S开发板串口通信及其使用被打赏¥18元 | |

| 【S32K3XX】多核 CORE ID 获取被打赏¥18元 | |

| OK1126B-S开发板的GPIO资源及其使用被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动屏幕(Arduino IDE环境)被打赏¥23元 | |