Quartus Ⅱ 9.0 使用教程(初级)

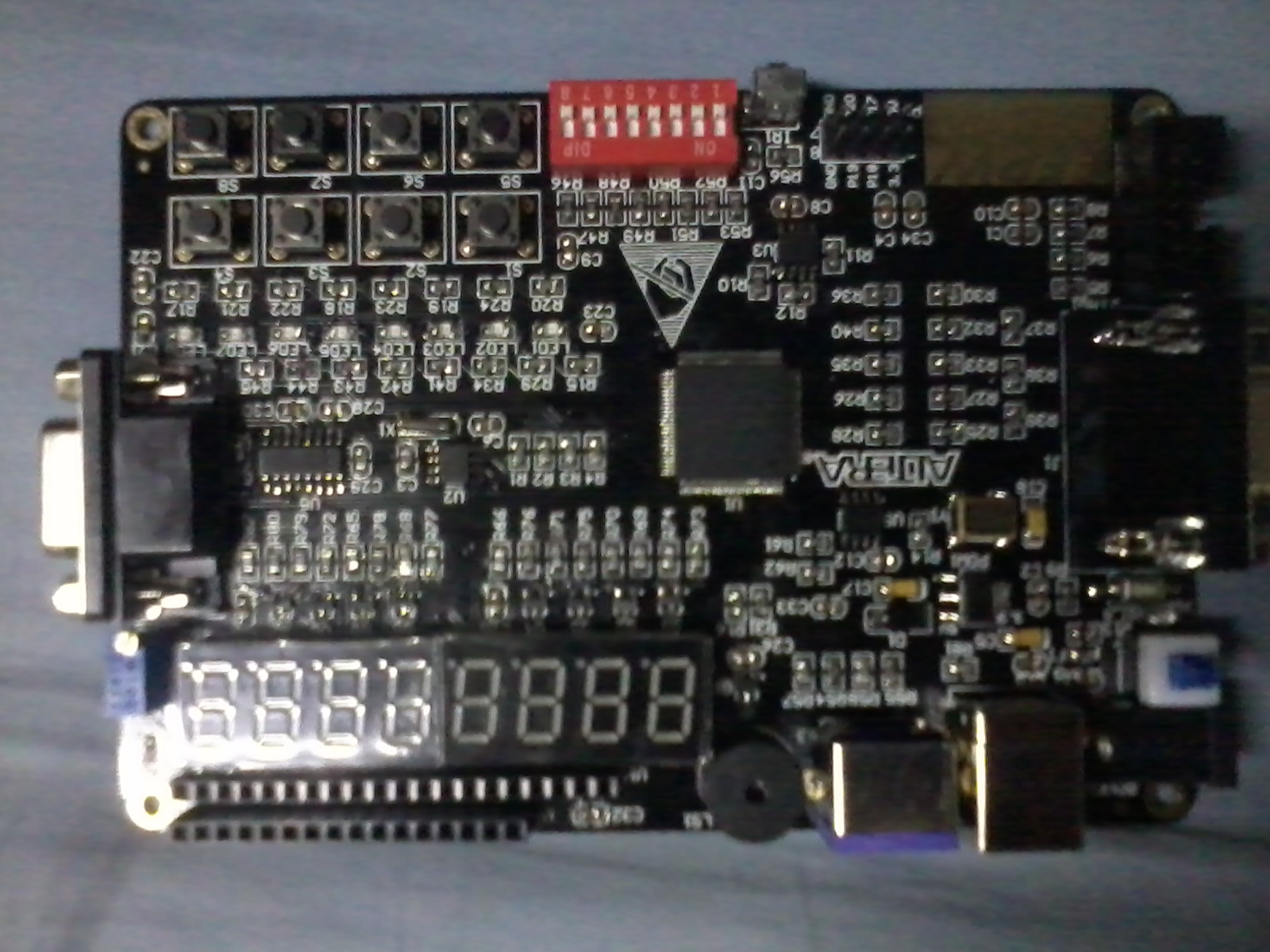

Quartus Ⅱ 是Altera公司推出的专业EDA工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。接下来我们对这种智能的EDA工具进行初步的学习。使大家以后的数字系统设计更加容易上手。

第一步:打开软件

l 快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

l 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

l 编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当 显示100%是表示编译或者综合通过。

l 信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard)

1 工程名称:

2添加已有文件(没有已有文件的直接跳过next)

3 选择芯片型号(我们选择MAX3000A系列下的EPM3256AQC208-10芯片)4 选择仿真,综合工具(第一次实验全部利用quartus做,三项都选None,然后next)

5 工程建立完成(点finish)

第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序

3-8译码器的VHDL描述源文件如下:

library ieee;

use ieee.std_logic_1164.all;

entity decoder3_8 is

port( A:in std_logic_vector(2 downto 0);

EN:in std_logic;

Y:out std_logic_vector(7 downto 0));

end decoder3_8;

architecture example_1 of decoder3_8 is

signal sel:std_logic_vector(3 downto 0);

begin

sel<=A & EN;

with sel select

Y <= "11111110" when "0001",

"11111101" when "0011",

"11111011" when "0101",

"11110111" when "0111",

"11101111" when "1001",

"11011111" when "1011",

"10111111" when "1101",

"01111111" when "1111",

"11111111" when others;

end example_1;

然后保存源文件;

第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis))

点击确定完成语法检查

第六步:(锁定引脚,点击工具栏的 (pin planner))

(pin planner))

双击location 为您的输入输出配置引脚(见管脚分配表)。

管脚分配表

|

信 号

|

实验板引出插孔标注

|

芯片引脚号

|

功能

|

|

EN

|

P43

|

69

|

I/O

|

|

A2

|

P76

|

7

|

I/O

|

|

A1

|

P75

|

8

|

I/O

|

|

A0

|

P74

|

9

|

I/O

|

|

Y0

|

P50

|

37

|

I/O

|

|

Y1

|

P51

|

36

|

I/O

|

|

Y2

|

P53

|

34

|

I/O

|

|

Y3

|

P54

|

33

|

I/O

|

|

Y4

|

P55

|

31

|

I/O

|

|

Y5

|

P57

|

28

|

I/O

|

|

Y6

|

P59

|

26

|

I/O

|

|

Y7

|

P61

|

24

|

I/O

|

第七步:整体编译(工具栏的按钮(start Complilation))

第八步:功能仿真(直接利用quratus进行功能仿真)

1 将仿真类型设置为功能仿真(setting>Simulator Settings>下拉>Function)

2 建立一个波形文件:

(new>Vector Waveform File)

然后导入引脚(双击Name下面空白区域>Node Finder>list>点击):

(以实现一个与门和或门为例,3-8译码器与以下的设计步骤类似)

接下来设置激励信号(单击>选择>Timing>Multiplied by 1)

设置b信号源的时候类同设置a信号源,最后一步改为Multiplied by 2

然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist)

接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):

观察波形,刚好符合我们的逻辑。功能仿真通过。

第九步:下载(点击(Programmer),再点击Hardware Setup配置下载电缆,单击弹出窗口的“Add Hardware”按钮,选择并口下载ByteBlasterMV or ByteBlasterMVⅡ,单击“Close”按钮完成设置。CPLD器件生成的下载文件后缀名为.pof,点击下图所示方框,选中下载文件,然后直接点击start按钮开始下载)

我要赚赏金

我要赚赏金