买开发板比较晚

一些安装细节就不上了

我安装出现的问题在选择USB-blaster驱动路径的时候

选择到了下一个子集单元 会出现无法安装的情况

套件光盘提供的内容很详细 出现问题可以查看视频 或咨询淘宝店主

进程<一> LED 的点亮

先建立一个文件夹方便对项目进行整合

保存为 LED.V

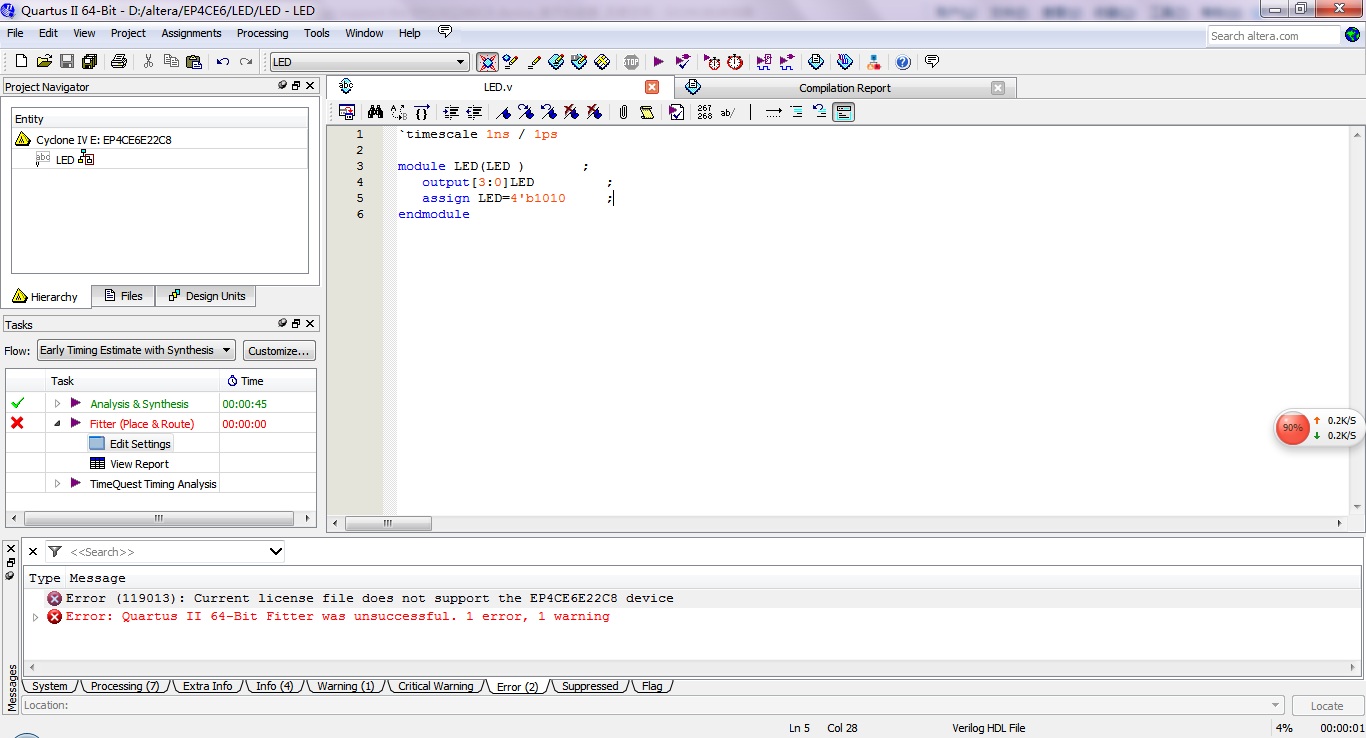

输入主程序 编译出现一个错误module led 与文件名不符 第一个错误 修改后编译出现以上图示错误

因为我未正确破解软件出现的 然后重新激活.....

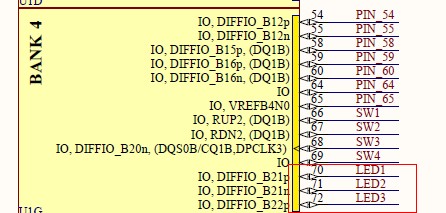

这个问题随之解决 然后定义输出引脚

然后进行全局编译

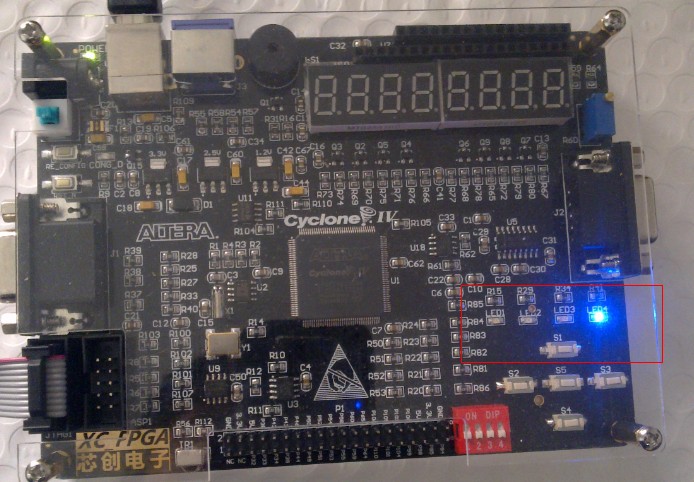

连接开发板和JTAG 进行下载

完成显示

注意[一]:定义自己的端口 默认从高到低

注意[二]:建立文件的根目录中 不能存在中文 会提示错误

提示[一]: sys_clk 系统时钟 全称The system clock sys_rstn是系统复位全称The system reset

clk为什么要用posedge,而不用negedge

Verilog中典型的counter逻辑是这样的:

always@(posedge clk or negedge reset) begin

if(reset == 1'b0)

reg_inst1 <= 8'd0;

else if(clk == 1'b1)

reg_inst1 <= reg_inst1 + 1'd1;

else

reg_inst1 <= reg_inst1;

end

clk为什么要用posedge,而不用negedge呢?请教丹内先生,答案如下:

- 一般情况下,系统中统一用posedge,避免用negedge,降低设计的复杂度,可以减少出错。

- 在ModelSim仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度不一样,甚至非周期性的微小波动。如果只使用posedge,则整个系统的节拍都按照clock上升延对齐,如果用到了negedge,则系统的节拍没有统一到一个点上。上升延到上升延肯定是一个时钟周期,但是上升延到下降延却很可能不是半个周期。这都会出现问题。

- FPGA特有的东西:Global CLK。FPGA内部有专门的CLK“线”,和一般的逻辑门的走法不一样,目的是为了保证整个FPGA片内的时钟一致,这个东西就叫Global CLK。

总结 :先熟悉编程规则和步骤。

然后根据例程实现效果。

完善并总结错误-----多研究错误信息如何导致和解决办法。

进程<二>蜂鸣器使用

有源蜂鸣器是只要通上直流电就会响的,但是它只能是以一种频率发出声音(即单音);而无源蜂鸣器是需要加上一定频率的电流才会发出声音,且通过改变频率可以让它发出不同的声音(即音乐)。

该开发板是无缘的蜂鸣器  不能发出声音

不能发出声音

进程更新中\\\\................. 进程会很快 一起学习的 可以加好友

我要赚赏金

我要赚赏金