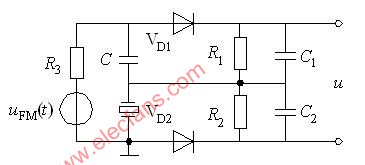

晶体鉴频器的原理电路如图7-55所示。电容C与晶体串联后接到调频信号源。VD1、R1 ,C1和VD2、R2、C2为两个二极管包络检波器。为了保证电路平衡,通常VD1与VD2性能相同,R1=R2,C1=C2。

晶体鉴频器原理电路

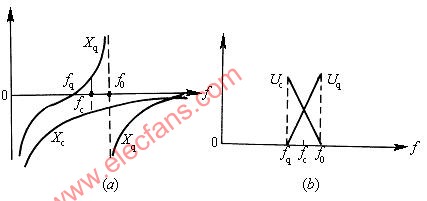

图7-56 电容—晶体分压器?

(a)电抗曲线;(b)电容、晶体两端电压变化曲线

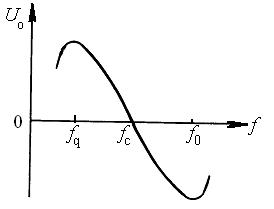

图7-57 晶体鉴频器的鉴频特性

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| OK1126B-S开发板下以导航按键控制云台/机械臂姿态调整被打赏¥29元 | |

| 【树莓派5】便携热成像仪被打赏¥36元 | |

| 【树莓派5】环境监测仪被打赏¥35元 | |

| OK1126B-S开发板下多时段语音提示型电子时钟被打赏¥27元 | |

| OK1126B-S开发板下函数构建及步进电机驱动控制被打赏¥25元 | |

| 【S32K3XX】LPI2C 参数配置说明被打赏¥20元 | |

| OK1126B-S开发板的脚本编程及应用设计被打赏¥27元 | |

| 5v升压8.4v两节锂电池充电芯片,针对同步和异步的IC测试被打赏¥35元 | |

| 【S32K3XX】S32DS LPI2C 配置失败问题解决被打赏¥22元 | |

| 【S32K3XX】FLASH 的 DID 保护机制被打赏¥19元 | |