LVDS信号电平特性

LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω 的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

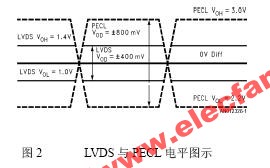

下图为LVDS与PECL(光收发器使用的电平)电平变化。

图2 LVDS与PECL电平图示

由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。85――1。55V之间,其由逻辑“0”电平到逻辑“1”电平变化的时间比TTL电平要快得多,所以LVDS更适合用来传输高速变化信号。其低压特点,功耗也低。

采用低压技术适应高速变化信号,在微电子设计中的例子很多,如:FPGA芯片的内核供电电压为2。5V或1.8V;PC机的CPU内核电压,PIII800EB为1.8V;数据传输领域中很多功能芯片都采用低电压技术。

我要赚赏金

我要赚赏金