也不算是完全完成了VGA篇的作业,只是把代码写好了,还没有来得及下载验证,因为手边没有VGA 线(这个都没有?!我的人生就是一个茶几,上面布满了各种杯具。。。![]() ),在网上买的还没到。就先把代码交了,请@51FPGA 及各位大神指点谬误。

),在网上买的还没到。就先把代码交了,请@51FPGA 及各位大神指点谬误。

代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: Charles Wang

//

// Create Date: 08/06/2014

// Design Name: VGA

// Module Name: VGA

// Project Name:VGA

// Target Devices: EP4CE6E22C8

// Tool versions: Quartus II 13.1

// Description: 实现VGA彩色信号显示(800 X 600 X 60Hz)

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// 部分代码移植自51FPGA源代码

//////////////////////////////////////////////////////////////////////////////////

module VGA(clk,rst_n,switch,hsync,vsync,disp_RGB);

input clk;//50 MHz 总线时钟

input rst_n;//异步复位,低电平有效

input [1:0]switch;//显示方式开关输入

output hsync;//行同步

output vsync;//场同步

output [2:0]disp_RGB;//RGB 输出

///////////////////////////寄存器及wire 定义//////////////////////////////////////////

reg [2:0]data;

reg [2:0]h_dat;

reg [2:0]v_dat;

reg [9:0]hcount;

reg [9:0]vcount;

wire vga_clk;

wire hcount_ov;

wire vcount_ov;

wire data_act;

wire hsync;

wire vsync;

////////////////////////////////////////////////////////////////////////////////////

PLL_VGA PLL(.inclk0(clk),.c0(vga_clk));//使用PLL IP核 产生40MHz vga_clk 时钟

////////////////////////////////////////////////////////////////////////////////////

parameter

hsync_end = 10'd127,

hdat_begin = 10'd215,

hdat_end = 10'd1015,

hpixel_end = 10'd1055,

vsync_end = 10'd3,

vdat_begin = 10'd26,

vdat_end = 10'd626,

vline_end = 10'd627;

always @(posedge vga_clk)

begin

if (hcount_ov)

hcount <= 10'd0;

else

hcount <= hcount + 10'd1;

end

assign hcount_ov = (hcount == hpixel_end);

//场扫描

always @(posedge vga_clk)

begin

if (hcount_ov)

begin

if (vcount_ov)

vcount <= 10'd0;

else

vcount <= vcount + 10'd1;

end

end

assign vcount_ov = (vcount == vline_end);

//数据、同步信号输

assign dat_act = ((hcount >= hdat_begin) && (hcount < hdat_end))

&& ((vcount >= vdat_begin) && (vcount < vdat_end));

assign hsync = (hcount > hsync_end);

assign vsync = (vcount > vsync_end);

assign disp_RGB = (dat_act) ? data : 3'h00;

//************************显示数据处理部分*******************************

always @(posedge vga_clk)

begin

case(switch[1:0])

2'd0: data <= h_dat; //选择横彩条

2'd1: data <= v_dat; //选择竖彩条

2'd2: data <= (v_dat ^ h_dat); //产生棋盘格

2'd3: data <= (v_dat ~^ h_dat); //产生棋盘格

endcase

end

always @(posedge vga_clk) //产生竖彩条

begin

if(hcount < 131)

v_dat <= 3'h7; //白

else if(hcount < 263)

v_dat <= 3'h6; //黄

else if(hcount < 395)

v_dat <= 3'h5; //青

else if(hcount < 527)

v_dat <= 3'h4; //绿

else if(hcount < 659)

v_dat <= 3'h3; //紫

else if(hcount < 791)

v_dat <= 3'h2; //红

else if(hcount < 923)

v_dat <= 3'h1; //蓝

else

v_dat <= 3'h0; //黑

end

always @(posedge vga_clk) //产生横彩条

begin

if(vcount < 79)

h_dat <= 3'h7; //白

else if(vcount < 158)

h_dat <= 3'h6; //黄

else if(vcount < 237)

h_dat <= 3'h5; //青

else if(vcount < 316)

h_dat <= 3'h4; //绿

else if(vcount < 395)

h_dat <= 3'h3; //紫

else if(vcount < 474)

h_dat <= 3'h2; //红

else if(vcount < 553)

h_dat <= 3'h1; //蓝

else

h_dat <= 3'h0; //黑

end

endmodule

由于我这里的ga_clk 是有PLL IP 核产生的,不知道怎么用modelsim 仿真,还请@51FPGA 及各位大神指点。

不过,到是对51FGPA 的源代码进行了仿真,请@51FPGA 及各位大神指点谬误,代码如下:

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: Charles Wang // // Create Date: 08/07/2014 // Design Name: vga_tb // Module Name: vga_tb // Project Name:vga_tb // Target Devices: EP4CE6E22C8 // Tool versions: Quartus II 13.1 // Description: VGA test bench // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module vga_tb(); reg clk; reg rst_n; reg [1:0]switch; wire [2:0]disp_RGB; wire hsync; wire vsync; VGA vga_test(.rst_n(rst_n),.clock(clk),.switch(switch),.disp_RGB(disp_RGB),.hsync(hsync),.vsync(vsync)); ///////////////////////////////////////////////////////////////////////////////// initial begin rst_n = 1'b0; #10 rst_n = 1'b1; #10 clk = 1'b0; forever begin #10 clk = ~clk; end end initial begin switch = 2'b00; #1000000 switch = 2'b01; #1000000 switch = 2'b10; #1000000 switch = 2'b11; end endmodule

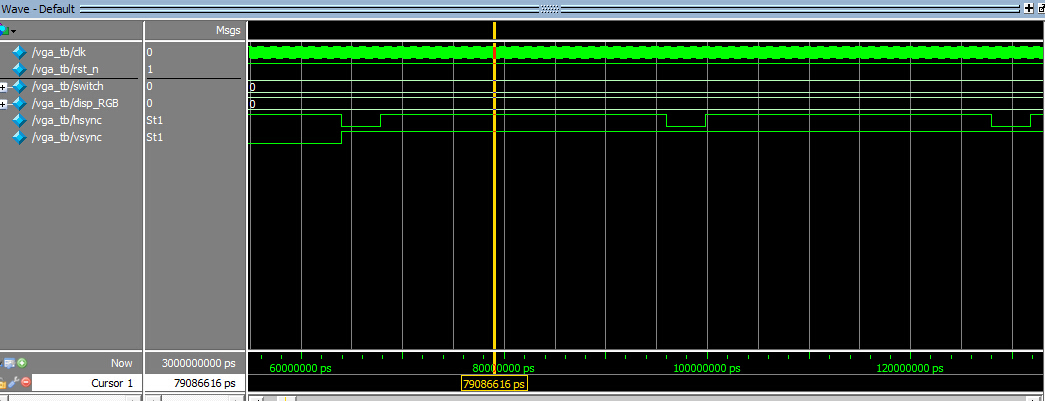

波形如下:

我要赚赏金

我要赚赏金