PWM

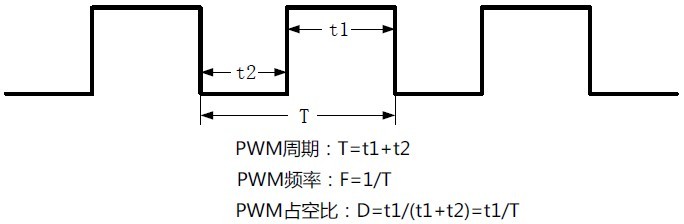

PWM---Pulse Width Modulation---脉宽调制,简单的描述就是一些矩形脉冲波形,PWM波形最重要的三个参数是周期、频率和占空比。PWM是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。#此前在首页部分显示#

PWM波形图

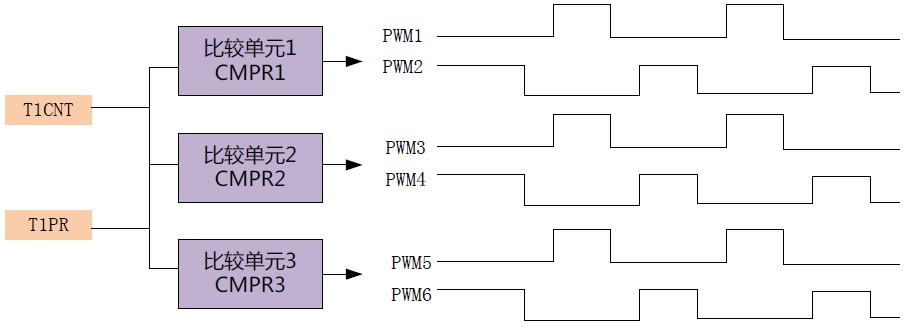

EVA的两个通用定时器能够产生2路独立的PWM波形—T1PWM和T2PWM,三个比较单元每一个都能产生一对互补的PWM波形,比较单元1产生PWM1和PWM2,比较单元2产生PWM3和PWM4,比较单元3产生PWM5和PWM6。这样,EVA一共能产生8路PWM波形。

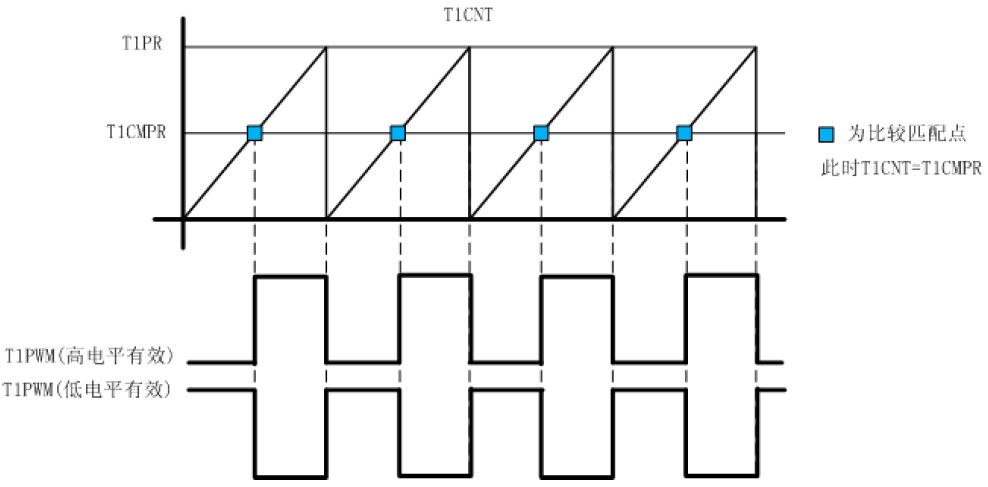

通用定时器产生的PWM波

T1和T2分别能够产生1路独立的PWM,以T1为例。当T1计数寄存器T1CNT的值和T1CMPR的值相等时,就会发生比较匹配事件,这时如果PWM的功能使能,则T1PWM引脚便可以输出PWM波形。T1能够产生两种类型的PWM,一种是不对称的PWM波形,一种是对称的PWM波形,取决于T1CNT的计数方式。

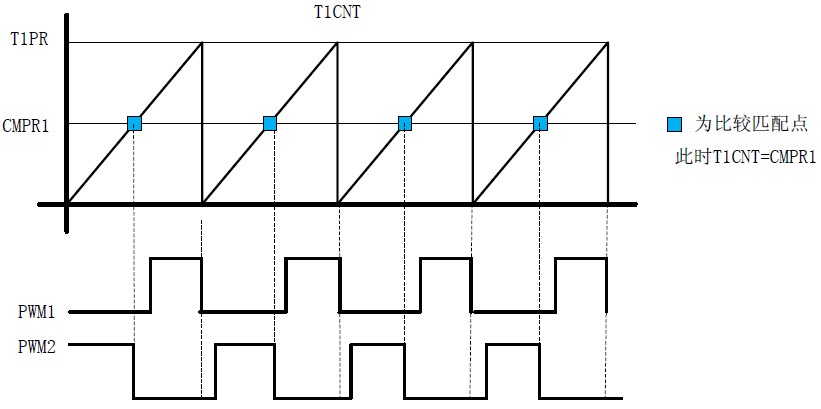

(1)当T1CNT为连续增计数时 ----- 不对称的PWM波形。

定时器T1工作于连续增模式。当T1CNT的值计数到和T1CMPR的值相等时,发生比较匹配事件。如果T1CON的第1位定时器比较使能为TECMPR为1,即定时器比较操作被使能,且GPTCONA的第6位比较输出使能位TCMPOE为1,同时GPTCONA下的T1PIN引脚输出极性为高电平或者低电平的话,T1PWM就会输出不对称的PWM波形

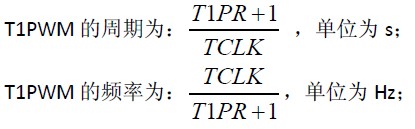

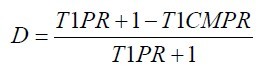

T1连续增模式,定时器的周期T=(T1PR+1)*tc,其中tc为T1CNT每计数1次所需的时间

TCLK为定时器时钟频率。分频系数决定

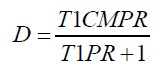

T1PWM的占空比要分GPTCONA中T1PIN的输出极性,

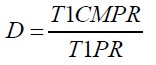

当T1PIN为高电平有效时,则占空比为:

当T1PIN为低电平有效时,PWM波形的占空比为:

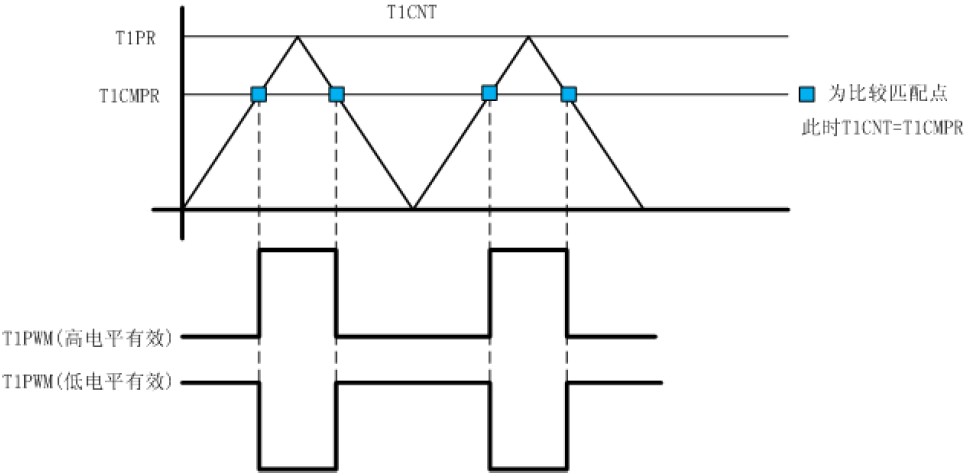

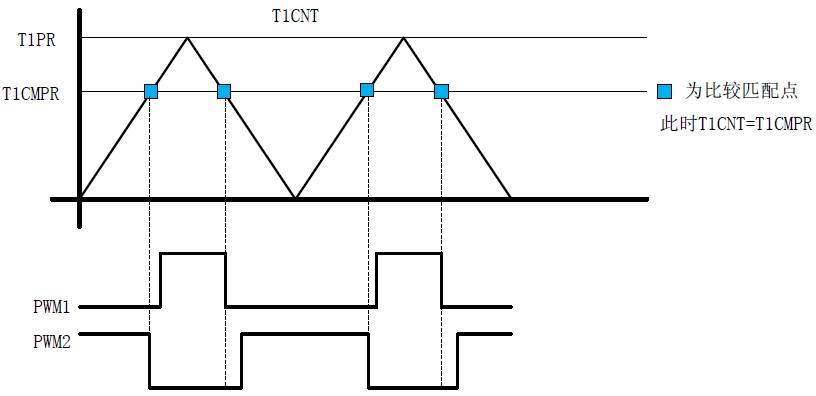

2)当T1CNT为连续增/减计数时 ----- 对称的PWM波形。

当定时器T1工作于连续增/减计数模式。当T1CNT的值计数到和T1CMPR的值相等时,发生比较匹配事件。如果T1CON的第1位定时器比较使能为TECMPR为1,即定时器比较操作被使能,且GPTCONA的第6位比较输出使能位TCMPOE为1,同时GPTCONA下的T1PIN引脚输出极性为高电平或者低电平的话,T1PWM就会输出对称的PWM波形。

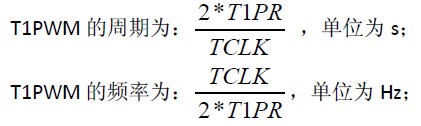

当T1工作于连续增/减计数模式时,T1CNT一个周期T=(2*T1PR)*tc,其中tc是T1CNT计一次数所花的时间,

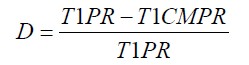

T1PWM的占空比要分GPTCONA中T1PIN的输出极性,

当T1PIN为高电平有效时,则占空比为:

当T1PIN为低电平有效时,PWM波形的占空比为:

(3)比较单元产生的可带有死区的PWM波形

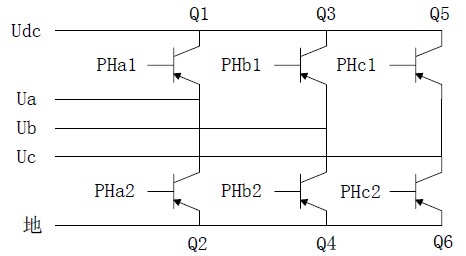

2812的EV还为我们提供了3个全比较单元,分别是比较单元1,比较单元2和比较单元3。这3个全比较单元每一个都能产生一对互补的PWM波形,也可以通过相应的寄存器设置死区时间。这样,使得EVA和EVB都有能力去驱动一个三相全桥电路。

三相全桥电路 桥理想驱动波形

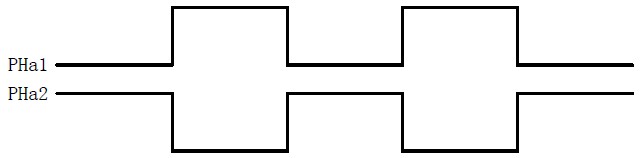

该电路由6个开关管组成,上下两个开关管组成1个桥壁。任何一个开关管在输入的PWM波形处于高电平时导通,处于低电平时关断。同一桥壁上的上下两个开关管不能同时导通,因为如果同时导通,电源和地就会短接,也就是会发生短路。因此,PHa1和PHa2,PHb1和PHb2,PHc1和PHc2必须都是互补的,

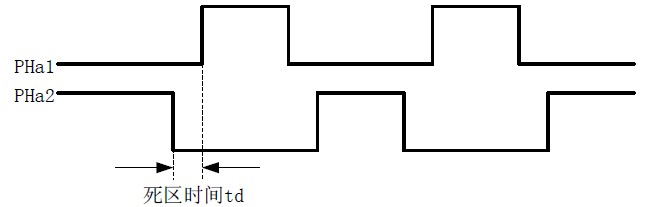

以PHa1和PHa2为例,理想情况下当PHa1为高电平时,PHa2为低电平;当PHa1为低电平时,PHa2为高电平PHa1为高电平时Q1导通,此时PHa2为低电平,Q2关闭,当PHa1从高电平转变为低电平时,Q1由导通变为关断,而此时Q2由关断变为导通,实际上开关管从导通转为关断的时候,总会有延时,这样,就会有一小段时间里面其实Q1和Q2都处于导通状态,这样是非常危险的。为了解决这个问题,我们通常要求上下管输出的驱动波形要具有一定的死区时间,上下桥壁中任何一个开关管从关断到导通都要经过1个死区时间的延时

带死区PWM波形

比较单元产生PWM的波形和定时器通过比较功能产生PWM波形的原理是类似的。只不过定时器中的比较寄存器T1CMPR,变成了比较单元的比较寄存器CMPR1。三个比较单元都是类似的,以比较单元1为例。比较单元产生PWM时,所相关的寄存器有T1PR,T1CNT,CMPR1,比较控制寄存器COMCONA和比较行为控制寄存器ACTRA。

比较单元的时基是由T1来提供的,因此我们用到的是T1PR和T1CNT,当T1CNT中的值和CMPR1中的值相等时,就发生了比较匹配。这时候,如果COMCONA的CENABLE为1,即比较操作被使能,FCMPOE为1,比较输出时各路PWM波形都由相应的比较逻辑来驱动,同时如果ACTRA中CMP1和CMP2的极性为低电平或者高电平有效的时候,就会产生两路互补的PWM波形,PWM1和PWM2。 和T1产生PWM一样,当T1工作于连续增计数模式时,比较单元1输出不对称的PWM波形,而当T1工作于连续增减计数模式时,比较单元1输出对称的PWM波形。

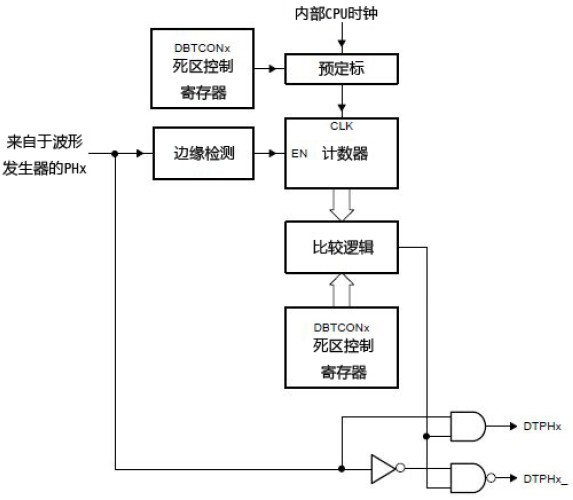

死区单元的模块图(x=1,2,3)

当比较单元的比较操作被使能,就会产生波形PHx。PHx经过死区单元,就会输出两路互补的带有死区的PWM波形DTPHx和DTPHx_。PHx、DTPHx、DTPHx_之间的关系,如果没有死区,那么DTPHx和DTPHx_应该是完全互补的。DTPHx的导通时刻是在PHx的基础上延时了1个死区时间,而关闭时刻未变。DTPHx_是在PHx取反的基础上,也将导通时间延迟了1个死区时间,而关断的时间没有发生改变。

死区时间的控制,死区控制寄存器DBTCONx的[11~8]死区定时器周期和DBTCON的[4~2]位死区定时器预定标因子。如果死区定时器周期为m,死区定时器预定标因子x/p,则死区的值就为(p*m)个CPU时钟周期。

比较单元1产生的不对称PWM波形---带死区

比较单元2产生的对称PWM波形---带死区

我要赚赏金

我要赚赏金