在高速数字电路设计中,由于趋肤效应、临近干扰、电流高速变化等因素,设计者不能单纯地从数字电路的角度来审查自己的产品,而要把信号看作不稳定的模拟信号。采用频谱分析仪对信号分析,可以发现,信号的高频谱线主要来自于信号的变化沿而不是信号频率。例如一个1MHz的信号,虽然时钟周期为1微秒,但是如果其变化沿上升或下降时间为纳秒级,则在频谱仪上可以观察到频率高达数百兆赫兹的谱线。因此,电路设计者应该更加关注信号的边沿,因为边沿往往也就是信号频谱最高、最容易受到干扰的地方。

在同步设计中,数据的读取需要基于时钟采样,根据以上分析,为了得到稳定的数据,时钟的采样点应该远离数据的变化沿。

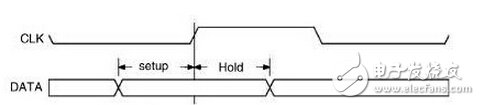

图1 信号采样实例

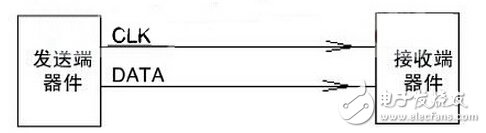

图2 源同步系统拓扑图

图1是利用时钟CLK的上升沿采样数据DATA的示例。DATA发生变化后,需要等待至少Setup时间(建立时间)才能被采样,而采样之后,至少Hold时间(保持时间)之内DATA不能发生变化。因此可以看出,器件的建立时间和保持时间的要求,正是为了保证时钟的采样点远离数据的变化沿。如果在芯片的输入端不能满足这些要求,那么芯片内部的逻辑将处于非稳态,功能出现异常。

时序分析中的关键参数

为了进行时序分析,需要从datasheet(芯片手册)中提取以下关键参数:

● Freq:时钟频率,该参数取决于对芯片工作速率的要求。

● Tcycle:时钟周期,根据时钟频率Freq的倒数求得。Tcycle=1/Freq。

● Tco:时钟到数据输出的延时。上文提到,输入数据需要采用时钟采样,而输出数据同样也需要参考时钟,不过一般而言,相比时钟,输出的数据需要在芯片内延迟一段时间,这个时间就称为Tco。该参数取决于芯片制造工艺。

● Tsetup(min):最小输入建立时间要求。

● Thold(min):最小输入保持时间要求。

除以上五个参数外,时序分析中还需要如下经验参数:

● Vsig:信号传输速度。信号在电路上传输,传输速度约为6英寸/纳秒。

时序计算的目标是得到以下两个参数之间的关系:

● Tflight-data:数据信号在电路板上的走线延时。

● Tflight-clk:时钟信号在电路板上的走线延时。

以上参数是进行时序分析的关键参数,对于普通的时序分析已经足够。

源同步系统的时序计算

源同步系统指数据和时钟是由同一个器件驱动发出的情况,下图是常见的源同步系统拓扑结构:

该系统的特点是,时钟和数据均由发送端器件发出,在接收端,利用接收到的时钟信号CLK采样输入数据信号DATA。

源同步系统的时序计算公式为:

TCO(max) + (Tflight-data - Tflight-clk)MAX + Tsetup(min) < Tcycle (式1)

TCO(min) + (Tflight-data - Tflight-clk)MIN >Thold(min) (式2)

时序计算的最终目标是获得Tflight-data - T flight-clk的允许区间,再基于该区间,通过Vsig参数,推算出时钟信号和数据信号的走线长度关系。

SPI4.2接口时序分析

SPI4.2(System Packet Interface Level4, Phase 2)接口是国际组织OIF制定的针对OC192(10Gbps)速率的接口。目前广泛应用在高速芯片上,作为物理层芯片和链路层芯片之间的接口。SPI4.2的接口定义如下:

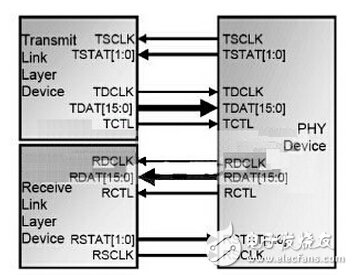

SPI4.2接口信号按照收、发方向分为两组,如图3中,以T开头的发送信号组和以R开头的接收信号组。每组又分为两类,以发送信号组为例,有数据类和状态类,其中数据类包含TDCLK、TDAT[15:0],TCTL,状态类包含TSCLK,TSTAT[1:0]。

SPI4.2借口信号

中,状态类信号是单端LVTTL信号,接收端利用TSCLK的上升沿对 TSTAT[1:0]采样,方向为从物理层芯片发往链路层芯片;数据类信号是差分LVDS信号,接收端利用TDCLK的上升沿与下降沿对 TDAT[15:0]和TCTL采样,即一个时钟周期进行两次采样,方向为从链路层芯片发往物理层芯片。

由于接收信号组与发送信号组的时序分析类似,因此本文仅对发送信号组进行时序分析。

在本设计中,采用Vitesee公司的VSC9128作为链路层芯片,VSC7323作为物理层芯片,以下参数分别从这两个芯片的Datasheet中提取出来。

● 状态类信号的时序分析

对状态类信号,信号的流向是从物理层芯片发送到链路层芯片。

第一步,确定信号工作频率,对状态类信号,本设计设定其工作频率和时钟周期为:

Freq=78.125MHz;

Tcycle = 1/ Freq = 12.8ns;

第二步,从发送端,即物理层芯片手册提取以下参数:

-1ns < Tco < 2.5ns;

第三步,从接收端,即链路层芯片手册提取建立时间和保持时间的要求:

Tsetup(min) = 2ns;

Thold(min) = 0.5ns;

将以上数据代入式1和式2:

2.5ns + (Tflight-data - Tflight-clk)MAX + 2ns < 12.8ns

-1ns + (Tflight-data - Tflight-clk)MIN >0.5ns 整理得到:

1.5ns < (Tflight-data - Tflight-clk) < 8.3ns

基于以上结论,同时考虑到Vsig = 6inch/ns,可以得到如下结论,当数据信号和时钟信号走线长度关系满足以下关系时,状态类信号的时序要求将得到满足:TSTAT信号走线长度比TSCLK长9英寸,但最多不能超过49.8英寸。

● 数据类信号的时序分析

对数据类信号,信号的流向是从链路层芯片发送到物理层芯片。

第一步,确定信号工作频率,对数据类信号,本设计设定其工作频率为:

Freq=414.72MHz;

与状态类信号不同的是,数据类信号是双边沿采样,即,一个时钟周期对应两次采样,因此采样周期为时钟周期的一半。采样周期计算方法为:

Tsample = 1/2*Tcycle = 1.2ns;

第二步,从发送端,即链路层芯片手册提取以下参数:

-0.28ns < Tco < 0.28ns;

第三步,从接收端,即物理层芯片资料可以提取如下需求:

Tsetup(min) = 0.17ns;

Thold(min) = 0.21ns;

将以上数据代入式1和式2,需特别注意的是,对数据类信号,由于是双边沿采样,应采用Tsample代替式1中的Tcycle:

0.28ns + (Tflight-data- Tflight-clk)MAX + 0.17ns < 1.2ns

-0.28ns + (Tflight-data- Tflight-clk)MIN>0.21ns

整理得到:

0.49ns < (Tflight-data - Tflight-clk) < 0.75ns

基于以上结论,同时考虑到Vsig = 6inch/ns,可以得到如下结论,当数据信号和时钟信号走线长度关系满足以下关系时,数据类信号的时序要求将得到满足:TDAT、TCTL信号走线长度比TDCLK长2.94英寸,但最多不能超过4.5英寸。

结论

高速电路中的时序设计,虽然看似复杂,然而只要明晰其分析方法,问题可以迎刃而解。

我要赚赏金

我要赚赏金