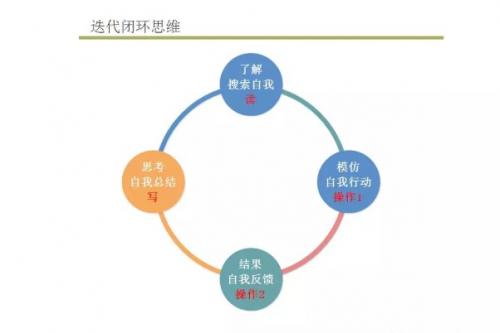

1. 迭代闭环思维

还记得小时候我们学习骑自行车的场景吗?一种是:亲自尝试模仿去骑,摔跤后总结下然后再尝试去骑,一遍又一遍的摔跤再尝试,然后越骑越好;另外一种是:在别人的指导下,按照别人的套路去练习,也越骑越好。

虽然这2种方式都学会了骑自行车,但差别还是很大的,前者是自我模仿思考的迭代闭环的学习方法,是小孩子常用的方法,比如小孩子学说话、走路等,这种方法的好处是学会了还能举一反三,不好的地方就是花掉的时间失败成本会更高;后者是套路式的学习方法,按照套路武功秘籍练好各式各招就会了,是年龄大的人常用的方法,这种方法的好处是学习的成本低,不好的地方是思考反馈会越来越少。

其实,现在我们仔细想下:小孩子为什么喜欢问为什么,因为小孩子是自我模仿思考的迭代闭环的学习方法;反而越大的人却越来越讨厌问为什么,因为大人更喜欢套路式学习方法,喜欢玩套路。

在这里,希望长大的我们,学习能多一些迭代闭环的思想方法,这样会因为我们迭代闭环的次数越多,学习就会越来越系统,也越学越快,越学越简单。就好比FPGA的设计一样,迭代次数越多,设计会越来越好。

FPGA设计的特点是需要不断不断的迭代各个设计流程来达到最终的设计,同时迭代的成本大,它比单片机开发更注重迭代的开发思想。所以,设计的前期一定要从系统的角度考虑好系统的方案,然后在系统这个方案中不断的迭代,不然后期发现由于系统方案的问题就得不偿失了,好的系统架构就是成功一大半了。其中,在FPGA设计中可以通过增量编译来加快我们的开发。

2. FPGA增量编译

FPGA增量编译可以理解为:当设计流程90%左右的设计是一样的话,就可以利用上次的结果来加速设计,当然如果设计中大部分不一样的话,利用增量编译就得不偿失。下面我们看看vivado中的增量编译:

使用增量编译时,可查看ug904文档,里面有详细介绍,主要利用Vivado的dcp类型的文件,dcp文件是Design Check Point文件,即一些中间节点文件,保存各个阶段的结果,为复用提供了方便。使用增量编译有2种方式:

在项目模式下:

1) 通过右键点击新实现方案运行 impl_2 ,并从弹出的菜单中选择设置增量编译;

2) 浏览增量编译检查点参考DCP文件并点击确认;

3) 继续运行实现方案,会明显发现编译时间缩短。

在非项目模式下:

在opt_design后运行以下命令:

%read_checkpoint -incremental reference_routed.dcp

上图的编译时间发现:增量编译后,可以大大减少编译时间,工程越大后的效果越明显。注意:

1) 当参考设计和当前设计的相似度大于95%的,最适合用增量编译技术,但相似度低于75%时,工具会建议关闭增量编译;

2) 有些时候,虽然是很小的RTL改动,也会造成网表的巨大差异,比如:改变HDL中的端口,增加总线的参数等,这个时候其实不适合用增量编译的。

我要赚赏金

我要赚赏金