ARMv8-A有两种执行模式,一种是AArch64执行模式,另一种是AArch32执行模式。执行状态定义处理单元(Processing Element, PE)的执行环境,包括以下内容:

a.

支持的寄存器宽度

b.

c.

支持的指令集

d.

e.

异常模型

f.

g.

虚拟存储系统(Virtual Memory System Architecture, VMSA)架构

h.

i.

程序员模型

j.

AArch64为64位执行状态。对应上述内容,此执行状态:

a.

提供31个64位通用寄存器,其中X30用作过程链接寄存器(ProcedureLink Register)。

b.

c.

提供64位程序计数器(PC)、堆栈指针(SP)和异常链接寄存器(ELRs)。

d.

e.

提供32个128位寄存器以支持SIMD矢量和标量浮点运算。

f.

g.

提供单一指令集A64。

h.

i.

定义ARMv8异常模型,该模型最多有四个异常级别EL0-EL3,它们提供执行权限层次结构。

j.

k.

支持64位虚拟寻址。

l.

m.

定义一系列与PSTATE相关的寄存器。A64指令集包括能直接操作各种PSTATE寄存器的指令。

n.

o.

使用后缀命名每个系统寄存器,该后缀指示可以访问寄存器的最低异常级别。

p.

AArch32为32位执行状态。对应上述内容,此执行状态:

a.

提供13个32位通用寄存器和一个32位PC、一个32位SP寄存器和一个32位链接寄存器(Link Register,LR)。链接寄存器用作异常链接寄存器和过程链接寄存器。其中一些寄存器有多个备份寄存器,用于不同的处理器工作模式。我们在上一期提到过,同一个功能的寄存器在不同的处理器运行模式下可能对应不同的物理寄存器,这些寄存器被称为备份寄存器。

b.

c.

为从Hyp(hypervisor)模式返回的异常提供一个异常链接寄存器。

d.

e.

提供32个64位寄存器,用于对高级SIMD矢量和标量浮点计算的支持。

f.

g.

提供两个指令集,A32和T32。

h.

i.

支持基于处理器工作模式的ARMv7-A异常模型,并将其映射到基于异常级别的ARMv8异常模型。

j.

k.

使用32位虚拟地址。

l.

m.

使用单个当前程序状态寄存器(CPSR)保存处理器状态。

n.

o.

在AArch64和AArch32执行状态之间进行转换称为内部处理(interprocessing)。

p.

04ARMv8-A架构的异常级别和安全状态

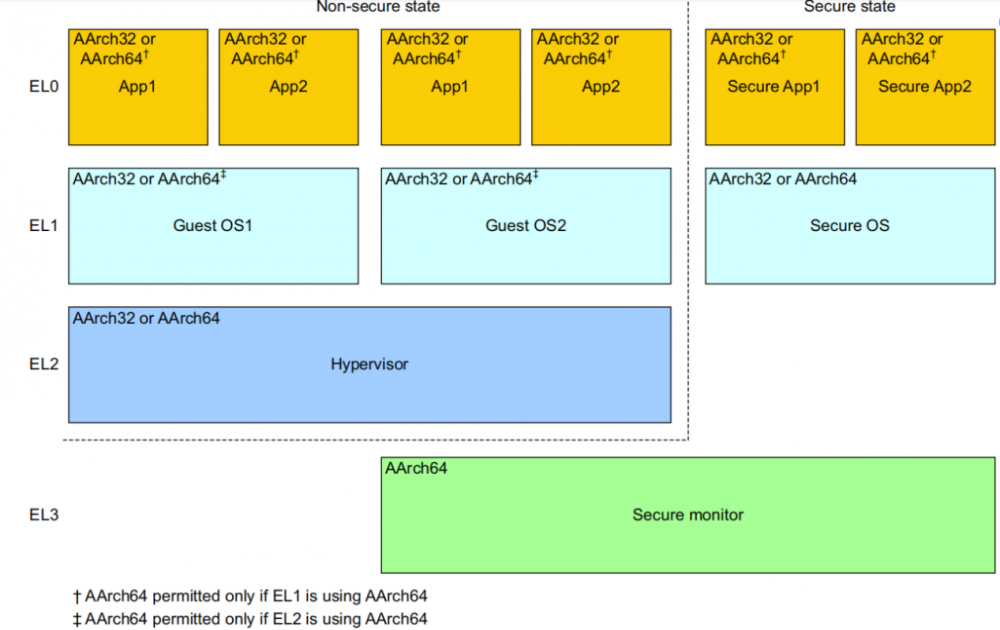

ARMv8-A有四个异常级别,从EL0到EL3。对于异常级别ELn,整数n增加表示软件执行的特权权限变大了。EL0级别下的执行叫非特权执行(unprivileged execution)。EL1主要用于运行操作系统内核。EL2可以支持非安全操作的虚拟化。EL3则支持安全状态和非安全状态之间的转换。安全状态与ARM TrustZone技术有关[2]。安全状态可以运行可信执行环境(TEE, Trusted Execution Environment)及安全应用,用于保障隐私数据和程序运行环境的安全性。

ARMv8-A架构并未直接指定哪些软件应该运行在哪些异常级别,但是在通常情况下,有如异常级别的使用模型:

1.应用程序运行在EL0;

2.操作系统内核和相关功能运行在EL1;

3.Hypervisor[3]运行在EL2;

4.安全世界状态和正常世界状态的切换在EL3完成。

下图反映了ARM-v8A架构中的执行状态、安全状态和异常级别之间关系[1]:

从图中我们可以看出,Hypervisor相关的支持特性主要是在EL2的非安全状态实现的。Hypervisor可以支持虚拟机之间的切换,而虚拟机主要被包含在EL1的非安全状态和EL0的非安全状态中。一些Guest OS可以运行在EL1状态里,每一个Guest OS可以运行在一个虚拟机上。而应用则运行在EL0的非安全状态中,同时也运行在Guest OS上。

我要赚赏金

我要赚赏金