在进行数字电路系统的设计时,时序是否能够满足要求直接影响着电路的功能和性能。本文首先讲解了时序分析中重要的概念,并将这些概念同数字系统的性能联系起来,最后结合FPGA的设计指出时序约束的内容和时序约束中的注意事项。

一、时序分析中的重要概念

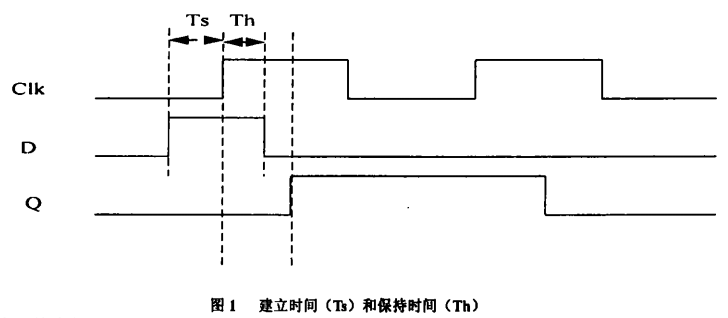

在数字系统中有两个非常重要的概念:建立时间和保持时间,其示意图如图1所示。一个数字系统能否正常工作跟这两个概念密切相关。只有建立时间和保持时间都同时得到满足时,数字系统才能可靠的、正常的工作。

当寄存器的建立时间或保持时间不能得到满足时,寄存器有可能会进入亚稳态( Metastable)。亚稳态是一种电压的中间态,假设寄存器的输出电压大于3V判决为逻辑1,小于0.3V判决为逻辑0,那么电压处于0.3V到3V之间并且能够短时间稳定的状态就是亚稳态。寄存器在进入亚稳态一段时间后会回复到正常的状态,但是有可能回到逻辑1的状态,也有可能回到逻辑0的状态。这种不确定性就有可能引起数字系统的错误。

建立时间和保持时间是一个寄存器的固有属性,是由其内部的结构、工艺等因素决定的,因而在进行数字系统设计时只能通过改变电路结构使其满足建立时间和保持时间的要求,而不能改变建立时间和保持时间的值。

二、建立时间和保持时间对电路性能的影响

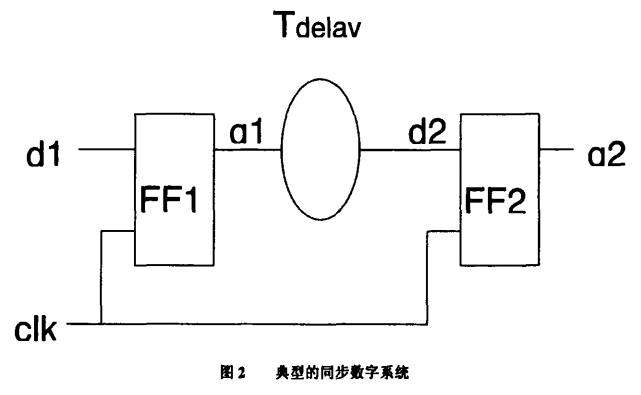

首先来看一个典型的同步数字系统的示意图,见图2。

在图2中,FF1和FF2代表两个寄存器,在两个寄存器中间存在组合逻辑。同步的数字系统正是由许多的寄存器,以及寄存器中间的组合逻辑构成的(也包括寄存器间的直接连接)。

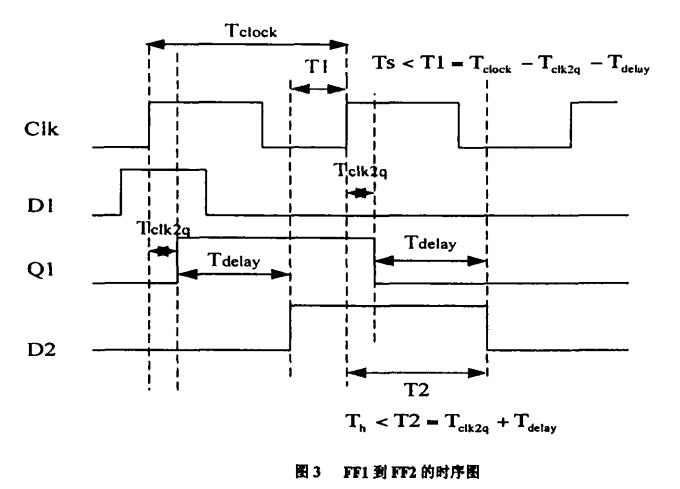

显然,如果要数字系统正常工作,每个寄存器的建立时间和保持时间都必须得到满足。假设时钟信号ck到达所有寄存器的时间相同,图3画出了这两个寄存器间的时序关系。

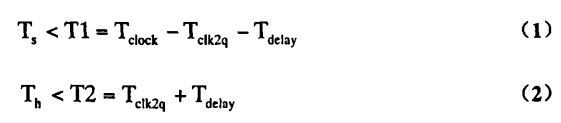

从图中可以看到,如果要FF2的建立时间和保持时间得到满足,必须要满足以下公式:

![]()

其中Ts建立时间,Th为保持时间,Tclock为时钟周期,Tclk2q为寄存器的传输延时(从时钟有效沿到输出的时间),Tdelay为两个寄存器之间的组合逻辑延时。

从公式(1)中可以看出,建立时间是否能得到满足取决于3个参数:时钟周期、寄存器传输延时以及组合逻辑延时。其中寄存器的输出延时是寄存器的固有属性,不可更改,因而在设计中只能靠调节时钟周期和组合逻辑的延时来满足寄存器对于建立时间的要求。

从公式(2)中可以看出,保持时间能否得到满足取决于2个参数:寄存器的传输延时和组合逻辑的延时,设计者能做的仅仅是调节组合逻辑的延时。

图3仅仅是两个寄存器之间的时序关系,在一个数字系统中往往包含有成千上万个寄存器,任意两个相邻的寄存器之间的时序关系都必须满足公式(1)和公式(2)的约束,只有如此数字系统才能正常工作。在数字系统可以正常工作的前提下,组合逻辑的延时就决定了数字系统能够工作的时钟频率的上限。组合逻辑的延时越短,系统的工作频率的上限就越高,这里的组合逻辑的延时指的是任意两个相邻的寄存器之间的最长的组合逻辑延时,也就是关键路径的延时。当然,组合逻辑的延时也不能无限短,必须要满足公式(2) 的要求。

三、在FPGA中对时序进行约束

在FPGA设计中,时序约束占有重要的地位。时序约束主要有两方面的作用:第一,EDA工具会根据设计者的约束努力尝试布局布线,尽量满足设计者提出的时序方面的要求;第二,在EDA工具经过努力仍不能满足设计者提出的时序要求时会给出警告信息,用以提示设计者。

在对设计进行约束时要做到恰到好处,太松或者太紧的约束都不能使电路达到最好的状态。约束过松自不必提,约束过紧之后EDA软件经过努力尝试仍不能达到要求,但其不会取最接近目标的一次,而是将最后一次作为结果,可能导致电路性能更加恶化。

当今的FPGA设计中时序约束主要包括3种:一是寄存器到寄存器的约束,二是引脚到寄存器的约束,三是寄存器到引脚的约束。

寄存器到寄存器的约束是对时钟周期的约束,对应于公式(1)中的Tclk2q+Tdelay+Ts,通常来讲设计者应该对其所设计的系统需要多快的时钟频率有所了解,只要结合需求给出时钟周期的约束即可。

在约束时钟周期时,实际上保证的是两个寄存器中后一级的寄存器。第一级寄存器连接在FPGA的外部引脚上,那么第一级寄存器能否满足其建立时间和保持时间的约束就取决于引脚上时钟和数据的关系以及各自到达寄存器的延时。假设引脚时钟和内部时钟是同步的(频率和相位都同步),那么数据引脚和时钟引脚的时序关系以及从引脚到寄存器输入端的延时共同决定了第一个寄存器的建立时间和保持时间能否得到满足,设计者可以对数据引脚到寄存器输入端的延时进行约束。

为了保证FPGA的输出信号和时钟的时序关系达到预期的效果,比如达到后一级芯片对时钟和数据时序关系的要求,设计者可以对寄存器的输出到引脚所经历的延时进行约束。

以上三种约束就可以涵盖设计中的所有寄存器。但是在某些特定的情况下,比如异步时钟域时,我们清楚地知道某些寄存器会发生建立时间或者保持时间不满足的情况,但这是不可避免的,设计者也已经对其进行了处理。在这种情况下,设计者最好告诉EDA软件忽略这些路径,否则EDA软件会努力尝试解决这些路径的时序冲突,既费时又没有效果。

我要赚赏金

我要赚赏金