FPGA中DSP资源是宝贵的且有限,我们在计算大位宽的指数、复数乘法、累加、累乘等运算时都会用到DSP资源,如果我们不了解底层的DSP特性,很多设计可能都无法进行。逻辑综合往往是不可控的,为了能够充分利用DSP资源,我们需要对DSP48E1有所了解。

1.DSP48E1介绍

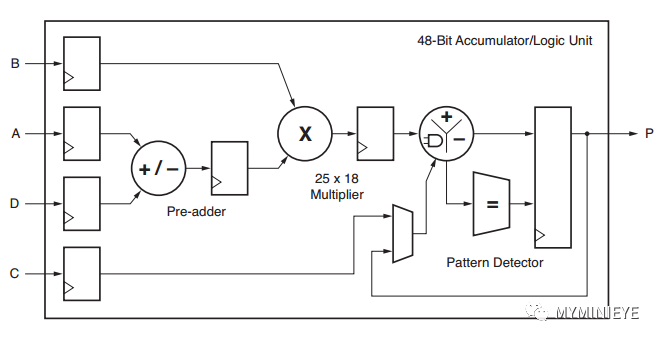

DSP48E1是7系列的最小计算单元,DSP资源,支持许多独立的功能,其基本功能如下所示

DSP48E1简易模型

包括:

• 带有D寄存器的25位预加法器

• 25*18二进制乘法

• 48位累加

• 三输入加法

其他的一些功能还包括桶形移位、宽总线多路复用、幅度比较器、按位逻辑功能和宽计数器等。

每个DSP48E1都有一个双输入乘法器,接着是3个数据通路的多路复用器和一个三输入的(加法器/减法器/累加器)

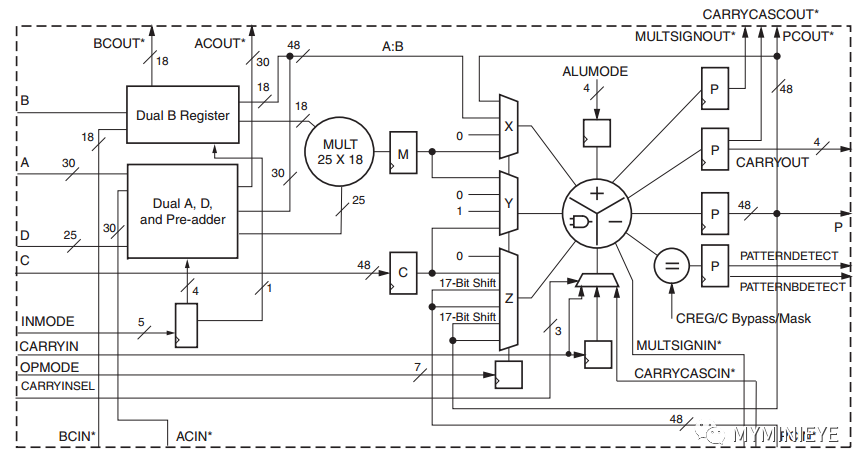

DSP48E1内部详细资源

一种典型的使用是A,B输入相乘后与C输入相加或减;当不使用第一级的乘法器的时候,两组48位输入可以实现按位操作的逻辑功能。

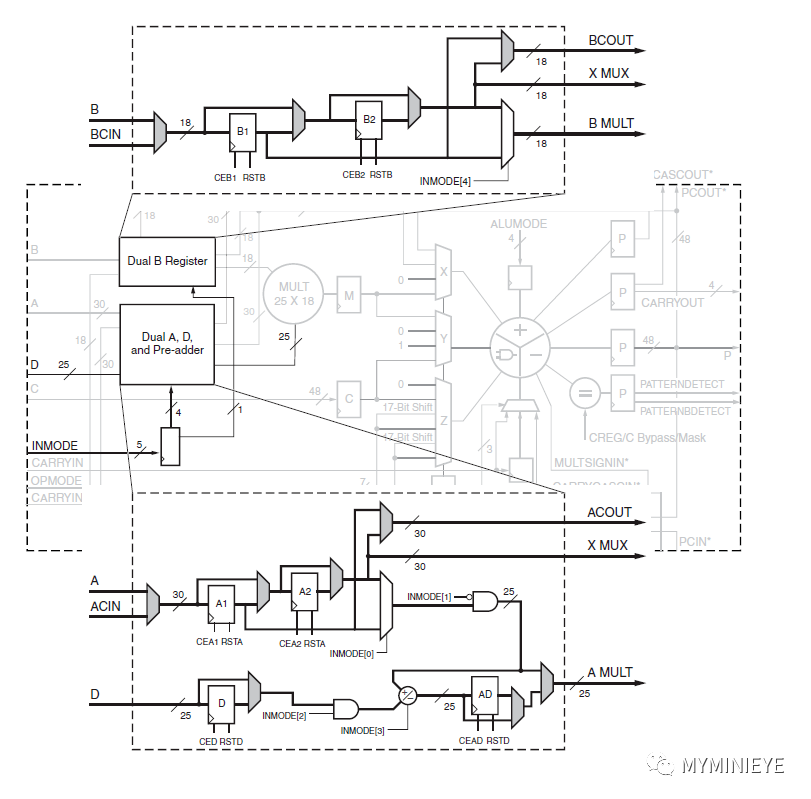

A和B的数据输入可以选择直接输入或者寄存一级、两级输入,如下所示

DSP48E1输入分层视图

其他的数据和控制输入可是选择寄存一级输入,这样的输入选择有助于构建多种类型,高流水化的DSP应用。

2. DSP48E1使用

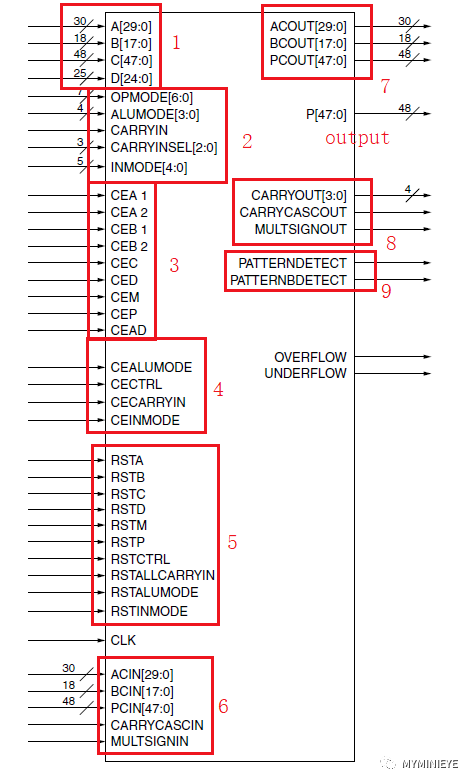

(1)DSP原语使用的每个端口及位宽如下所示:

①表示的数据通道,运算数据的输入。

②寄存器配置通道,我们可以通过配置这些寄存器,实现不同的功能,比 如加法、减法、乘累加,累减等。

③数据输入寄存器使能通道,在数据输入的时候可以选择寄存一级或者两 级(两级仅限A和B)。

④配置寄存器使能通道。

⑤复位信号,寄存器的复位端口。

⑥、⑦和⑧表示的是级联通道,其中CIN表示级联的输入,COUT表示级联 的输出。

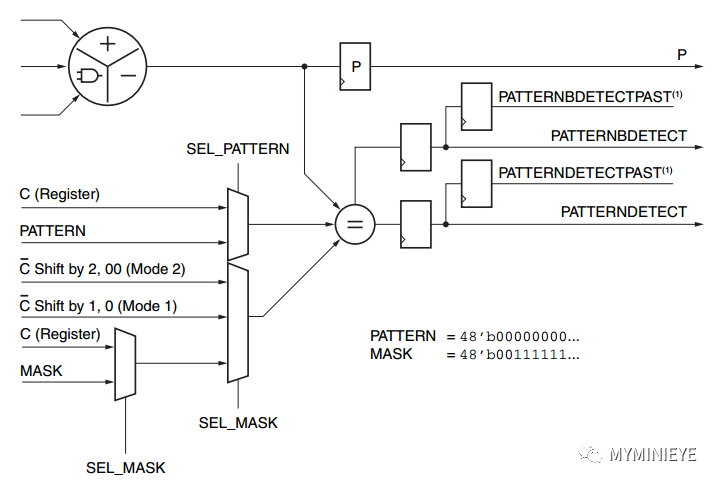

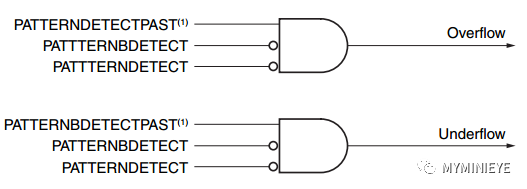

⑨模式检测输出,模式检测用于检测P总线是否与指定的模式或者模式的 补码完全匹配,如果加法器的输出与设置的模式匹配,则PATTERNDETECT (PD)将变高,如果与设置的补码匹配,则PATTERNBDETECT(PBD)将变高,其 使用逻辑如下

模式检测逻辑

OVERFLOW和UNDERFLOW是与模式检测一起使用时的溢出指示标志。

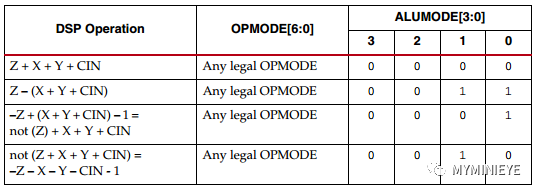

(2)DSP的使用主要通过三个寄存器来进行控制和改变相应的运算。

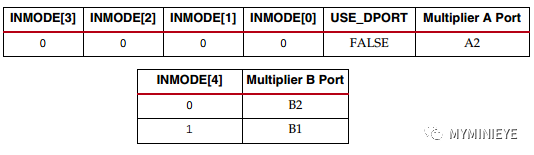

•INMODE 控制预加器,A,B,D寄存器的输入;(5bit)

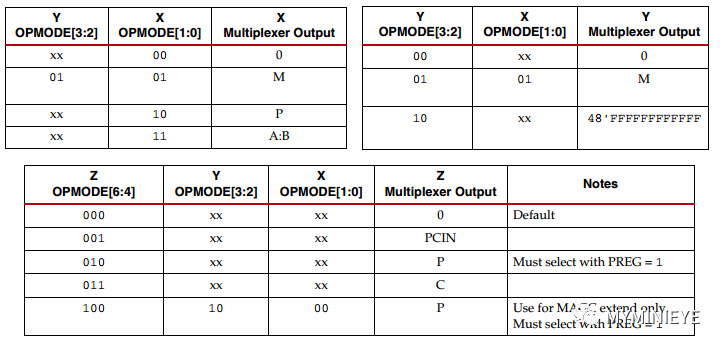

•OPMODE 控制X,Y,Z选择器的输入;(7bit)

•ALUMODE逻辑控制选择单元;(4bit)

我们通过构建一个乘累加器来介绍DSP的使用以及寄存器的配置。

实现的乘累加完成如下功能,即SUM = SUM + A * B ;SUM也就是DSP中的P输出。

明确了运算表达式,然后我们需要对三个寄存器进行设置:

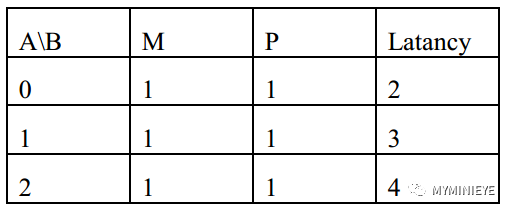

①乘法器的两个输入分别为A和B,我们选择A端口和B的数据相乘的时候,只使用A的[24:0]位参与运算,具体介绍可以见Xinlinx文档ug479(P30),这里我们把数据通过第二个寄存器输出到乘法器,INMODE设置为5’b00000。

图片居中使用:

②多路复用器需要指明参与ALU运算模块的数据,根据运算功能,我们选择乘法器的输出和P输出作为信号的输入,OPMODE设置为7’b010_0001。

③在最后的运算中我们选择加法运算。ALUMODE设置为4’b0000。即P=Z+X+Y+CIN其中Z=P,X=M,Y=0,CIN=0,M=A*B。所以P=P+A*B。

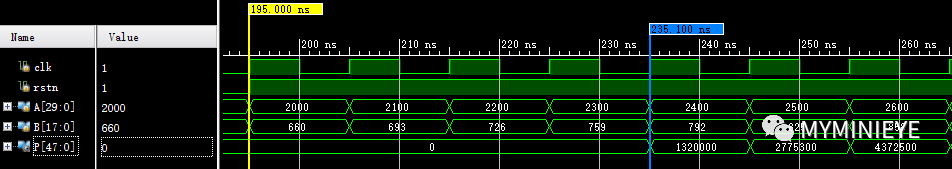

(3)相应的配置设置好之后,例化DSP48E1的原语,原语的调用可以见Xinlinx文档ug768(P120),然后建立Vivado工程,测试如下

通过仿真得到了正确的乘累加结果

需要注意的是:在计算乘法时,M寄存器必须是打开的,多路复用器Z的输入通过P寄存器,因此输出至少滞后2个时钟周期,这里通过A2和B2寄存器输入,故延迟了4个时钟周期输出结果。

3. DSP48E1注意事项

• 使用有符号数进行数据的处理。

• 尽量使用流水进行数字信号的处理。

•当数字的处理位宽较小时,尽量使用逻辑进行数据处理

•级联使用DSP的时候请尽量使用专用布线资源。

•合理的去复用DSP资源。

•在DSP不使用的时候,通过USE_MULT将乘法器关闭以降低功耗。

我要赚赏金

我要赚赏金