1引言

随着DSP技术的飞速发展,以其为核心的多轴运动控制卡越来越广泛的应用在运动控制系统中。上位机只需对被控对象实施总体的控制和管理,而位置反馈信号的采集、闭环控制的计算和控制量的输出均由运动控制卡完成,这极大地提高了运算速度和控制响应速度。本文设计的运动控制卡以TI公司的32位定点DSPTMS320F2812为核心处理器,辅以运动控制器LM628,通过PCI总线专用接口芯片PCI9052与上位机通信,实现3轴(可扩成多轴)伺服电机的控制,完成位置、速度控制以及直线、圆弧插补功能。本文将对运动控制卡的硬件设计进行详细的介绍。

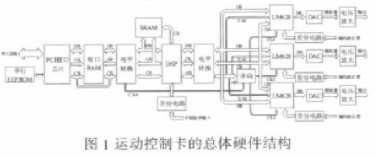

2运动控制卡的硬件结构

LM628是NSC公司专为使用增量式编码器作为位置反馈的伺服机构而设计的一种芯片,其集成度高,需要外围部件少,易于调试。主要特点如下:具有32位位置、速度和加速度寄存器;带有16位参数的可编程数字PID控制器;可编程微分采样间隔;运动过程中可改变速度、预期位置和PID控制器参数;实时可编程的主机中断。

PCI9052是PLX公司推出的低成本、低功耗、32位PCI总线专用目标接口芯片。其兼容PCIV2.1协议特性,可与多种局部总线相连;支持复用或非复用的8/16/32位局部总线;支持4个局部片选信号和5个局部地址空间;支持两个来自局部总线的中断,可生成一个PCI中断;支持局部总线等待状态,附加的LRDYi#握手信号可用于产生各种等待状态。运动控制卡的总体硬件结构如图1所示。其中,DB为数据总线,AB为地址总线,CB为控制总线,CS-1”CS-4为片选信号,XA0为DSP经电平转换后的最低位地址线。

从图中可以看出PCI接口芯片的PCI总线端直接与金手指相连,局部总线端则通过双端口RAM与DSP相连,构成16位存储转换电路。DSP分别与三片LM628相连,与其配合以实现3轴运动控制。这样既解决了DSP因系统资源不足不能控制多轴的问题,又弥补了LM628单独控制时总线传输延时的缺点。LM628的数字量输出经数/模转换和电压放大后转换为交流伺服驱动器可以接收的模拟电压信号(-10V“+10V)。而伺服电机增量式光电编码器的反馈经差分电路滤波并合成单端信号接入到LM628中,以构成位置闭环控制。

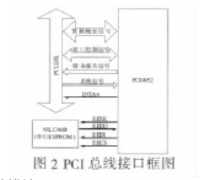

2.1PCI总线接口

PCI总线是一种高性能、32位地址/数据复用总线,数据传输速率高达132MB/s。目前实现PCI接口的有效方案有使用可编程逻辑器件和使用专用接口芯片两种。前者实现PCI接口比较灵活,但是设计难度很高。后者虽没有前者那么灵活,但其优越性非常明显:能够有效降低接口设计的难度,缩短开发时间,同时其还具有较低的成本和通用性,并能够优化数据传输,提供配置空间等。这里采用PCI9052实现PCI总线接口,并选用EEPROM93LC46B对其进行配置,电路框图如图2所示。中断信号这里只用到一条中断线INTA#。

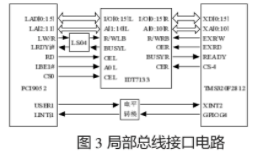

2.2局部总线接口

为了满足DSP与上位机之间大量数据的高速交换,这里采用主从式共享双口RAM的通信方案,接口电路如图3所示。由于IDT7133是2K×16位的SRAM,因此将PCI9052的局部总线设置为16位宽的数据总线,即将LBE1#单独接到IDT7133的A0L端。BUSYL经非门接到PCI9052的LRDYi#端,这是因为当BUSYL为高时才允许外部设备访问,而局部总线准备好信号LRDYi#为低电平有效。BUSYR经电平转换后直接接到TMS320F2812的READY端。当BUSYL或BUSYR任何一个引脚被置低,其所属设备就等待一个访问周期,直到BUSY被拉高,即双口RAM不再忙,这样便保证了数据传输的准确性和可靠性。因此,采用双口RAM通信不但简化了接口电路的设计,而且提高了上下位机数据交换的速度。

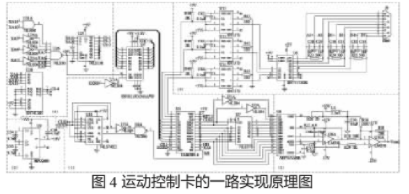

2.3LM628伺服控制单元

控制卡共有3路输出,其中一路如图4中虚线框(1)所示,其余两路与此类似。XD0”XD7为DSP的低八位数据线,LM628所需的32位数据由其经总线驱动芯片SN74LVC4245分四个写周期写入。DSP经CS-1选通LM628后,再结合XA0就可实现对其读写。为了提高控制精度,这里采用12位输出模式,即在每一个采样周期,LM628的18“23脚输出两个周期,前一个输出低6位数据,后一个输出高6位数据。为了让12位数据能同时输入到后续的DAC芯片中,这里采用了一片6位数据锁存器74LS378。当LM628输出低6位时,DA0是输入触发器的时钟信号,DA1是触发器的允许信号,此时,锁存器的G端为高,数据锁存,接着LM628输出高6位数据,此时DA0是给DAC芯片的写信号,DA1是片选信号,锁存器的G端为低,数据不锁存。这样便从8位输出合成了12位的DAC输入信号DAC0”DAC11。

2.4数/模转换和放大电路

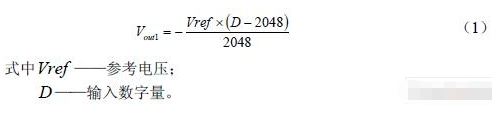

如图4中虚线框(2)所示,DAC参考电压Vref由Maxim公司的MAX680提供,而LM358的±12V电源则可直接从PCI插槽获得。LM628输出的12位数字量经AD7545A转换为相应的模拟量,再由LM358两级运算放大成-10V“+10V电压信号送往交流伺服驱动器,从而驱动电机运转。电阻R26和R27用来调整满刻度输出电压和抑制零点漂移,电容C38则用来加快DAC变换速度和对其输出进行频率补偿。最终输出电压Vout1可由式(1)计算得出:

2.5差分电路

在噪声比较大的环境中,为了解决干扰和远距离传输等问题,通常采用差动信号传输,如图4中虚线框(3)所示。为了进一步消除干扰,在每个输入端都接入一个滤波电容,同时在每一对差动信号输入线之间接一个用于线路阻抗匹配的电阻。差动信号(IN+、IN-、A+、A-、B+、B-)经差动线路接收器SN75175和高速光电耦合器6N137转换为单端信号(IN、A、B)输入到LM628中,以实现闭环控制。

2.6译码电路

如图4中虚线框(4)所示,采用一片3/8译码器74LS138对地址译码,实现对控制卡3路伺服单元的片选,而XA0则专门用于对LM628进行读写控制,这样得出的地址信号是连续的(0XF60”0XF65)。另外,采用一片四位二进制码比较器74LS85实现DSP对双口RAM的读写片选。片选地址信号范围为0“7FF,这刚好寻址双口RAM2K范围内的所有空间。

此外,由于TMS320F2812要从双口RAM读出大量的运动轨迹数据并存储,而其片内只有18KB的空间,远不能满足要求,同时为了方便程序调试和修改,均需要DSP扩展一片存储器。这里选用CYPRESS公司的256K×16位的SRAMCY7C1041CV33,其读写周期时钟最快可达12ns,因此可与DSP进行零等待状态接口,保证了DSP的运算速度。

3运动控制卡的配置

配置空间是PCI总线所特有的一个空间,其通常与接口芯片相关,包括一系列的PCI配置寄存器。PCI9052的配置寄存器分为PCI配置寄存器和局部配置寄存器,两者都可以由PCI总线和串行EEPROM访问。

3.1PCI配置寄存器及其配置

在PCI配置寄存器中的设备ID、制造商ID、版本号、首区类代码、类别代码、指令寄存器和状态寄存器等在所有的PCI设备中都必须实现。操作系统通常使用其内容来决定为该PCI设备加载驱动程序。此外,PCI配置寄存器还提供6个基地址寄存器,其中BASE0和BASE1是分别映射到内存和I/O的基地址,可固定用于对PCI9052的寄存器操作。而BASE2”BASE5最多可访问局部端所接的4个设备,实现其局部地址空间的访问。PCI总线对局部端设备的局部地址映射是通过1个寄存器组(包括PCI基地址寄存器、局部范围寄存器、局部基地址寄存器和局部总线区域描述符)来实现的。它定义了每个空间及其特性,并将局部端设备通过局部端地址翻译为PCI总线地址,即将本地设备映射到系统的内存或I/O端口。而片选信号寄存器则用来选定这些设备。这样,用程序操作这一段内存(或I/O)实际上就是对本地设备的操作。这些寄存器的内容必须在设备复位时通过串行EEPROM加载。

3.2局部配置寄存器及其配置

在这里,选取LAS0(LocalAddressSpace0)访问局部端双口RAM,与其相关的寄存器为LAS0范围寄存器、LAS0局部基地址寄存器、LAS0局部总线区域描述符和片选0基地址寄存器。LAS0范围寄存器用于定义板卡上资源所占地址空间的大小。由于板卡需要2KB的内存空间,而计算机预留了32KB空间(即8000H),因此写入寄存器的值为0xFFFF8000H;LAS0局部基地址寄存器用来定义板卡资源所占的基地址,它将其重新映射到PCI地址空间中,以使PC机能对板卡进行访问。由于基地址必须是地址空间范围的整数倍,又因局部地址空间位0为使能位,因此,写入寄存器的值为00008001H;LAS0局部总线区域描述符用来定义地址空间0的具体工作特性。由于板卡数据总线采用16位,工作方式定义为不使能突发和不可预取,因此写入寄存器的值为4043A1C0H;片选0基地址寄存器用来确定片选信号有效的地址范围,其既确定了片选信号的基地址又确定了片选信号的地址范围。

这里控制卡采用PCI9052的CS0#作为双口RAM的片选信号,则其起始地址和地址范围都可由片选0基地址寄存器设置。由于双口RAM容量为2KB,因此设置CS0#基地址寄存器的第11位为1,又局部总线端空间0的基地址是0x00008000H,为方便寻址,将CS0#的基地址和局部总线端空间0的基地址设为同一值。由于基地址(8000H)是CS0#地址范围的16倍,所以将CS0#基地址寄存器的第16位设为1,再将位0设为1使能,这样写入片选0基地址寄存器的值为0x00008401H。当PC机寻址时,地址映射到局部总线端的空间0,从其基地址开始的2K空间落在CS0#基地址寄存器所设置的范围内,CS0#端则有效,可对双口RAM各单元进行读写,这样就不必根据地址译码得到片选逻辑,简化了硬件设计。此外,PCI9052提供两种中断源,即硬件和软件中断。这里板卡使用其提供的2个局部中断中的一个,即LINTI1引脚,通过设置中断控制/状态寄存器(INTCSR)实现,并生成PCI中断INTA#方式。

4驱动程序的开发

为了从PCI总线配置寄存器中获得上位机动态分配的映射基地址,并对映射端口进行读写,必须编写驱动程序。编写时可以使用DDK,但是难度较大,需要做很多通用的基础性工作。为简化驱动程序开发,可以采用NuMega公司开发的DriverStudio中的DriverWorks工具包进行WDM驱动程序设计。由于其被嵌入到VC中,因此可更方便的用于开发和调试驱动程序。实践表明,DriverStudio并没有通过牺牲系统性能来换取驱动程序的快速开发。

我要赚赏金

我要赚赏金