大家好,我是一哥,上章一个典型的uvm验证平台应该是什么样子的?从本章开始就正式进入uvm知识的学习。先一步一步搭建一个简单的可运行的测试平台。

本章首先来介绍一下构成uvm测试平台的主要组件。

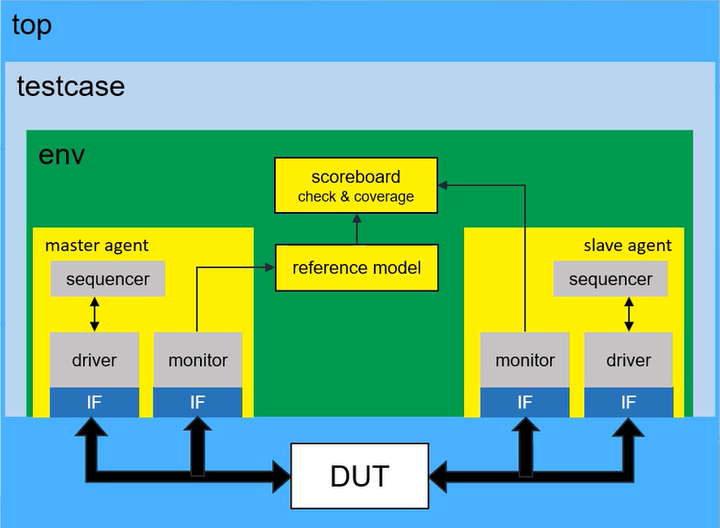

图示是一个典型的uvm测试平台的结构图,构成测试平台的每一个元素称为组件,既component。

下面从底层到高层,就每一个组件来说明它们在测试平台中所起到了作用。

第一个组件是driver。它的作用是将接受到的事物转化为pin级信号。然后通过接口驱动到被测设计的端口上,也就是所说的激励驱动。那么专门发送的事物是从哪里获得的呢?答案是sequencer。sequencer的作用是启动事物发生器sequence。sequence在被启动之后便会产生事物。sequencer将sequence产生的事物转发给driver。

monitor它的作用是监视接口上的信号,包括备测设计的输入信号以及输出信号。并将获取的pin级信号转化为事物级对象。然后发送给其他组件进行处理。

下一个组件是master agent。它的作用是将driver,sequencer以及monitor封装起来,因为driver要从sequencer获取事物,所以说需要在agent中将它们连接起来。

reference model参考模型,它将模拟dut的功能行为,根据输入的激励产生相应的结果,该结果称为参考值或是期望值。

master agent中的monitor会将dut的输入收集下来。然后发送给参考模型,作为参考模型的输入。

slave agent它用于收集dut的输出信息,并将pin级信号转化事物级对象,然后发送给其他组件进行分析,一般情况下,因为slave agent不需要驱动dut。所以说它只包含monitor,而去除了driver以及sequencer。我们称这种只有monitor的agent为agent的passive模式。

scoreboard积分板,它将会从两个地方获取数据,一个是参考模型发来的期望值,另一个是从slave agent发来的dut的输出值。在积分板中对这两个值进行比较,由此来判断dut的功能是否正确,同时可以将功能覆盖率嵌入到scoreboard当中,以实现覆盖率的收集。将多个agent,reference model,scoreboard以及其他组件封装到一起就构成了env。因为这些组件之间存在着数据通信。所以说,在env当中,要通过某种方式将它们连接起来。需要注意的是,一旦env完成,在后续的测试案例当中,就不能够在对他进行更改。如果出现必须更改的情况,那么之前已经通过了测试案例需要重新执行。

testcase测试案例,它包含了env,在一个测试项目当中,测试案例会有很多,但env只有一个并且一旦确定,就不能随意更改。对整个平台的配置都是在测试案例中完成的。因此在构建env的时候,需要事先定义好配置接口,是env具有可配置性。

uvm不仅为验证工程师提供了测试平台的结构,而且在uvm的资源库当中。对于平台中的每一个组件啊都有一个对应的基类。验证工程师在搭建验证平台的时候,每一个组件需要从相应的基类进行扩展。

来看一下uvm提供了哪些基类,以及这些基类和平台中的各个组件之间的关系。

uvm component,所有的组件的基类都扩展于uvm component。下面的类都是以它为基类扩展而来的。

uvm test,对应着testcase测试案例,验证工程师的测试案例都是从这个基类扩展而来。

uvm env对应着env,平台的env需要从这个基类扩展。以此类推,scoreboard应该从uvm scoreboard扩展。agent需要从uvm agent扩展。sequencer需要从uvm sequencer扩展,monitor需要从uvm monitor扩展。还有driver需要从uvm driver扩展。

这里需要注意的是uvm库中并没有参考模型references、model建立相应的uvm reference model这样的基类。但是,uvm reference model需要从以uvm component这个基类进行扩展。因为各个组件之间存在着信息通讯。

比如driver需要从sequencer获取事物。monitor则需要将监控到的信息发送给reference model或者是scoreboard。所以,uvm需要建立某种机制将需要通信的组件连接起来。

那么,在uvm当中,使用通讯端口来建立组件之间的连接,外面的端口有很多种,可以根据不同的场合和不同的需求来选用。这些端口使用起来简单安全,可以便捷地将各个组件连接起来。如果将验证平台的组件比作工厂中流水线的设备,那么事物就是穿梭于这些设备之间的产品了,事物是组件的操作对象,uvm也对事物建模提供了基类进行扩展,对事物级的建模需要从uvm sequence item扩展。而产生事物对象的事物发生器sequence需要从uvm sequence扩展。

凡事都一个有简到繁荣的过程,那么,由于刚刚接触到uvm平台,那么对其结构呢还有很多疑问。所以说,为了降低上手的难度,这里对平台进行简化,从搭建最简单的平台开始,以后再逐步对平台进行完善。

简化一,去掉slave agent,简化二,去掉scoreboard。简化三,去掉reference model。简化四,去掉dut,最后平台只剩下一个简单的master agent。它仅仅可以实现的功能是产生事物并且将事物发送到driver上面。

下一节课我们就从零开始搭建一个可以运行的uvm测试平台。

我要赚赏金

我要赚赏金