电源设计者如今面临两个主要问题:消除有害的输入谐波电流和确保功率因数尽可能地接近于1。有害的谐波电流会导致传输设备过热,并带来后续必须解决的干扰难题;这两者也会对电路的尺寸和/或效率产生不利影响。如果施加在线路上的负载不是纯电阻性的,输入电压和电流波形之间将产生相移,从而增加视在功率并降低传输效率。如果非线性负载使输入电流波形失真,则会引起电流谐波,从而进一步降低传输效率并将干扰引入市电电网。

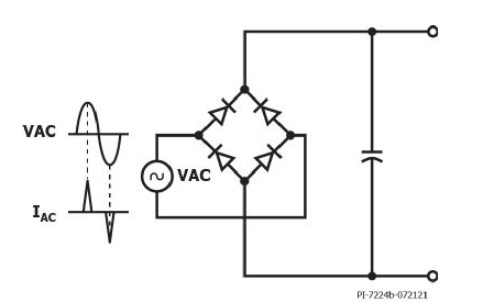

如果我们回到原来的整流级看波形,输入交流电压是一个传统的正负极交替的对称正弦波。然而,输入电流表现为一系列尖峰,随着输入电压的升高而增大。这是因为二极管导通(因此电流流动)只会在大电容充电时发生,此时VAC输入电压超过存储在电容上的DC电压。当VAC低于存储的电容电压时,存储在大电容上的电荷将支持电源的输出。在此期间,能量从电容转移到负载,这会导致电容电压下降。一旦AC电压再次超过储能电容上的(现在较低的)电压,电容就会重新充电。这种短的充电窗口意味着输入电流以三角形脉冲而不是正弦波的形式提供。

图1:整流级的输入电流表现为一系列包含大量谐波成分的尖峰信号,

这会污染AC线路

这种尖峰电流波形由一系列工频谐波组成。谐波含量受到为保护配电网络而制定的各种国家和国际法规的限制。图1所示电路的功率因数往往非常低,约为0.5,与理想的1相去甚远。

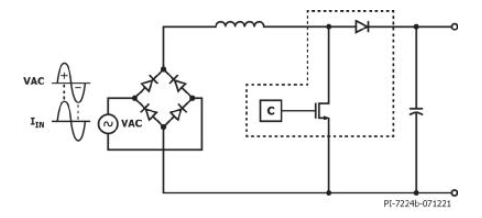

这个问题可以通过几种不同的方式来解决。最简单的方法是添加一个电感来抵消电路的电容分量 - 这种技术称为无源功率因数校正。然而,无源功率校正的作用有限。在具有高功率输出的应用中,所需电感的物理尺寸使其不切实际。在这种情况下,通常使用有源PFC电路来使电路的功率因数更接近于1,而不会对电路的尺寸产生负面影响。有源功率因数校正由PFC二极管、电感和MOSFET组成。MOSFET用作高频开关,由执行功率因数校正算法的控制器驱动。

开关电路强制输入电流跟随整流后的VAC输入,并再次变为适当的正弦波。理想情况下,正弦波具有低失真,以消除可污染AC线路的谐波电流。由于电压和电流波形同相,功率因数也上升到接近理想值1。

图2:具有有源功率因数校正功能的整流级将输入电流变为正弦波

实现有源PFC电路的一个简单方法是使用Power IntegraTIons的HiperPFS-4解决方案(见图3)。HiperPFS-4器件包括一个超低反向恢复电荷二极管,通过最大限度地减少二极管的转换损耗来实现高效率。它还具有可降低导通损耗的低RDS(ON)MOSFET和集成了许多安全功能的高级连续导通模式控制器。

图3:Power IntegraTIons的HiperPFS-4

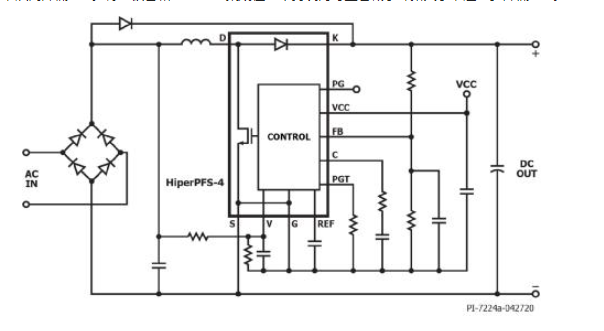

HiperPFS-4器件同时集成了功率因数校正二极管、MOSFET和控制器,这种高集成度有助于缩短开发时间并加快上市速度。将关键元件集成在一个封装内的另一个优势是最大限度地减少连线中的寄生电感。电路电感的降低有助于降低PFC二极管两端的电压应力和MOSFET的峰值漏源极电压,从而提高电路的可靠性。此外,所使用的二极管具有软恢复特性,可减少振铃,从而降低EMI。将二极管和MOSFET集成在一个封装内可显著减小环路大小,进一步降低EMI。

图4:HiperPFS-4器件在同一个封装内集成了用于有源功率因数校正的关键元件,

以最大限度地减少连线中的寄生电感,从而降低功率开关上的di/dt感应电压应力

总结

有源功率因数校正是减少有害的输入谐波电流和提高功率因数的最佳方法。Power IntegraTIons开发了HiperPFS-4解决方案,将有源功率因数校正所需的关键元件集成到同一个封装内。这种方案可大幅减少输入电流谐波并提高功率因数,同时解决了在传统电路设计常见的许多布局问题,例如降低电压应力、EMI和寄生损耗。

我要赚赏金

我要赚赏金