Frank Xiao

TPS53355作为D-CAP 模式的代表芯片,具有优异的负载动态响应性能,以及非常简单的外部电路设计要求,被广泛应用于交换机,路由器以及服务器等产品中。D-CAP模式不同于定频电压和电流控制模式,内部没有电压误差放大器,只有一个比较器,这样做一方面可以实现变换器的快速动态响应,另一方面对输出电容纹波就会有一定的要求,以满足芯片内部比较器的识别门限。随着电路尺寸和使用寿命的优化,无电解电容已经成为未来的趋势,瓷片电容的ESR参数相对小很多,很难满足芯片最小纹波的要求,另输出端负载对输出电压纹波的要求也越来越高,因此D-CAP控制模式芯片就需要设计RCC纹波注入电路以保证整个电路的稳定,那如何设计RCC纹波电路呢,又有哪些注意点呢?本文会做具体介绍。

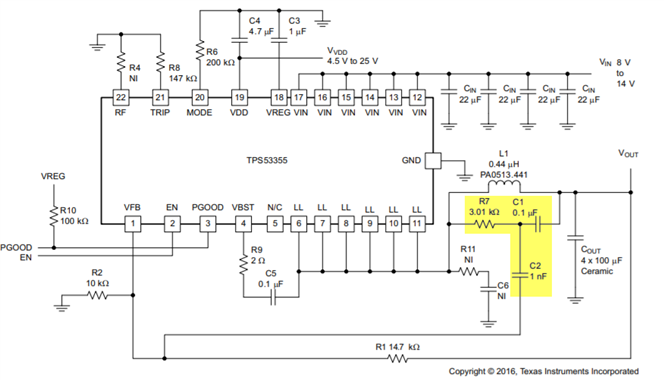

图1 TPS53355的RCC纹波注入电路

第一步:

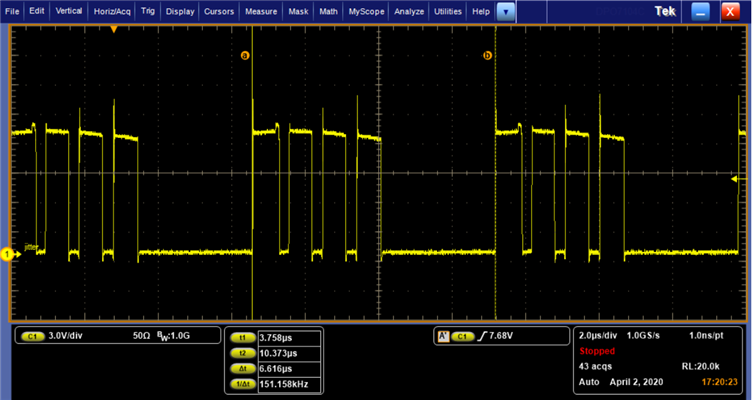

设计要满足电路的稳定性条件判据公式(1)(其中Rr和Cr分别对应图1中R7和C1),这里需要考虑输出电压较高时输出电容容值的衰减情况,比如5V输出且选用6.3V耐压的输出电容时,电容容值很可能会衰减为标称容值的20%左右。从而导致电路的不稳定(如图2),因此通过稳定性判据公式可以得到芯片的最小纹波注入大小(需要将此纹波注入大小与芯片内部比较器纹波需求、一般15mv进行比较,选取二者中的更大值,不过一般这个值会比芯片内部比较器纹波需求大)稳定性判据公式(1)的具体推导过程本文不再赘述,有兴趣可以评论区留言提问。

图2 不稳定时的开关波形

第二步:

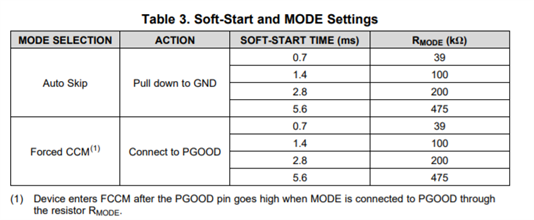

设计中要判断是否需要使用PG(power good)信号,以及是否需要使用FCCM模式,如果有以上的需求,设计时要保证芯片不触发power good门限。因为一旦叠加纹波注入后的FB 触发PG门限就会导致PG拉低,另使得芯片无法退出auto skip模式(如图3)

图3 芯片MODE 选择设置

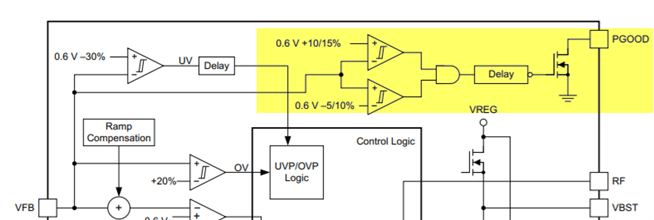

从图4中我们可以判断PG信号正常时,最高FB点不能超过0.6V* (1+15%),鉴于15%有正负5%的变化,所以FB最大不能超过660mv,纹波注入不能超过60mv。

图4 芯片内部PG触发逻辑

我要赚赏金

我要赚赏金