74LS161是一个同步四位二进制计数器

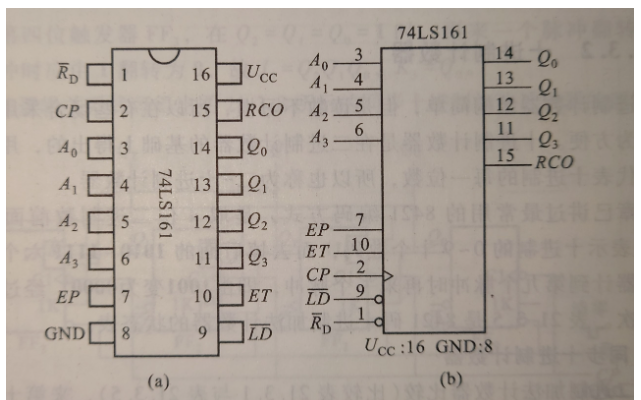

引脚介绍

1脚:RD'为清零端,低电平有效。

2脚:CP为时钟脉冲输入端,上升沿有效。

3~6脚:A0~A3为输入(预置)端,可预置任意一个4位二进制数。

7,10脚:EP,ET为为计数控制端,两脚同时为高电平时芯片计数;任意一脚为低电平时计数器保持原数据。

9脚:LD'为并行(寄存器)启用控制端,低电平有效。

11~14脚:Q0~Q3为数据输出端。

15脚:RCO为进位输出端(满16进一),高电平有效。

通过从功能表分析

第一行:当RD'(低电平有效)为0时,此时无论其他引脚是什么,都是复位置零功能。也说明RD'不需要等CP的时钟信号,即异步清零。

第二行:当RD'为1,LD'为0时,在CP时钟信号为上升沿时刻,输出等于输入,即同步置数,相当于寄存器作用。

第三、四、五行:当RD'和LD'都为1(无效)、EP和ET中任意一个为0时,此时输出端保持原数据不变。

第五行:当RD'、LD'、EP和ET都为1时,为计数功能。当CP时钟信号上升沿来临时计数加一。

基本应用及注意事项

一、16位进制计数器

二、任意进制计数器(重点)

任意进制的实现有两种方法:

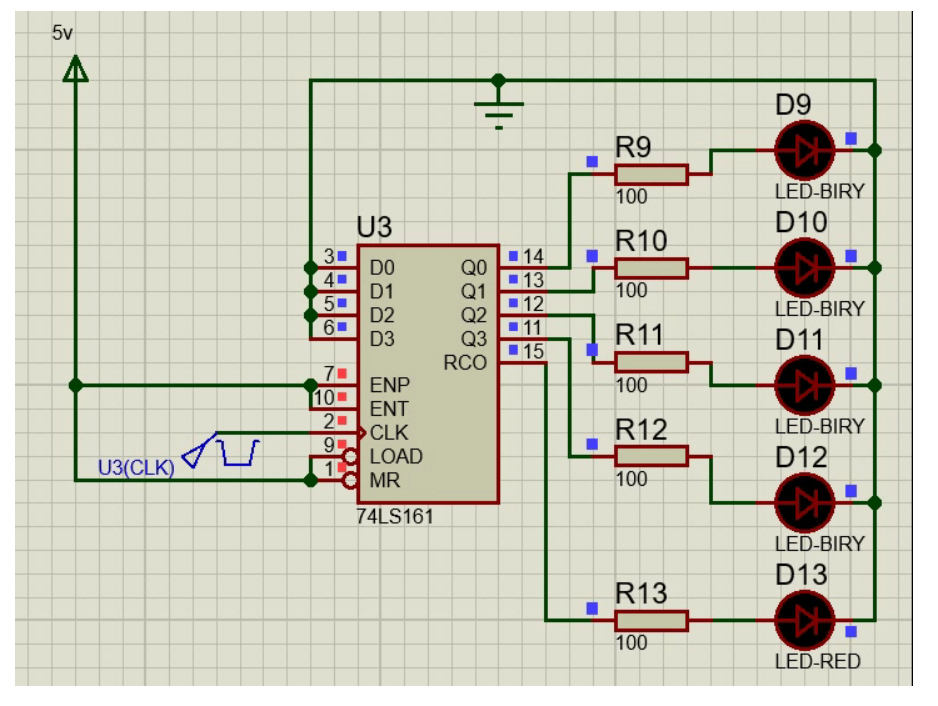

1、反馈清零,即将数据输出端Q接上与非门后接回清零端RD'(仿真图中为MR)。

例如实现12进制(0000~1011共12个状态)就将12+1(0000~1100共13个状态)的1(即Q3Q2端)与非后接回清零端RD'(低电平有效)。

那么,为什么要在需要的进制加1后再接回清零端RD'呢?前面我们说过74LS161有异步清零的性质,即当RD'为0时,RD'不需要等CP的时钟信号即可实现清零功能。

若使用1011做12进制,当Q3Q2Q0为1时经过与非后立即使RD'为0(有效),此时立即触发清零功能,1011这一状态不会被保存,当然也不会被算在计数里。所以要使用1011+1即1100。

反馈清零法实现12进制

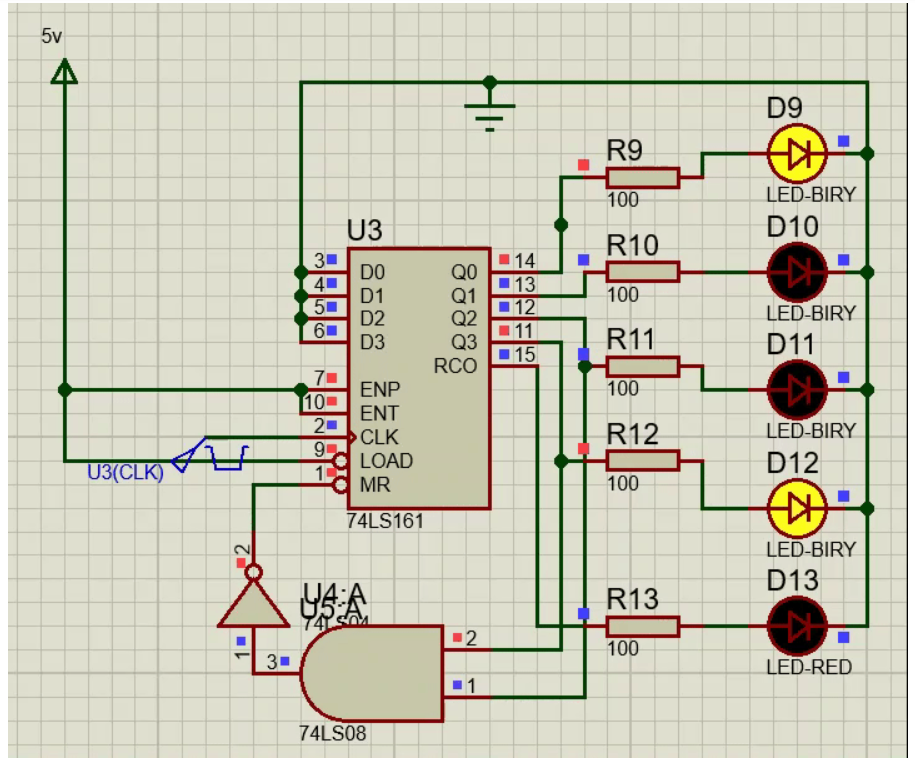

2、反馈置数,即将数据输出端Q接上与非门后接回并行启用控制端LD'(仿真图中为LOAD)。

因为使用了并行启用控制端LD',所以我们也要用上数据输入端A0~A3(仿真图中为D0~D3),如果输入端什么都不接,就无法判断是多少进制。

例如12进制:

若A端给0000(0000~1011共12个状态),当Q端为1011时(Q3Q2Q0为1)经过与非后使LD'为0,此时还需再等一个CP时钟信号将A端的0000送到Q端,即同步置数(0000~1011共12个状态)。该接法下1011这一状态是稳定的。

若A端给0001,则Q端最终为1100。(0001~1100共12个状态);

若A端给0100,则Q端最终为1111。(0100~1111共12个状态);PS:我们知道当Q端为1111时会产生进位,此时RCO端会为1。所以我们可以直接将RCO端接非门后接回并行启用控制端LD'。

反馈置数法 A端给0100实现12进制

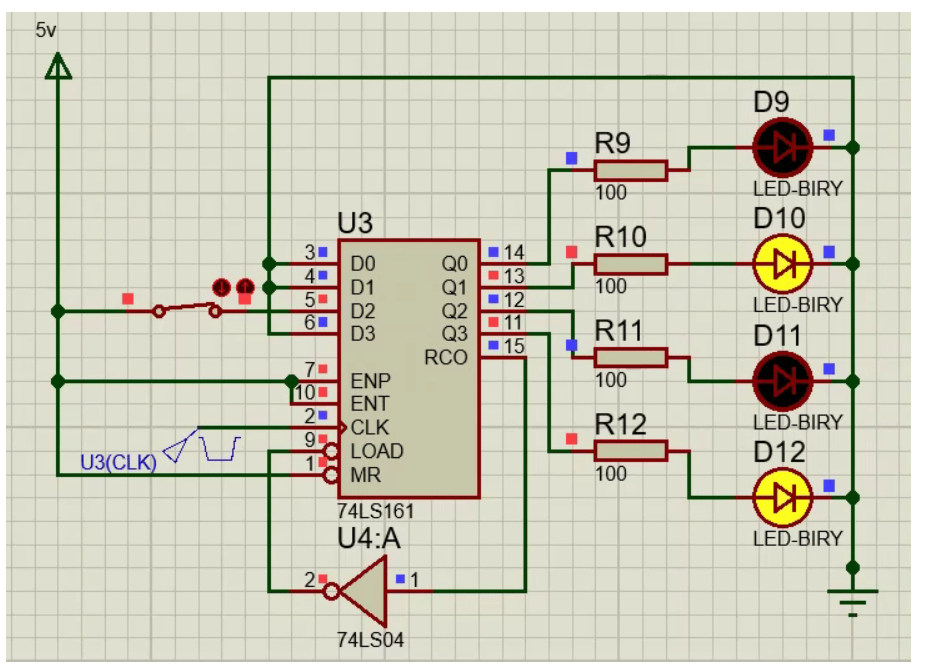

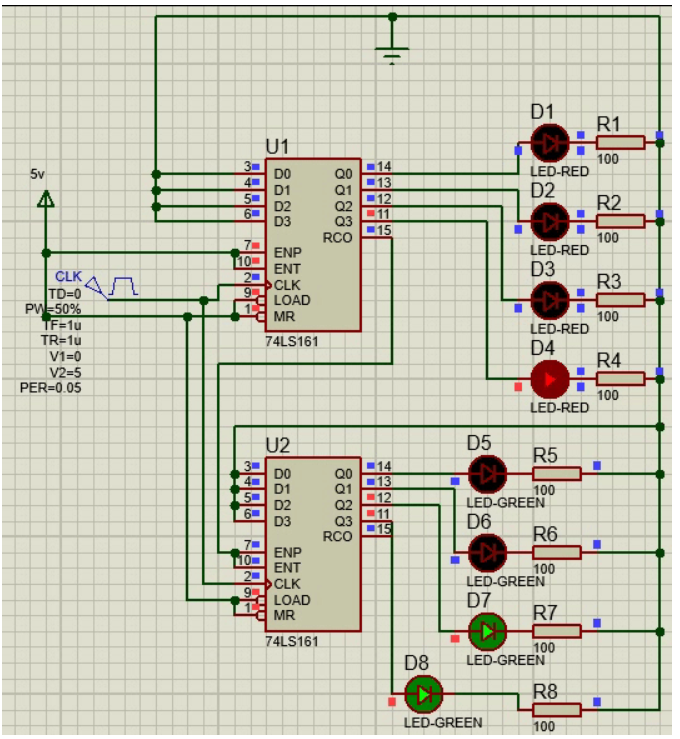

若需要的进制大于16,就需要多块74LS161来实现了。方法是将低位的进位端接入高位的EP、ET端(仿真图中为ENP和ENT)。芯片要共用CP时钟信号。这里放出32进制的仿真,若需要其他大于16进制的计数,参考上面反馈清零和反馈指置法。

两块74LS161实现32进制

我要赚赏金

我要赚赏金