-接下来,请您介绍一下驱动器源极引脚是如何降低开关损耗的。首先,能否请您对使用了驱动器源极引脚的电路及其工作进行说明?

Figure 4是具有驱动器源极引脚的MOSFET的驱动电路示例。它与以往驱动电路(Figure 2)之间的区别只在于驱动电路的返回线是连接到驱动器源极引脚这点。请看与您之前看到的Figure 2之间的比较。

从电路图中可以一目了然地看出,包括VG在内的驱动电路中不包含LSOURCE,因此完全不受开关工作时的ID变化带来的VLSOURCE的影响。

如果用公式来表示施加到内部芯片的电压VGS_INT的话,就是公式(2)。当然,计算公式中没有3引脚封装的公式(1)中存在的LSOURCE相关的项。所以,4引脚封装MOSFET的VGS_INT仅受RG_EXT和IG引起的电压降VRG_EXT的影响,而且由于RG_EXT是外置电阻,因此也可调。下面同时列出公式(1)用以比较。

-能给我们看一下比较数据吗?

这里有双脉冲测试的比较数据。这是为了将以往产品和具有驱动器源极引脚的SiC MOSFET的开关工作进行比较,而在Figure 5所示的电路条件下使Low Side(LS)的MOSFET开关的双脉冲测试结果。High Side(HS)是将RG_EXT连接于源极引脚或驱动器源极引脚,并仅使用体二极管换流工作的电路。

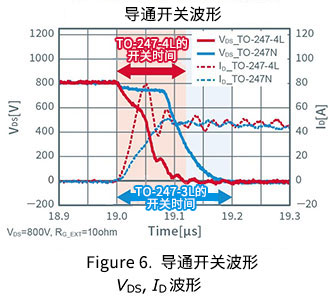

Figure 6是导通时的漏极-源极间电压VDS和漏极电流ID的波形。这是驱动条件为RG_EXT=10Ω、VDS=800V,ID约为50A时的波形。

红色曲线的TO-247-4L为4引脚封装,蓝色的TO-247N为以往的3引脚封装,其中的SiC MOSFET芯片是相同的。

我们先来比较一下虚线ID的波形。与蓝色的3引脚封装品的波形相比,红色的4引脚封装的ID上升更快,达到50A所需的时间当然也就更短。

虽然VDS的下降时间本身并没有很大的差别,但栅极信号输入后的开关速度明显变快。

-就像您前面说明的,区别只在于4引脚封装通过设置驱动器源极引脚,消除了LSOURCE的影响,因此它们的开关特性区别只在于LSOURCE的有无所带来的影响?可不可以这样理解?

基本上是这样。当然,也有一些应该详细查考的事项,但如果从栅极驱动电路中消除了LSOURCE的影响,则根据Figure 4中说明的原理,开关速度将变快。关于关断,虽然不像导通那样区别显著,但速度同样也会变快。

-这就意味着开关损耗得到了大幅改善。

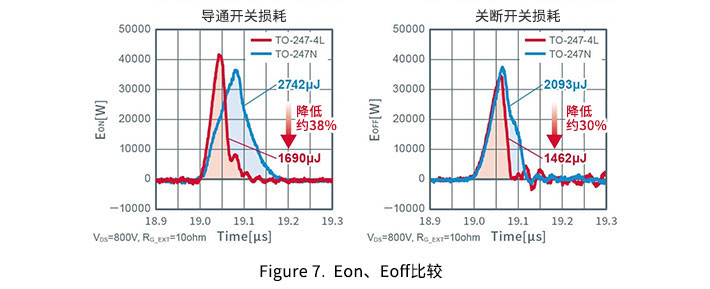

这里有导通和关断相关的开关损耗比较数据。

在导通数据中,原本2,742µJ的开关损耗变为1,690µJ,损耗减少了约38%。在关断数据中也从2,039µJ降至1,462µJ,损耗减少了约30%。

-明白了。最后请你总结一下,谢谢。

SiC MOSFET具有超低导通电阻和高速开关的特点,还具有可进一步缩小电路规模、提高相同尺寸的功率、以及因降低损耗而提高效率并减少发热量等诸多优点。

另一方面,关于在大功率开关电路中的功率元器件的安装,由于必须考虑寄生电感等寄生分量的影响,如果开关电流速度明显提高,那么其影响也会更大。这不仅仅是实装电路板级别的问题,同时也是元器件封装级别的课题。

此次之所以在最新一代SiC MOSFET中采用4引脚封装,也是基于这样的背景,旨在在使用了SiC功率元器件的应用中,进一步降低损耗。

这里有一个注意事项,或者说是为了有效使用4引脚封装产品而需要探讨的事项。前面提到了通过消除封装电感LSOURCE的影响可提高开关速度并大大改善开关损耗。这虽然是事实,但考虑到稳定性和整个电路工作时,伴随着开关速度的提高,也产生了一些需要探讨的问题。就像“权衡(Trade-off)”一词所表达的,电路的优先事项一定需要用最大公约数来实现优化。

对此,将在Tech Web的基础知识“SiC功率元器件”中进行解说。另外,您还可以通过ROHM官网下载并使用本次议题的基础,即Application Note“利用驱动器源极引脚改善开关损耗(PDF)”。

-感谢您的讲解。

我要赚赏金

我要赚赏金