在PCB设计过程中,有一项重要的任务是从发 射和抗扰度这两个角度去分辨哪些是关键信号。对于抗扰类,需要重点关注的信号有,时钟信号,高 dv/dt 或 高di/dt 信号,以及射频RF信号等。对于抗扰类,需关注的重点信号有,复位、中断和低电平模拟信号等。识别出这些信号后,请避免将它们靠近电路板边缘进行布线。

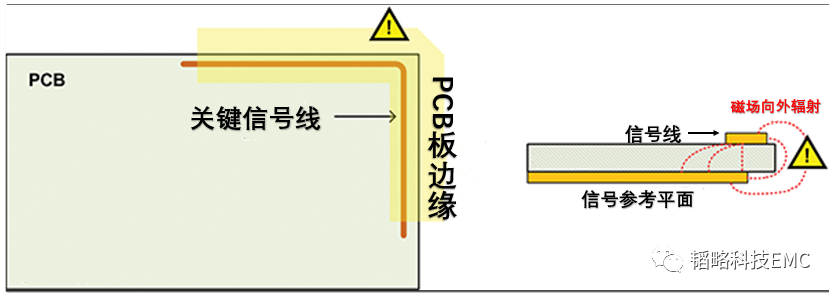

图 1给出了一个带有关键发 射信号的示例。信号走线路径靠近电路板右上角边缘,而电路板右上角边缘底下并无完整的参考平面。由于边缘效应,关键高速信号走线附近会产生拥有密集磁力线的磁场,产生的噪声磁场容易耦合到附近电路、外围连接线缆或接插件等。

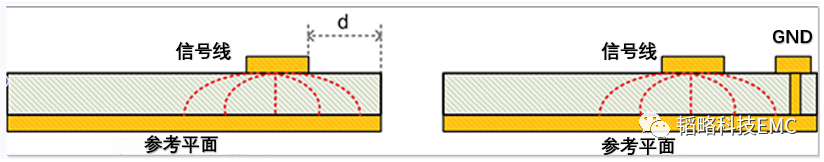

为了尽量减少这种影响,在空间有限且走线不能改动的前提下,有以下2个改善措施。如图 2所示。电路板边缘,走线底下铺设完整参考平面,并在顶层沿电路板边缘添加一条额外的地走线,同时将地走线用过孔连接到中间层的参考平面上。这样,磁力线会被包围在 PCB 内部,从而减少了边缘效应。

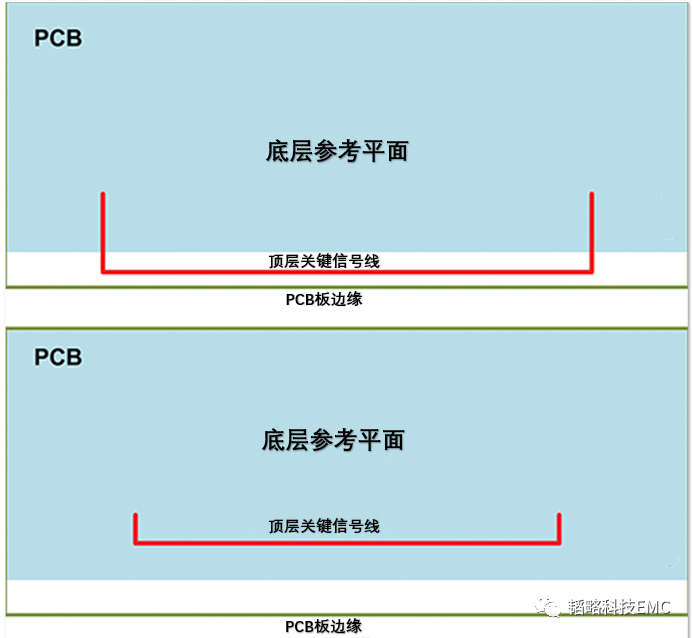

这里准备了个简单的实验来验证关键信号走线走在PCB板边缘的危害。如图 3 所示为两个双面板。

两个板情况如下:1) 信号走线靠近电路板边缘的底部且其下方没有完整的参考平面(上图),以及 2) 信号走线远离电路板边缘,且底下具有完整参考平面(下图)。

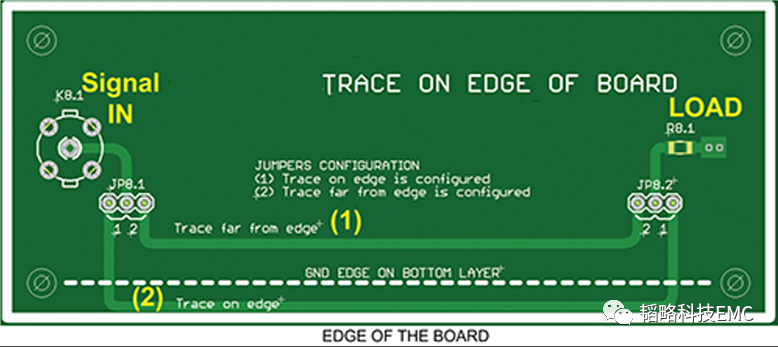

具体PCB如图 4 所示,其中我们的信号(数字时钟信号)通过 K8.1接口引入,负载端R8.1位置接50欧姆电阻。通过跳线切换JP8.1和JP8.2连接器来选择不同走线。

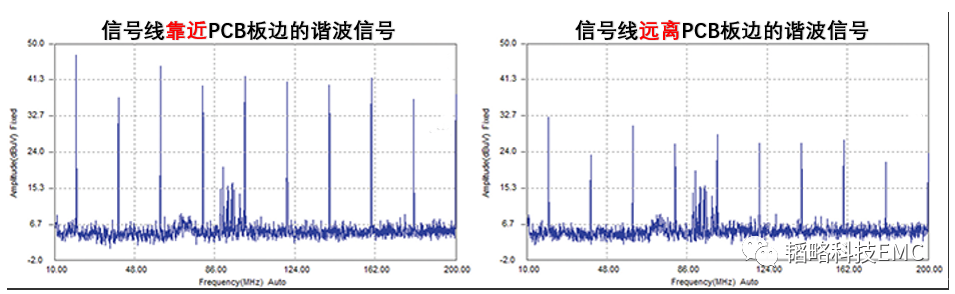

图 5 显示了通过频谱分析仪近场探头在 PCB 下方测量结果(测试数据在100MHz左右频段杂波为环境底噪)。通过下面对比数据,能直观地看出,信号走线靠近板边(左)比信号走线远离板边(右)的谐波噪声最多高出 20dB。

综上所述,各位工程师朋友们,在分析EMC问题时请将关键信号筛选出来,切勿将关键信号走线布置在靠近电路板边缘的位置。上述案例对比的是辐射发 射类情况,但抗扰类模型同样适用。

转载自网络,如有侵权,联系删除。

我要赚赏金

我要赚赏金